UNIVERSIDADE FEDERAL DA PARAÍBA

Larissa de Melo Soares

## **Análise de Defeitos na Perspectiva do Leiaute por meio de Extração de Elementos Parasitas**

**João Pessoa**

**2017**

UNIVERSIDADE FEDERAL DA PARAÍBA

Larissa de Melo Soares

**Análise de Defeitos na Perspectiva do Leiaute por meio

de Extração de Elementos Parasitas**

Dissertação apresentada ao Programa de Pós-Graduação em Engenharia Elétrica - PPGEE, da Universidade Federal da Paraíba - UFPB, como requisito para obtenção do título de Mestre em Engenharia Elétrica.

Orientador: Prof. Dr. Cleonilson Protásio de Souza

JOÃO PESSOA

2017

S323a Soares, Larissa de Melo

Análise de Defeitos na Perspectiva do Leiaute por meio de Extração de Elementos Parasitas / Larissa de Melo Soares. - JOÃO PESSOA, 2017.

100f. : il. (algumas color.)

Orientador: Prof. Dr. Cleonilson Protásio de Souza

Dissertação (Mestrado) - UFPB/CEAR

1. Engenharia Elétrica.

2. Engenharia de Testes.

3. Circuitos Integrados.

4. Defeito.

5. Leiaute.

6. Testes.

- I. Título II. Cleonilson Protásio de Souza.

UNIVERSIDADE FEDERAL DA PARAÍBA

Larissa de Melo Soares

## **Análise de Defeitos na Perspectiva do Leiaute por meio de Extração de Elementos Parasitas**

Dissertação apresentada ao Programa de Pós-Graduação em Engenharia Elétrica - PPGEE, da Universidade Federal da Paraíba - UFPB, como requisito para obtenção do título de Mestre em Engenharia Elétrica.

A Comissão Examinadora abaixo assinada, aprova a Dissertação de Mestrado

---

**Prof. Dr. Cleonilson Protásio de Souza**

Orientador - Presidente da Banca

---

**Prof. Dr. Antônio Carlos Cavalcanti**

Membro Externo

---

**Prof. Dr. Diomadson Rodrigues

Belfort**

Membro Externo

JOÃO PESSOA, 24 de fevereiro de 2017

# Dedicatória

*Este trabalho é dedicado aos meus pais, Mário Francisco Ferreira Soares e Soraya Alves de Melo Soares.*

# Agradecimentos

Agradeço primeiramente a Deus, à minha família que sempre me apoiou em todas as minhas decisões na vida acadêmica. Essas pessoas são minha mãe Soraya Alves de Melo Soares, que me deu todo suporte ao longo dessa jornada, ao meu pai Mário Francisco Ferreira Soares, que nunca me deixou desistir dos meus objetivos e ao meu sobrinho Arthur de Melo Paiva, que mesmo com pouca idade e sem perceber me deu o apoio mais sincero e gratuito que poderia receber. Aos membros da minha família que mesmo distantes me apoiam sempre como Paulo Lavedoque, Rita Ferreira, Kelsilene Melo (por ser minha segunda mãe), Alexandre Brasil, Talita Melo, Anderson Melo (pelo apoio incondicional à minha vida acadêmica), Rosilene Ribas, Júlia Melo, Paulo Alexander Melo (por ser um dos responsáveis da escolha em Engenharia Elétrica), Erika Barros e Heitor Melo.

Agradeço ao Professor Cleonilson Protásio de Souza pelos ensinamentos acadêmicos e que tornou possível a realização deste mestrado.

Agradeço aos amigos Ítalo, Rafael Ângelo, Rafael Duarte, Pamela (pela amizade e ajuda excepcional neste trabalho), Leonardo (por seus conselhos na pesquisa), Verônica, Victor, Ranieri, Lucas, Luan, Nathália, Larissa Aguiar, Andréa, Tathiana, Dallianny, Hugo, Bárbara e a todos os amigos que não me vem na memória mas que guardo na memória e agradeço sempre.

Agradeço à CAPES pelo fomento às minhas atividades de pesquisa.

E, por fim, agradeço à todos que direta ou indiretamente contribuíram para este trabalho.

# Resumo

Modelos de falhas clássicos, que representam defeitos físicos em circuitos integrados, já não satisfazem completamente os requisitos atuais para testes. Por isso, atualmente tem-se estudado modelos de falhas que sejam baseados no próprio leiaute do circuito integrado a ser testado, ao invés de se basear no diagrama lógico do circuito como é feito nos modelos clássicos. Modelos baseados em leiaute possibilitam verificar as áreas mais prováveis de acontecer uma falha em consequência de um defeito físico. Nesta dissertação é realizado um estudo dos principais modelos clássicos de falhas e dos modelos baseados na perspectiva do leiaute em que são explanados conceitos como: defeitos físicos, falhas, elementos parasitas, área crítica, nível de defeito e suas correlações. Posteriormente, é proposta uma modelagem de defeitos na perspectiva do leiaute e apresentado um método de extração de elementos parasitas do leiaute utilizando o CADENCE juntamente com as análises simulacionais e resultados obtidos. Ao final, será explicitado como elementos parasitas de leiaute são relacionados com as probabilidades de ocorrência de falhas devido ao projeto do leiaute. Também foram obtidos resultados satisfatórios com relação à mudanças do leiaute para minimizar os efeitos dos elementos parasitas no leiaute. Estes resultados serão mostrados através de um *heat map* que demonstrará as diferenças entre o leiaute modificado e o original.

**Palavras-chave:** testes de circuitos integrados, modelos de falhas clássicos, modelos de falhas na perspectiva do leiaute, *heat map*.

# Abstract

Classic fault models which represent physical faults on Integrated Circuits (IC) do not fulfill completely current requirements for tests. Therefore, studies are being made about fault models that are based on the IC's layout under test, instead of basing on the IC's logical diagram, which is the technique used on classic models. Models based on layouts make possible to verify the most probable areas to happen faults in consequence of a physical defect. In this dissertation, a study is made about the main classic fault models and the models based on the perspective of the layout where some concepts are defined, like: physical faults, faults, parasite elements, critical area, fault level and its correlations. After that, a fault modeling is proposed in the layout perspective and a method of extracting parasite elements of the layout is presented using CADENCE along simulational analysis and obtained results. By the end, it will be showed how parasite elements of the layout are related to the probability of fault occurrences due to the layout's project. Satisfactory results were also obtained with respect to the layout changes to minimize the effects of the parasitic elements in the layout. These results show through a heat map that will demonstrate how the differences between the modified and original layout.

**Keywords:** testing integrated circuits, classical fault models, fault models on layout perspective, heat map.

# Listas de ilustrações

|                                                                                                                                       |    |

|---------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 1.1 – Lei de Moore: A densidade de transistores dos circuitos integrados dobra a cada dois anos. . . . .                       | 14 |

| Figura 1.2 – Falha <i>Stuck-At</i> . . . . .                                                                                          | 15 |

| Figura 1.3 – Falha <i>Transition Delay</i> (GARCIA, 2001). . . . .                                                                    | 16 |

| Figura 1.4 – Defeitos extraídos de um leiaute. . . . .                                                                                | 18 |

| Figura 1.5 – Área Crítica. . . . .                                                                                                    | 18 |

| Figura 2.1 – Diferença entre <b>falha</b> e <b>defeito</b> . . . . .                                                                  | 22 |

| Figura 2.2 – Circuito com falhas, C1 <i>stuck-at-1</i> e C2 <i>stuck-at-0</i> (WU; LEE, 2014). .                                      | 23 |

| Figura 2.3 – Se <b>Caminho de propagação 1 &gt; Caminho de propagação 2</b> , o efeito da falha na NAND da saída seria 0-1-0. . . . . | 24 |

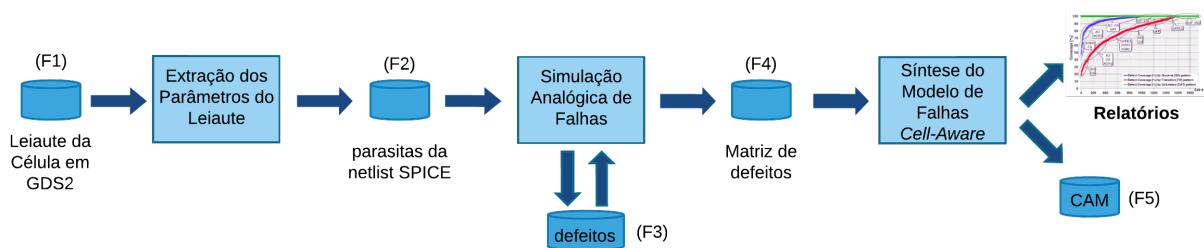

| Figura 3.1 – Etapas do <i>Cell-Aware</i> . . . . .                                                                                    | 25 |

| Figura 3.2 – Leiaute da célula de um multiplexador. . . . .                                                                           | 26 |

| Figura 3.3 – Leiaute da célula do multiplexador MUX31X4. . . . .                                                                      | 27 |

| Figura 3.4 – Transistores extraídos da netlist. . . . .                                                                               | 29 |

| Figura 3.5 – Ambiente de simulação analógica. . . . .                                                                                 | 29 |

| Figura 3.6 – Processo do ATPG normal. . . . .                                                                                         | 30 |

| Figura 3.7 – TPG para uma falha em ponte interna à célula. . . . .                                                                    | 30 |

| Figura 3.8 – Cobertura de defeitos do CAT em comparação com <i>Stuck-At</i> e <i>Transition Delay</i> . . . . .                       | 32 |

| Figura 4.1 – Função da Área Crítica (BUBEL et al., 1995a). . . . .                                                                    | 33 |

| Figura 4.2 – Método de expansão de polígonos para defeitos convexos arbitrários (ALLAN; WALTON, 1997a). . . . .                       | 34 |

| Figura 4.3 – Dinâmica do algoritmo que computa a Área Crítica (BUBEL et al., 1995a). . . . .                                          | 35 |

| Figura 4.4 – Material Extra (ALLAN; WALTON, 1998). . . . .                                                                            | 35 |

| Figura 4.5 – Material Perdido (ALLAN; WALTON, 1998). . . . .                                                                          | 36 |

| Figura 5.1 – Distribuição de probabilidade para o tamanho do defeito . . . . .                                                        | 38 |

| Figura 5.2 – <i>Wafer</i> contendo 648 chips. . . . .                                                                                 | 39 |

| Figura 5.3 – Área Crítica para um defeito de diâmetro $x$ . . . . .                                                                   | 40 |

| Figura 6.1 – Fabricação CMOS: Primeiras etapas. . . . .                                                                               | 45 |

| Figura 6.2 – Fabricação CMOS: Criação do <i>n-well</i> e Crescimento de óxido de campo. .                                             | 46 |

| Figura 6.3 – Fabricação CMOS: Máscaras. . . . .                                                                                       | 46 |

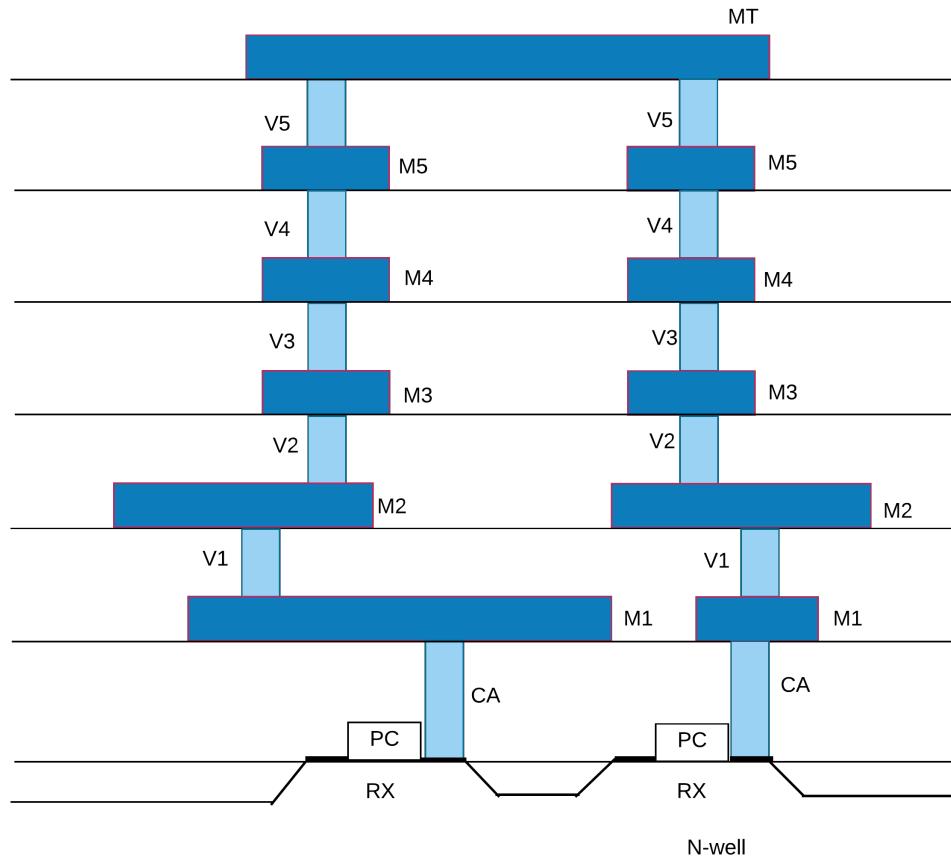

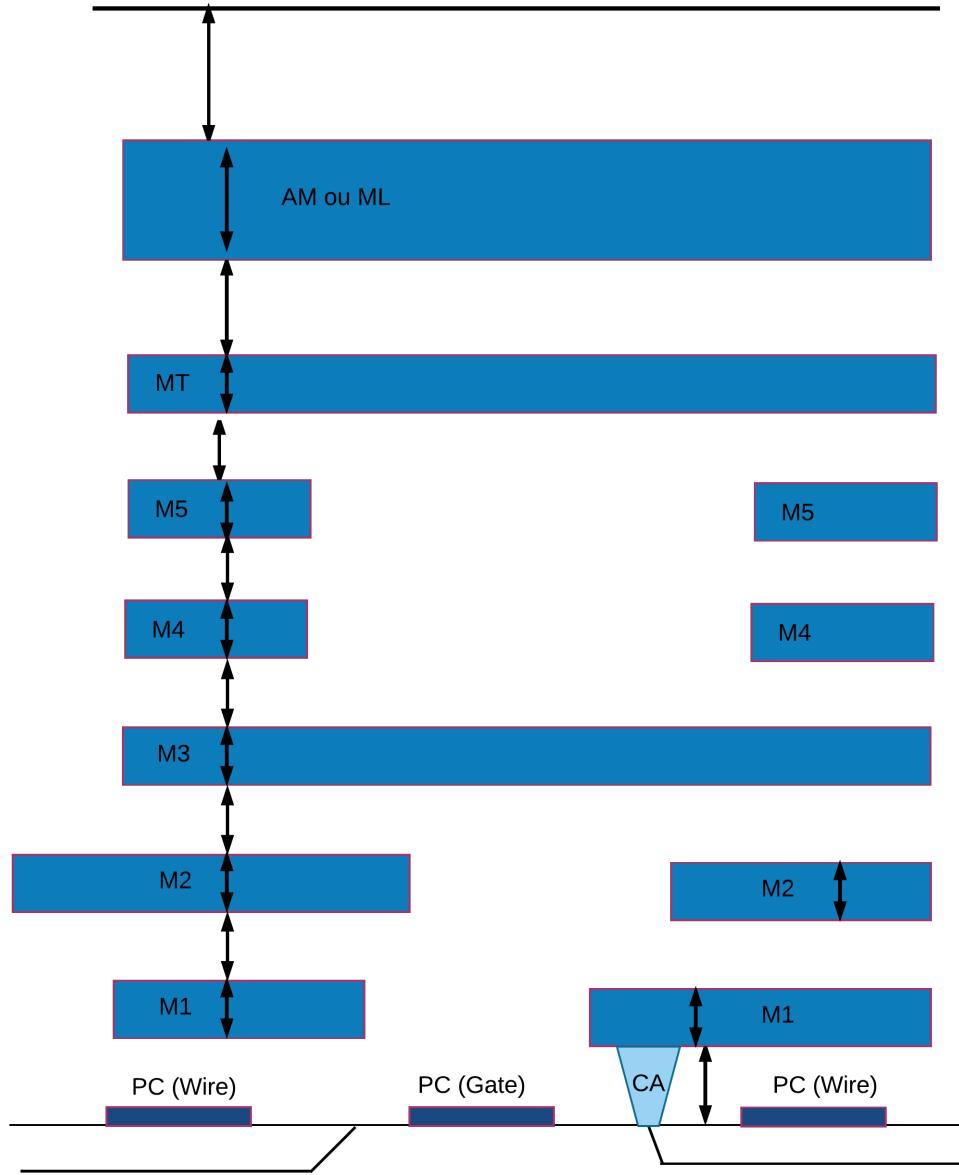

| Figura 6.4 – Camadas de metal e vias (ou contatos). . . . .                                                                           | 47 |

| Figura 6.5 – Camadas de metal e vias (ou contatos). . . . .                                                                           | 48 |

| Figura 6.6 – Visão lateral das camadas de metais. . . . .                                                                             | 48 |

| Figura 6.7 – Visão lateral das camadas de metais. . . . .                                                                             | 49 |

|                                                                                                                            |    |

|----------------------------------------------------------------------------------------------------------------------------|----|

| Figura 6.8 – Capacitâncias Parasitas (visão lateral). . . . .                                                              | 50 |

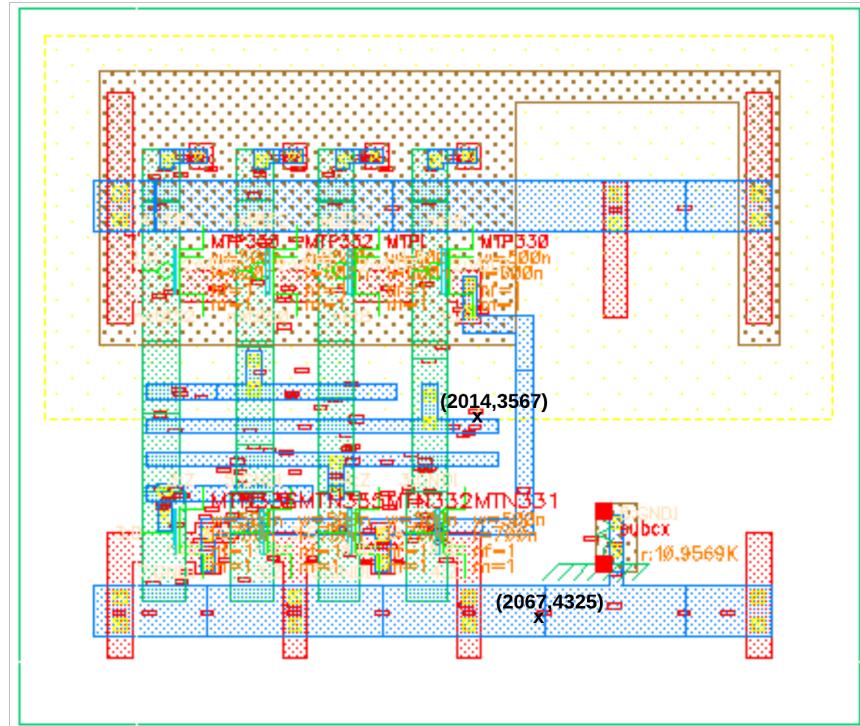

| Figura 6.9 – Modos de Extração de Capacitâncias no Assura RCX. . . . .                                                     | 51 |

| Figura 6.10–Diferença entre falha e defeito em nível de leiaute. . . . .                                                   | 51 |

| Figura 6.11–Distâncias entre nets <i>versus</i> Probabilidade de defeitos devido às capaci-<br>tâncias parasitas. . . . .  | 52 |

| Figura 7.1 – Fluxograma da Extração dos Elementos Parasitas. . . . .                                                       | 54 |

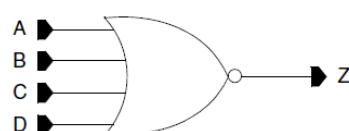

| Figura 7.2 – Porta lógica da célula <i>NOR4_A_5V</i> . . . . .                                                             | 54 |

| Figura 7.3 – Leiaute da célula <i>NOR4_A_5V</i> . . . . .                                                                  | 55 |

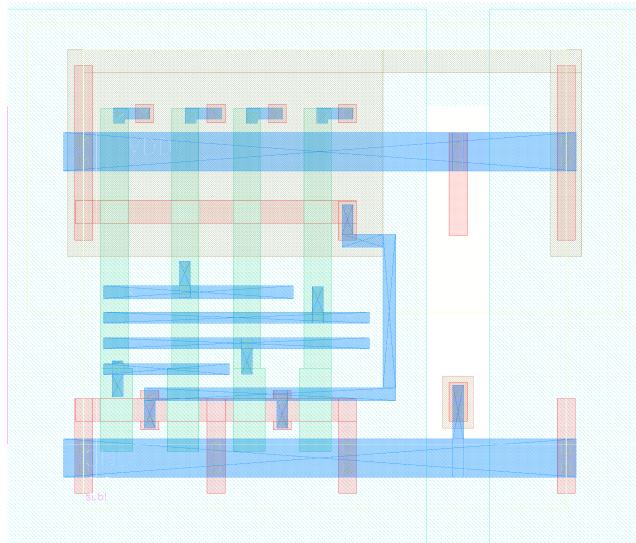

| Figura 7.4 – Análise DRC. . . . .                                                                                          | 55 |

| Figura 7.5 – Análise LVS (CDL). . . . .                                                                                    | 56 |

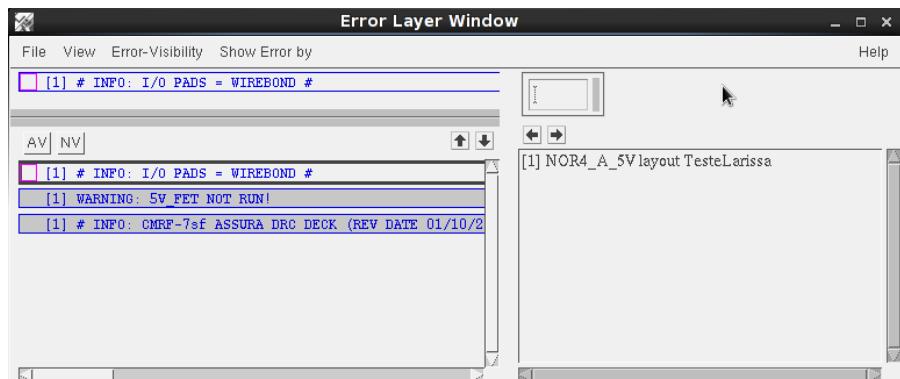

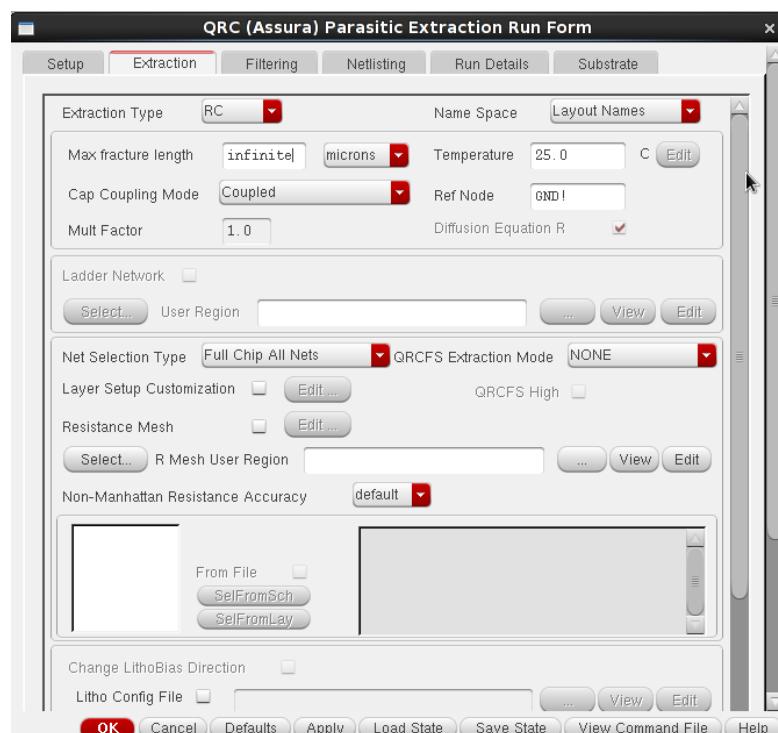

| Figura 7.6 – QRC Assura <i>Setup</i> . . . . .                                                                             | 57 |

| Figura 7.7 – QRC Assura <i>Extraction</i> . . . . .                                                                        | 57 |

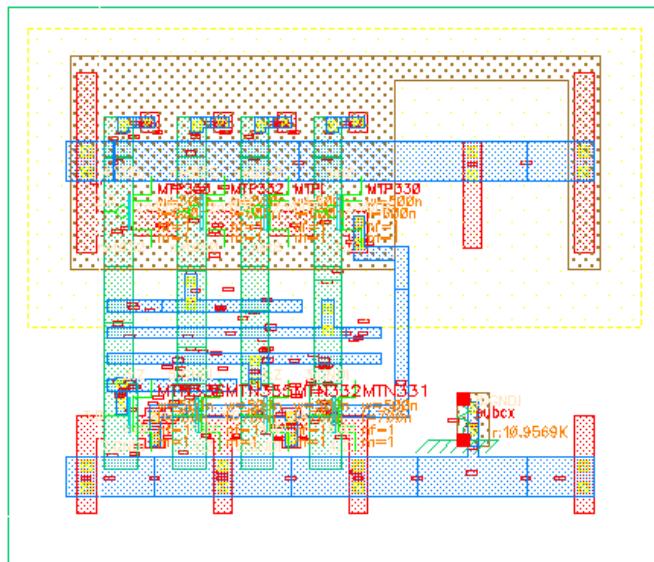

| Figura 7.8 – Extração de elementos parasitas da célula <i>NOR4_A_5V</i> . . . . .                                          | 58 |

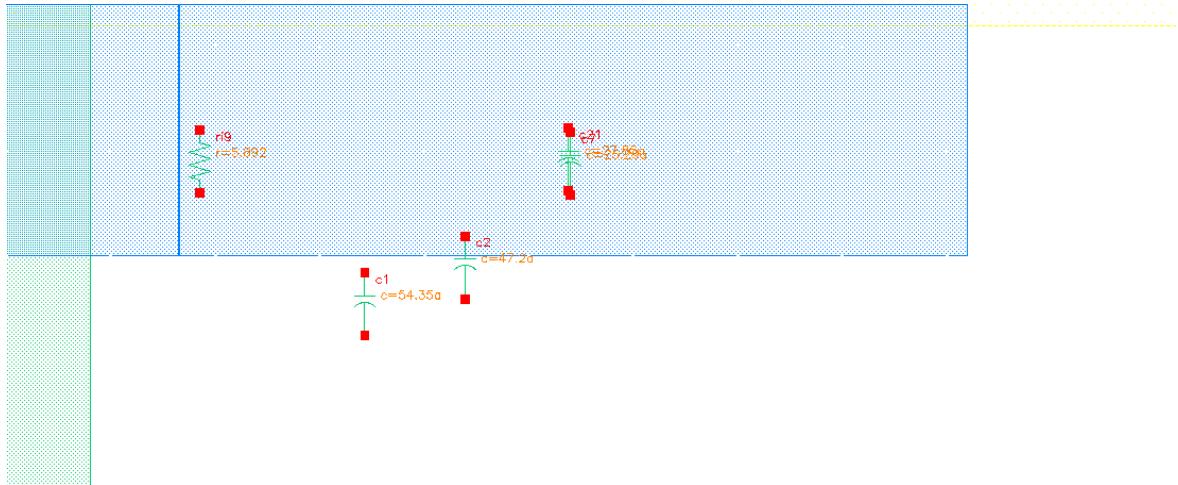

| Figura 7.9 – Elementos parasitas: capacitâncias . . . . .                                                                  | 58 |

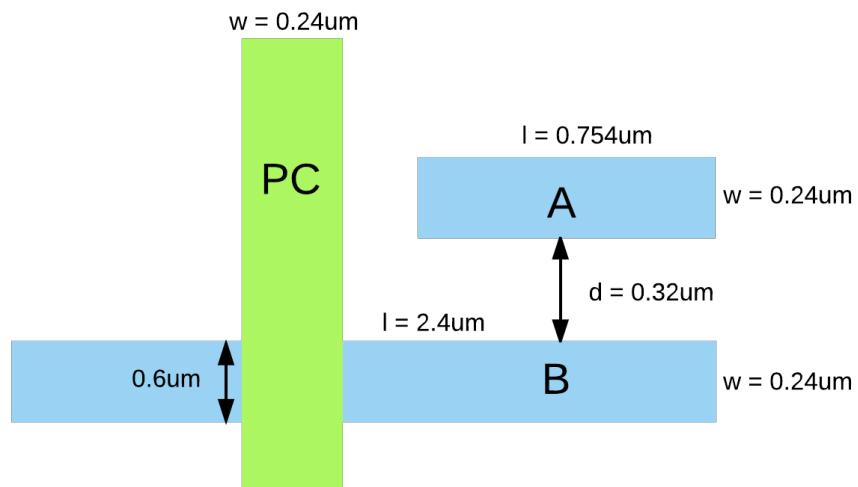

| Figura 7.10–Zoom nas capacitâncias entre as nets A e B. . . . .                                                            | 59 |

| Figura 7.11–Visão do topo das nets selecionadas. . . . .                                                                   | 59 |

| Figura 7.12–Visão frontal das nets selecionadas. . . . .                                                                   | 60 |

| Figura 7.13–Visão lateral das nets selecionadas. . . . .                                                                   | 61 |

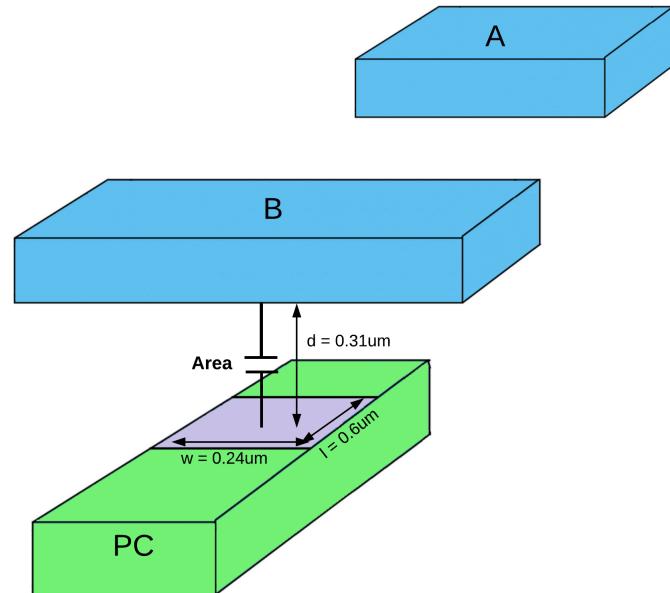

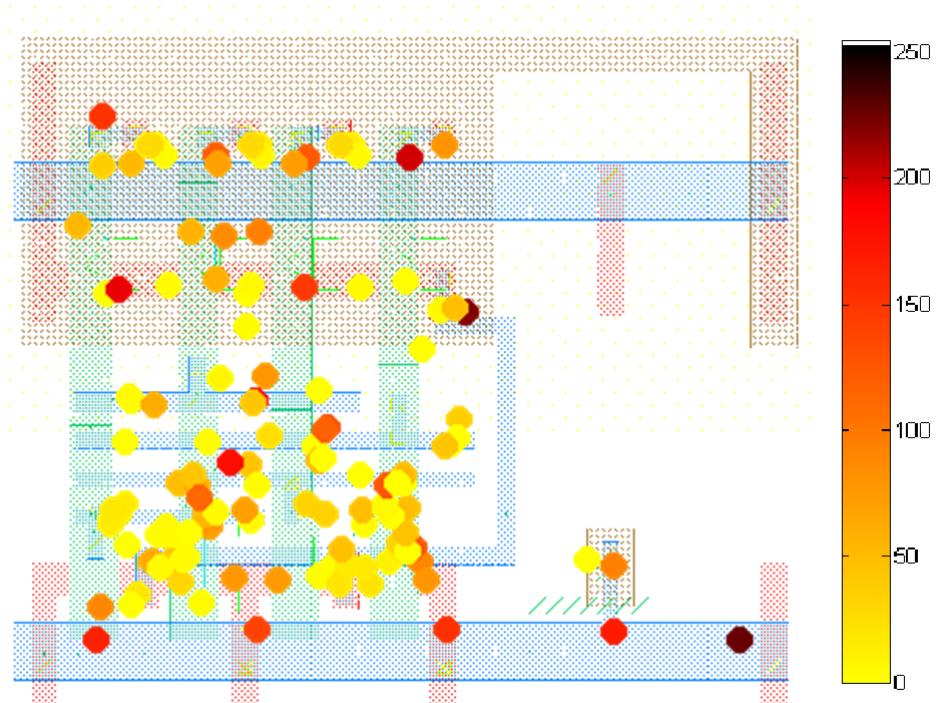

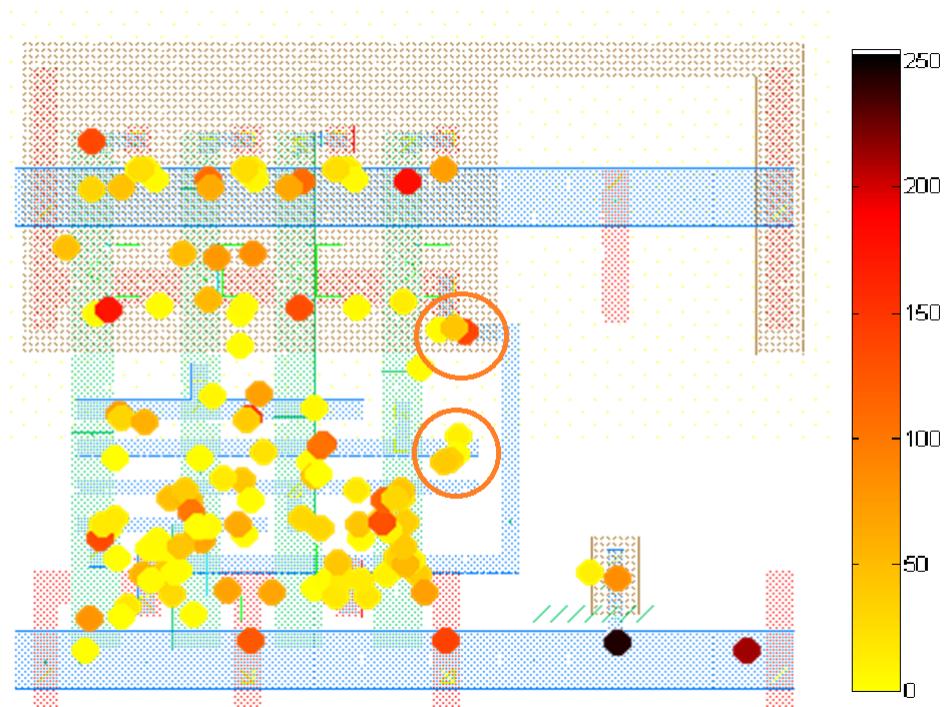

| Figura 8.1 – Programa no MATLAB para <i>Heat Map</i> de um leiaute. . . . .                                                | 63 |

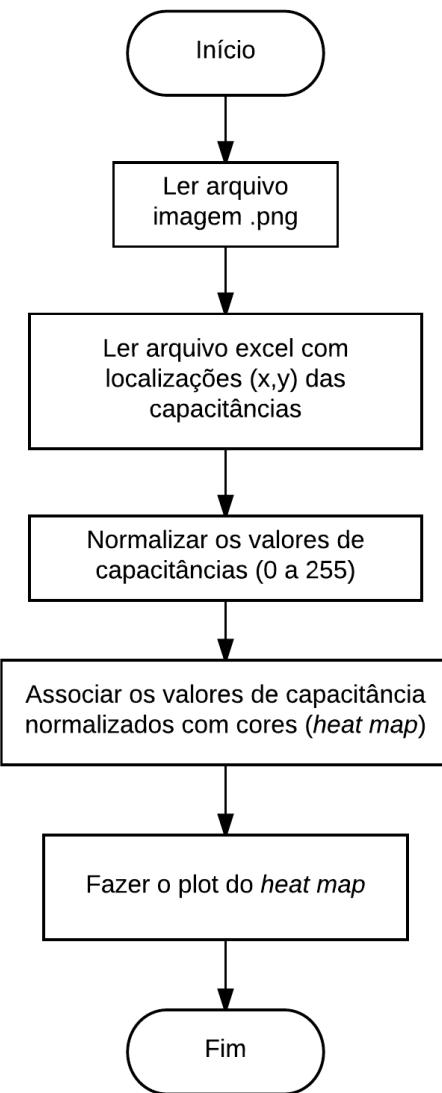

| Figura 8.2 – Leiaute com elementos parasitas e localizações. . . . .                                                       | 64 |

| Figura 8.3 – Leiaute da Célula <i>NOR4_A_5V</i> Original. . . . .                                                          | 64 |

| Figura 8.4 – Leiaute da Célula <i>NOR4_A_5V</i> Modificado. . . . .                                                        | 65 |

| Figura 8.5 – <i>Heat Map</i> com Célula <i>NOR4_A_5V</i> Original. . . . .                                                 | 66 |

| Figura 8.6 – <i>Heat Map</i> com Leiaute da Célula <i>NOR4_A_5V</i> Modificado. . . . .                                    | 66 |

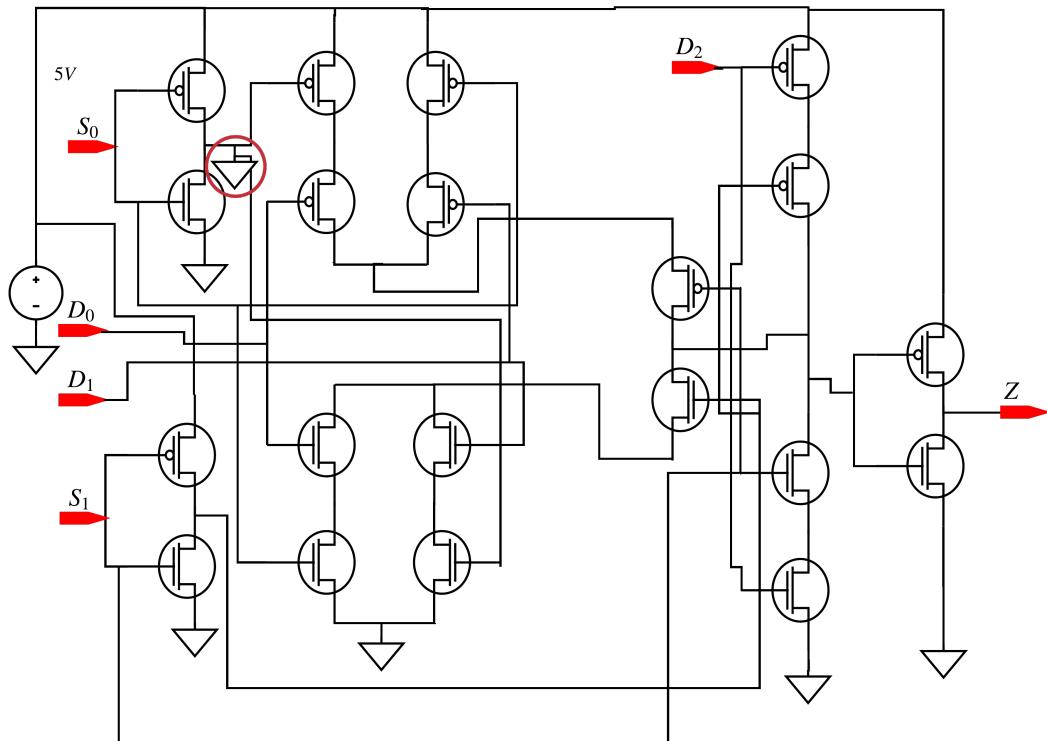

| Figura 9.1 – Multiplexador usado como exemplo dado pelo Hapke e implementado<br>no CADENCE <b>com defeito d1</b> . . . . . | 68 |

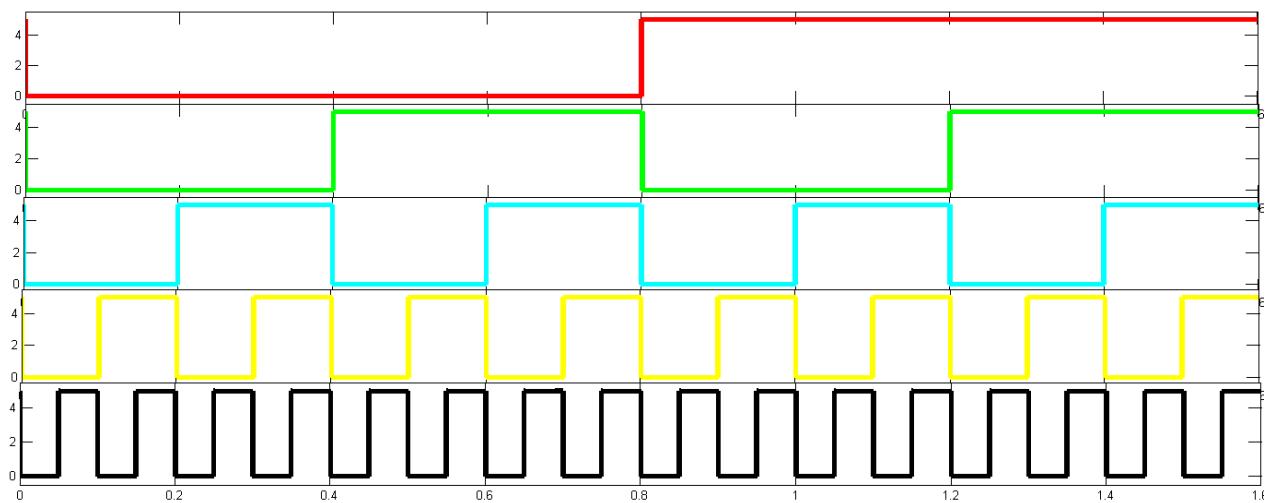

| Figura 9.2 – 32 possíveis entradas em $160\mu s$ . . . . .                                                                 | 68 |

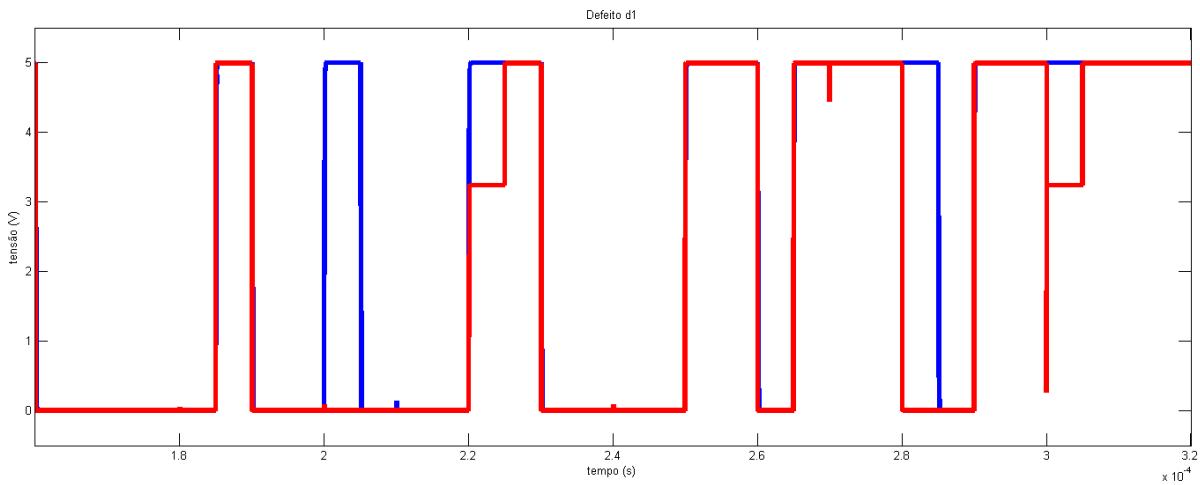

| Figura 9.3 – Resultado da simulação analógica com defeito <b>d1</b> (S0N, gnd). . . . .                                    | 69 |

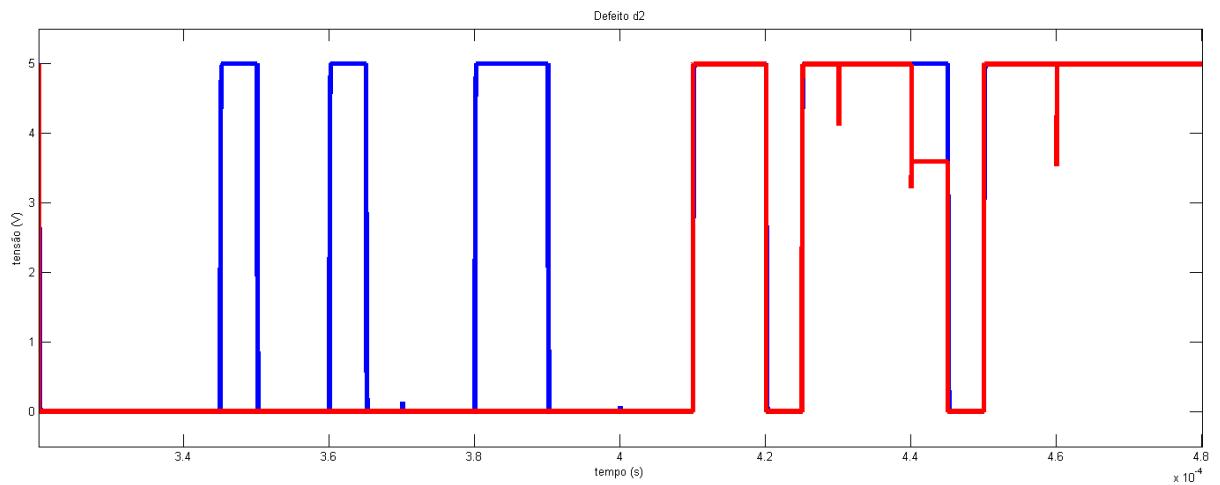

| Figura A.1–Resultado da simulação analógica com o defeito <b>d2</b> . . . . .                                              | 76 |

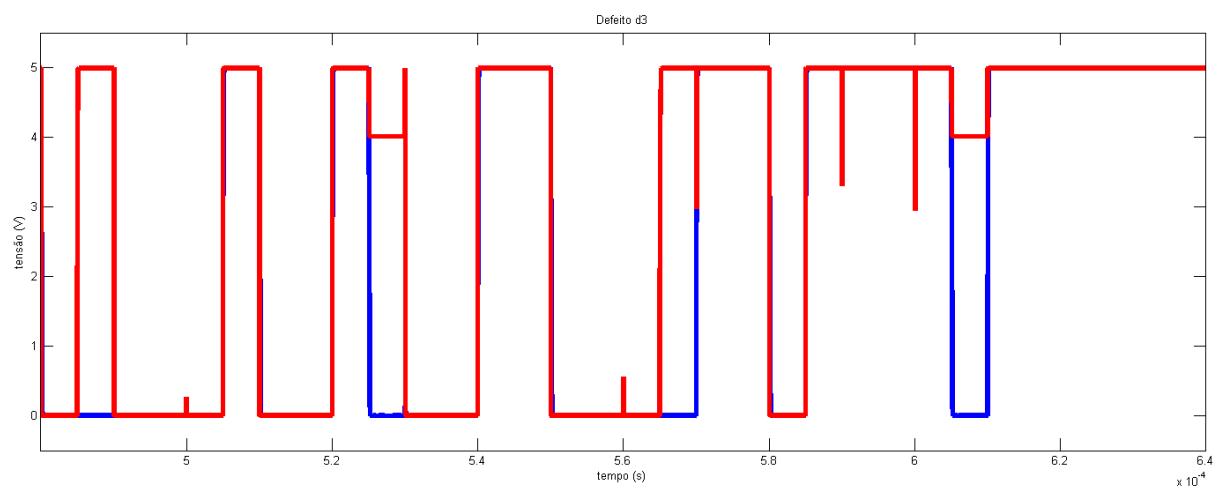

| Figura A.2–Resultado da simulação analógica com o defeito <b>d3</b> . . . . .                                              | 76 |

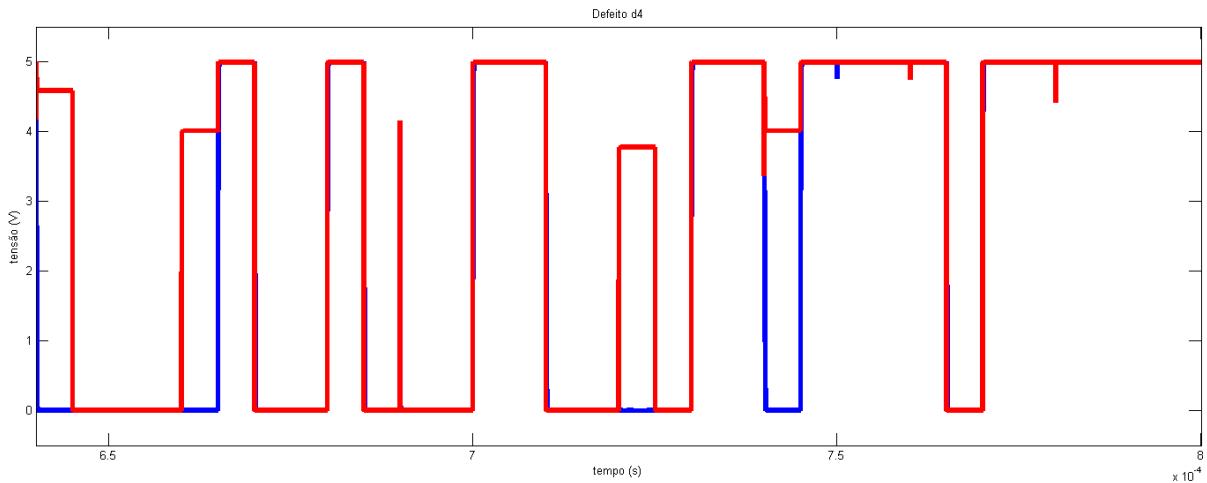

| Figura A.3–Resultado da simulação analógica com o defeito <b>d4</b> . . . . .                                              | 77 |

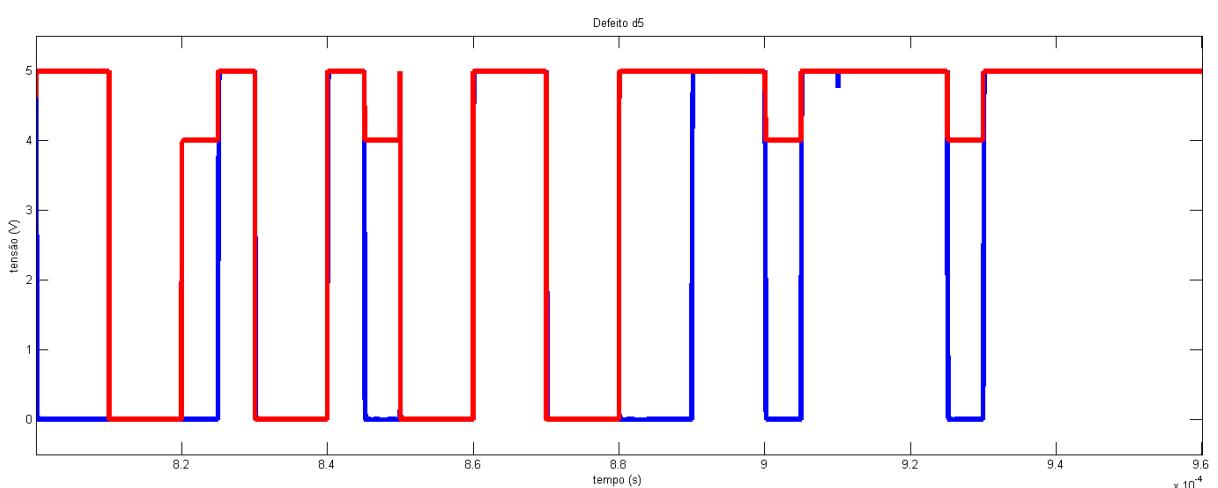

| Figura A.4–Resultado da simulação analógica com o defeito <b>d5</b> . . . . .                                              | 77 |

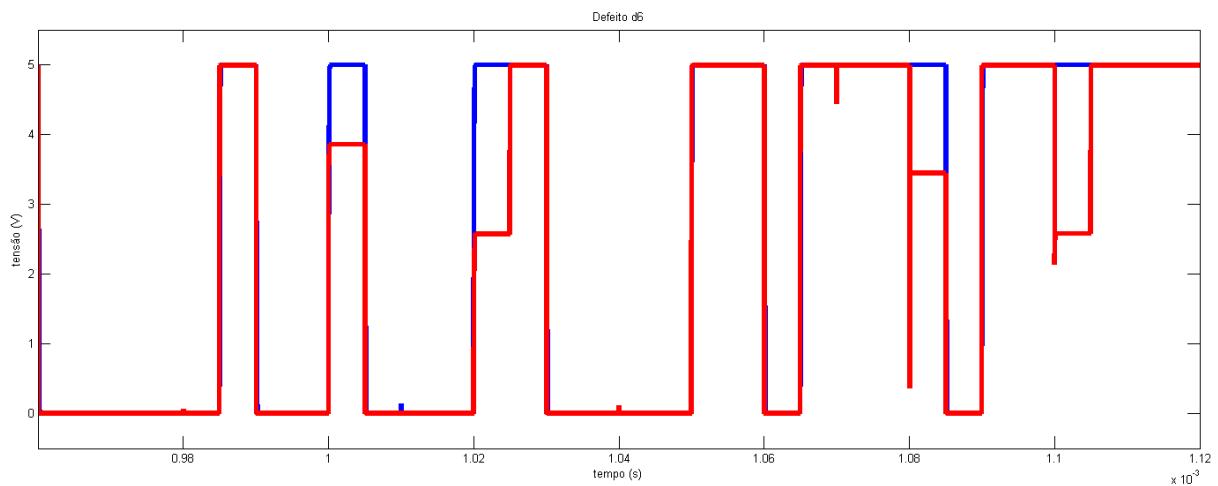

| Figura A.5–Resultado da simulação analógica com o defeito <b>d6</b> . . . . .                                              | 78 |

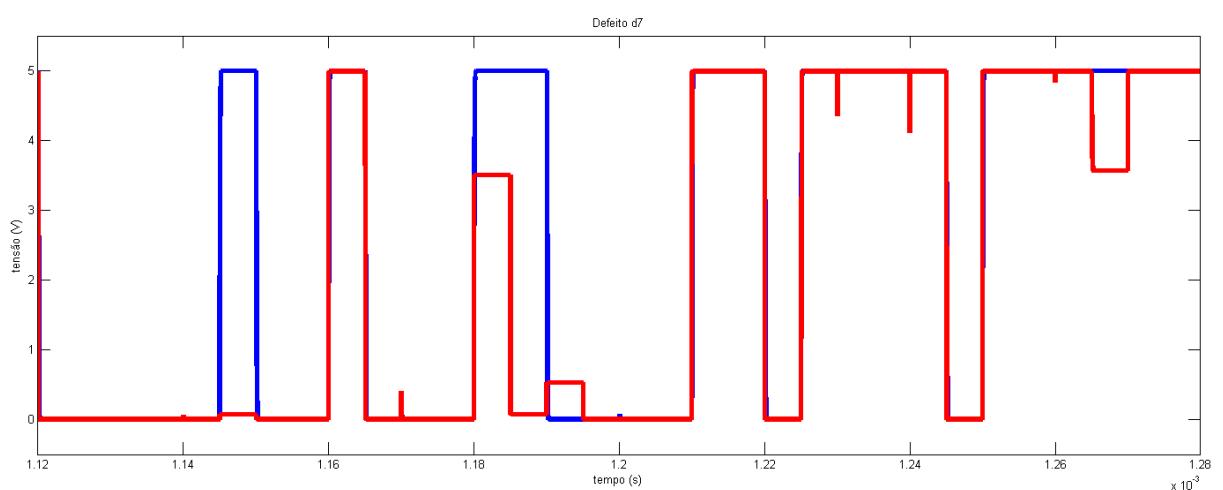

| Figura A.6–Resultado da simulação analógica com o defeito <b>d7</b> . . . . .                                              | 78 |

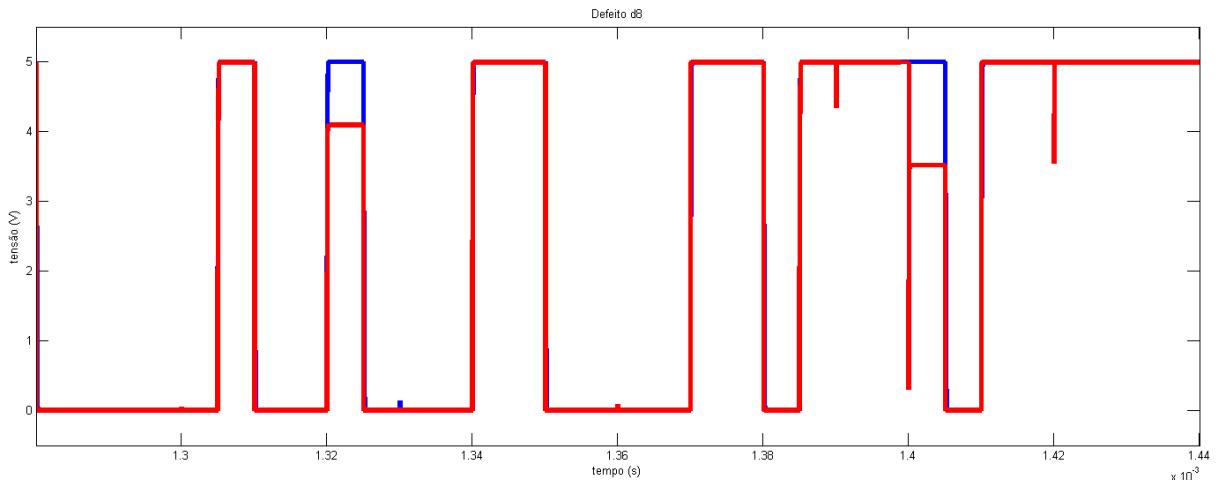

| Figura A.7–Resultado da simulação analógica com o defeito <b>d8</b> . . . . .                                              | 79 |

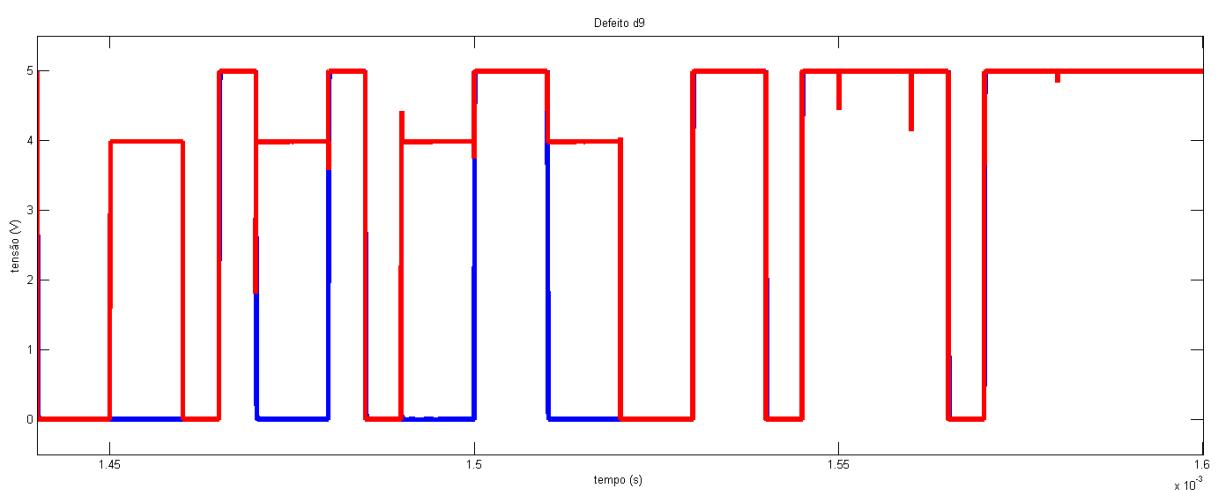

| Figura A.8–Resultado da simulação analógica com o defeito <b>d9</b> . . . . .                                              | 79 |

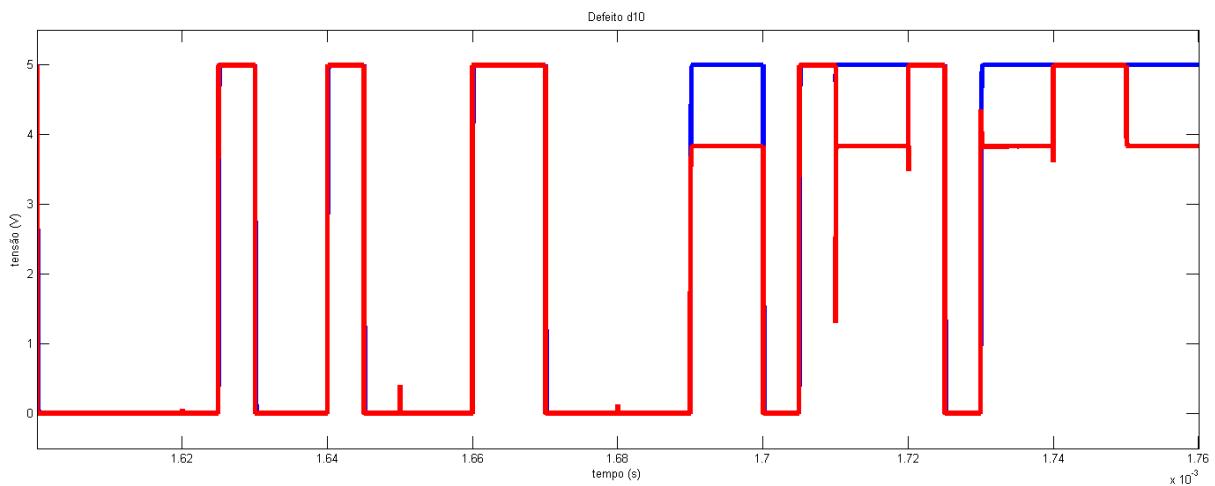

| Figura A.9–Resultado da simulação analógica com o defeito <b>d10</b> . . . . .                                             | 80 |

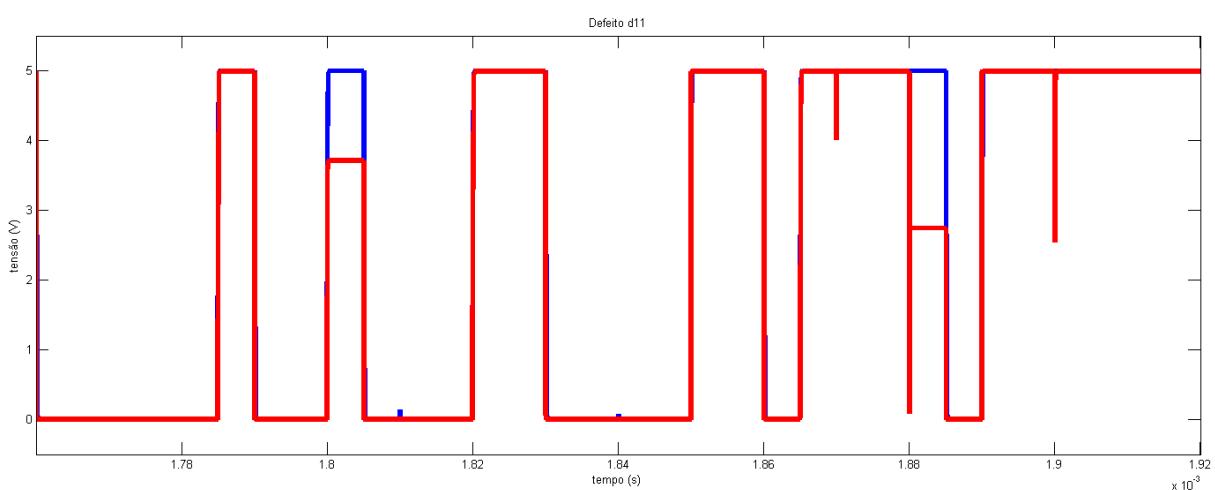

| Figura A.10–Resultado da simulação analógica com o defeito <b>d11</b> . . . . .                                            | 80 |

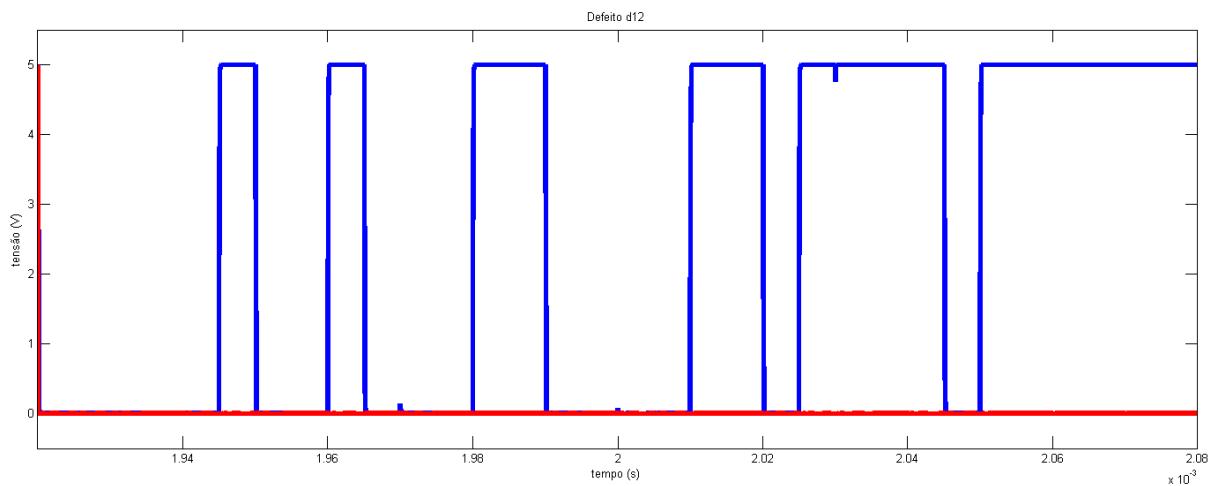

| Figura A.11–Resultado da simulação analógica com o defeito <b>d12</b> . . . . .                                            | 81 |

|                                                                       |     |

|-----------------------------------------------------------------------|-----|

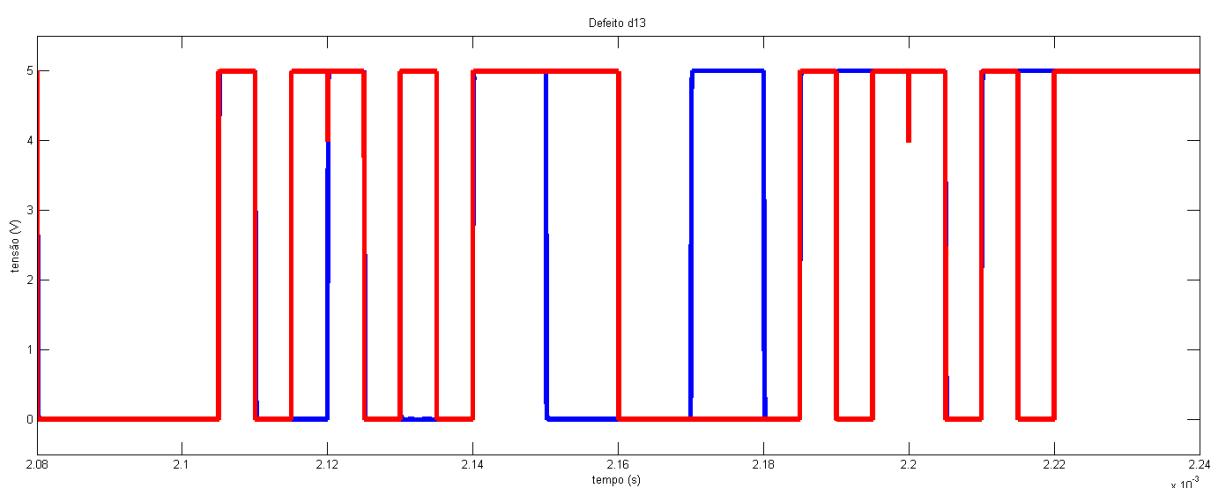

| Figura A.12–Resultado da simulação analógica com o defeito <b>d13</b> | 81  |

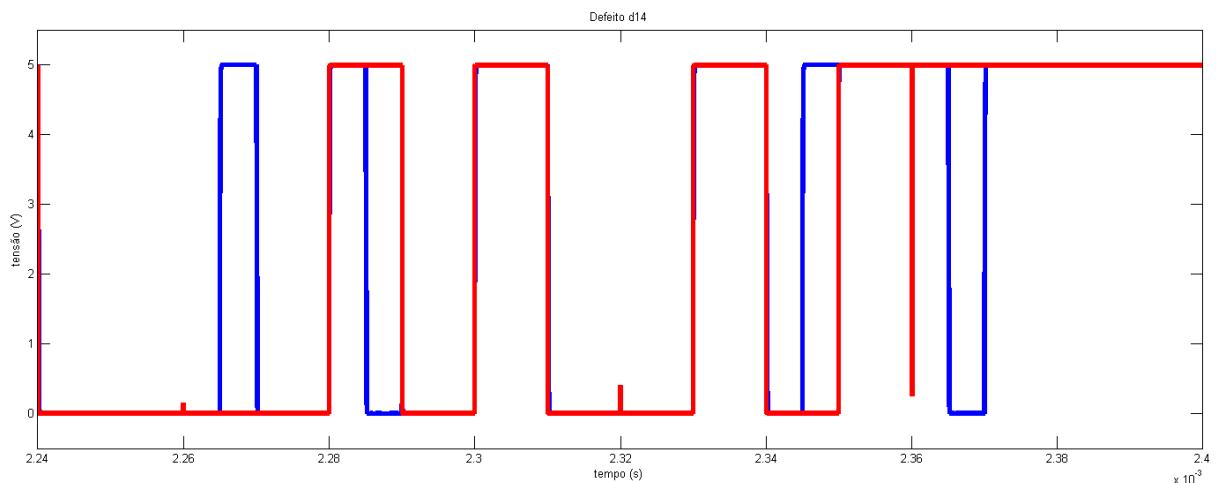

| Figura A.13–Resultado da simulação analógica com o defeito <b>d14</b> | 82  |

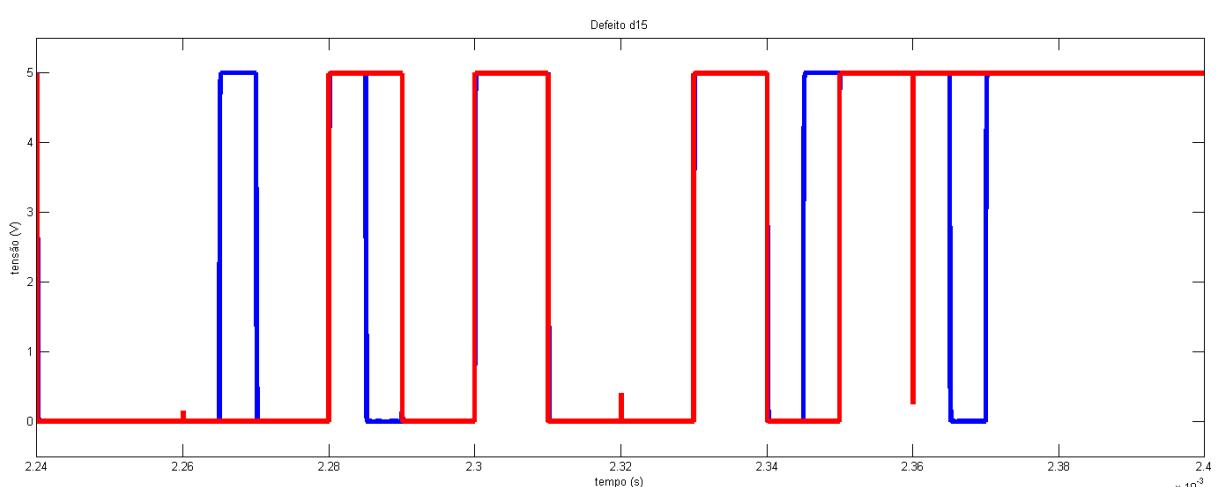

| Figura A.14–Resultado da simulação analógica com o defeito <b>d15</b> | 82  |

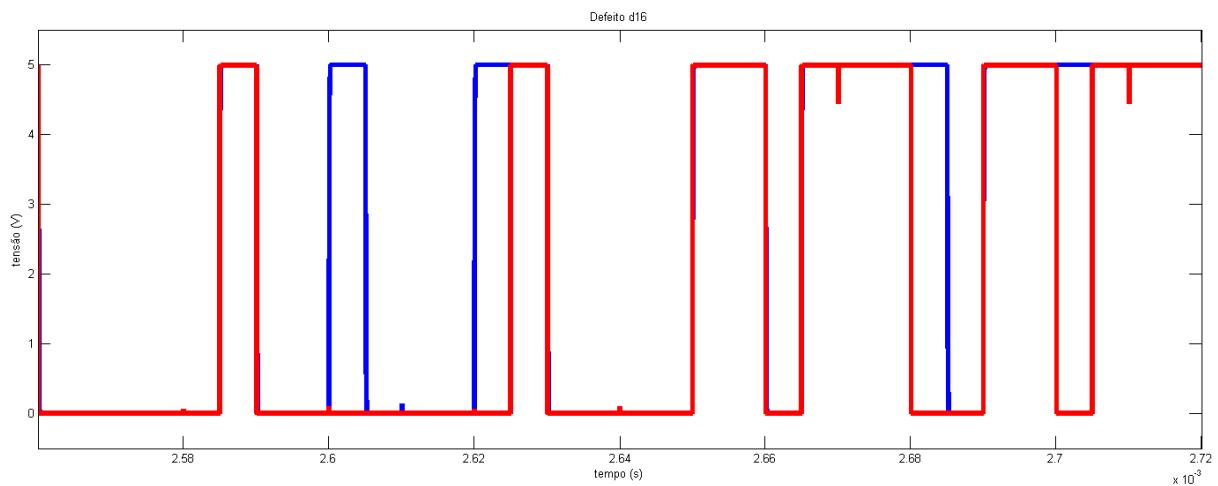

| Figura A.15–Resultado da simulação analógica com o defeito <b>d16</b> | 83  |

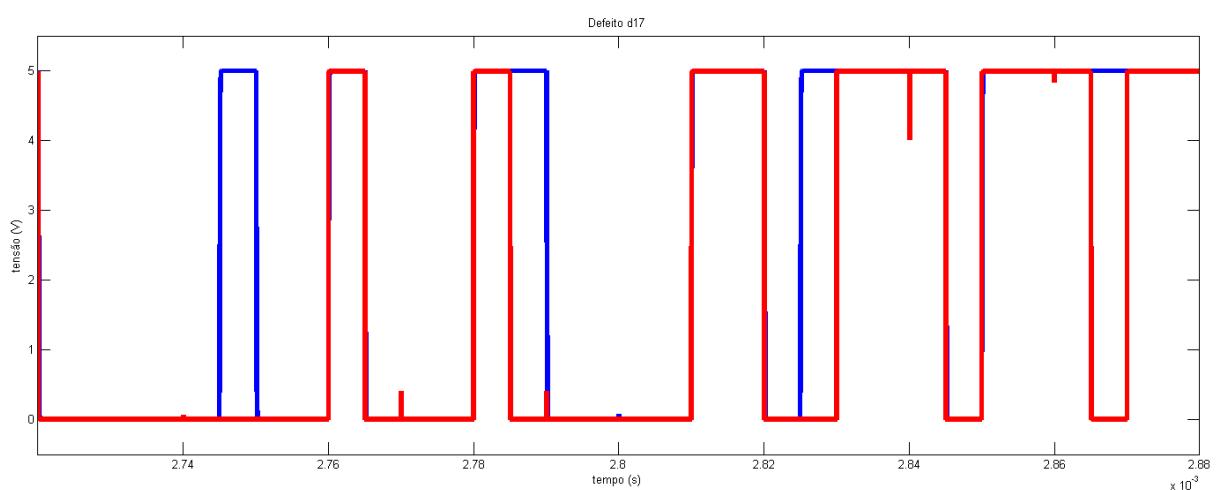

| Figura A.16–Resultado da simulação analógica com o defeito <b>d17</b> | 83  |

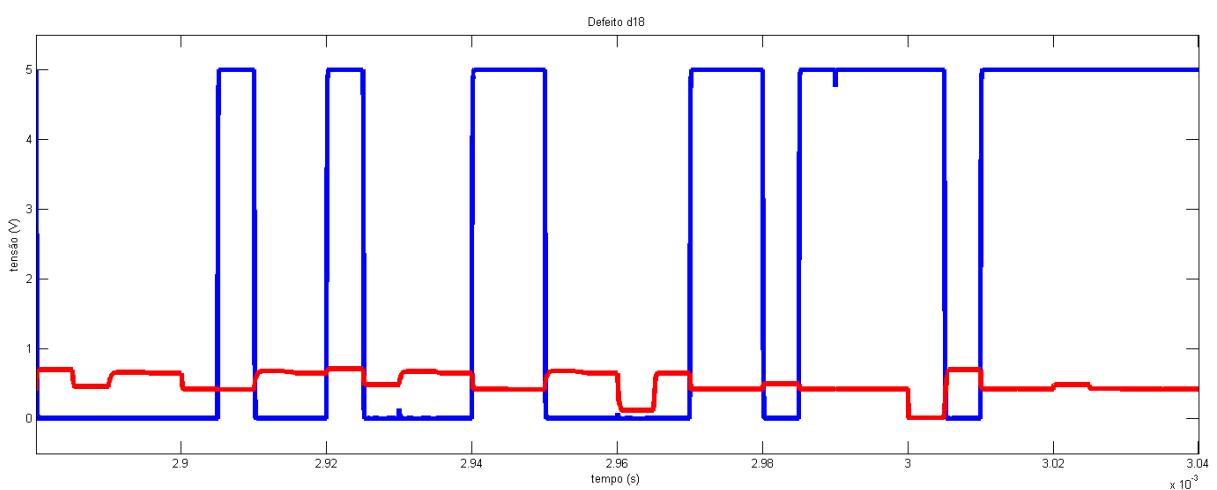

| Figura A.17–Resultado da simulação analógica com o defeito <b>d18</b> | 84  |

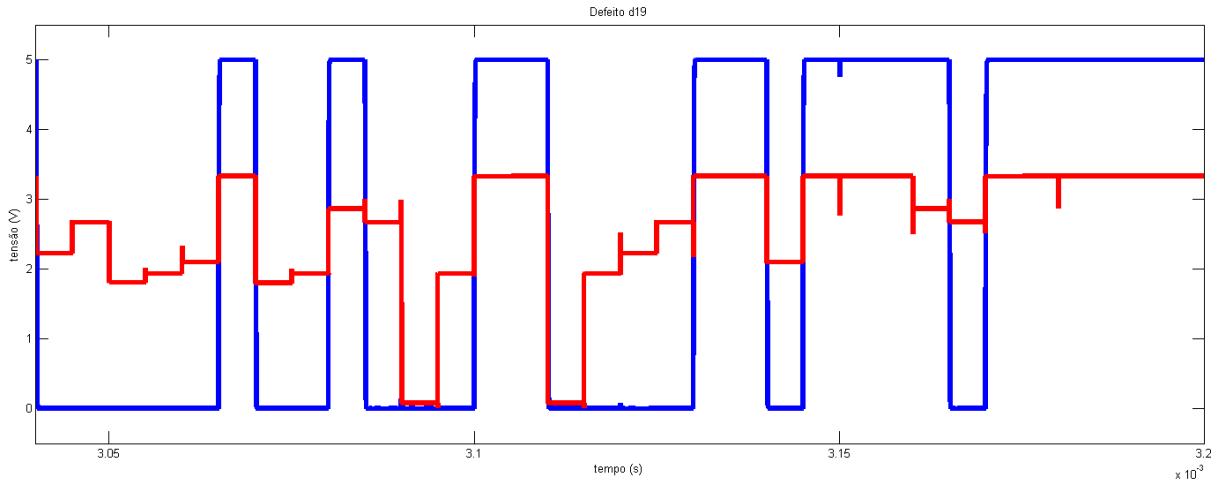

| Figura A.18–Resultado da simulação analógica com o defeito <b>d19</b> | 85  |

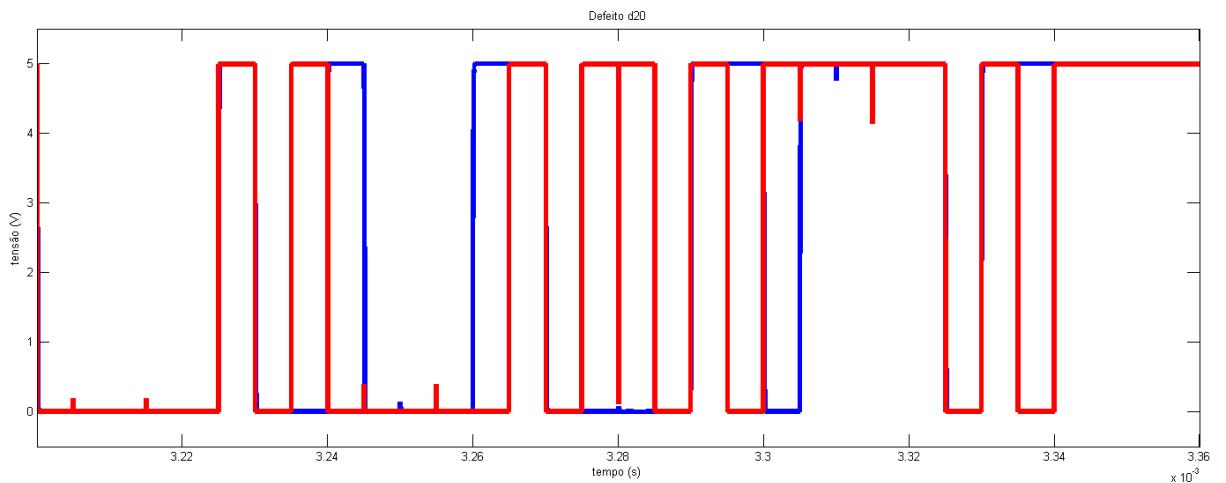

| Figura A.19–Resultado da simulação analógica com o defeito <b>d20</b> | 85  |

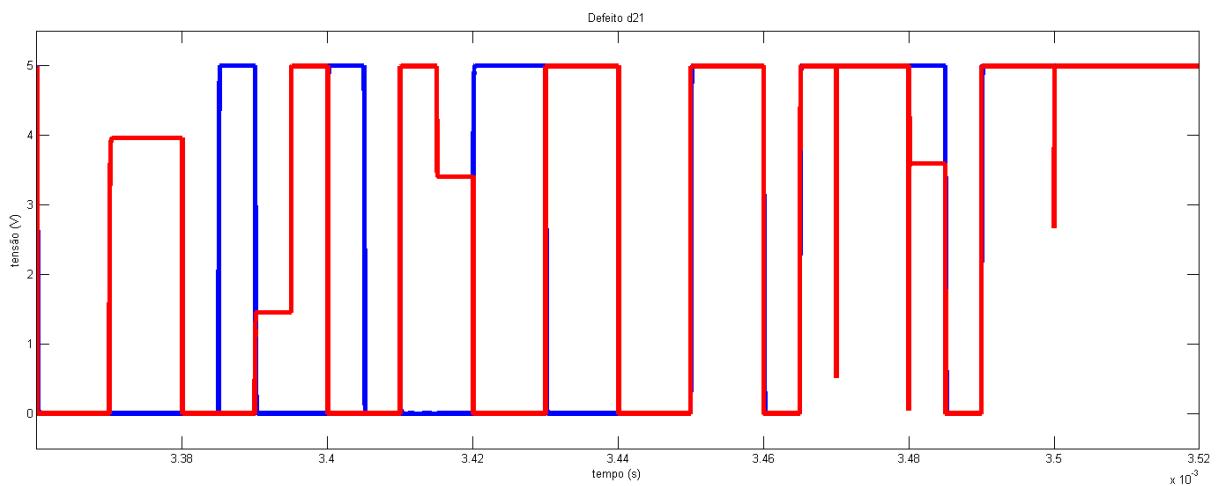

| Figura A.20–Resultado da simulação analógica com o defeito <b>d21</b> | 86  |

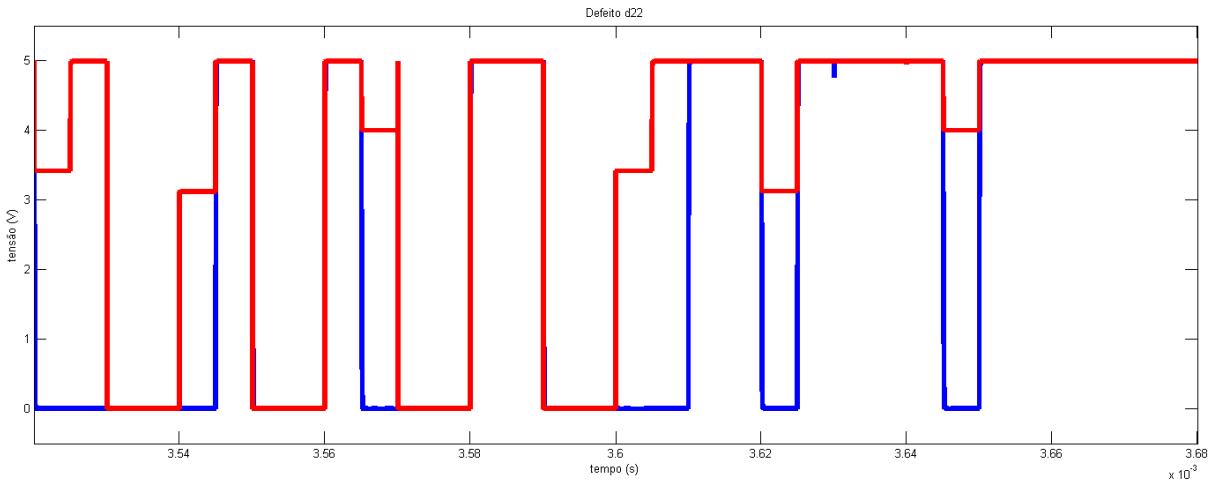

| Figura A.21–Resultado da simulação analógica com o defeito <b>d22</b> | 87  |

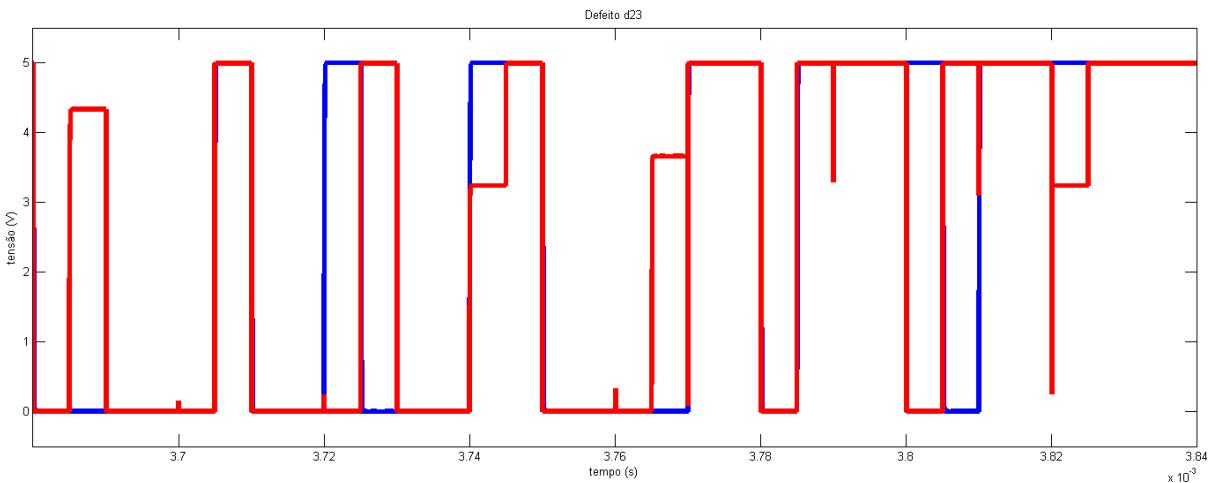

| Figura A.22–Resultado da simulação analógica com o defeito <b>d23</b> | 87  |

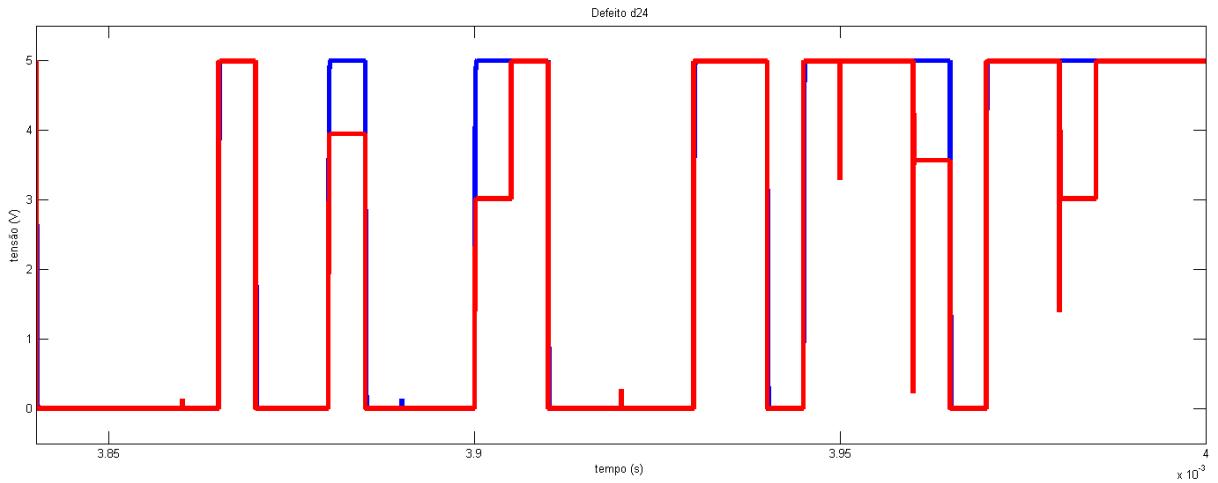

| Figura A.23–Resultado da simulação analógica com o defeito <b>d24</b> | 88  |

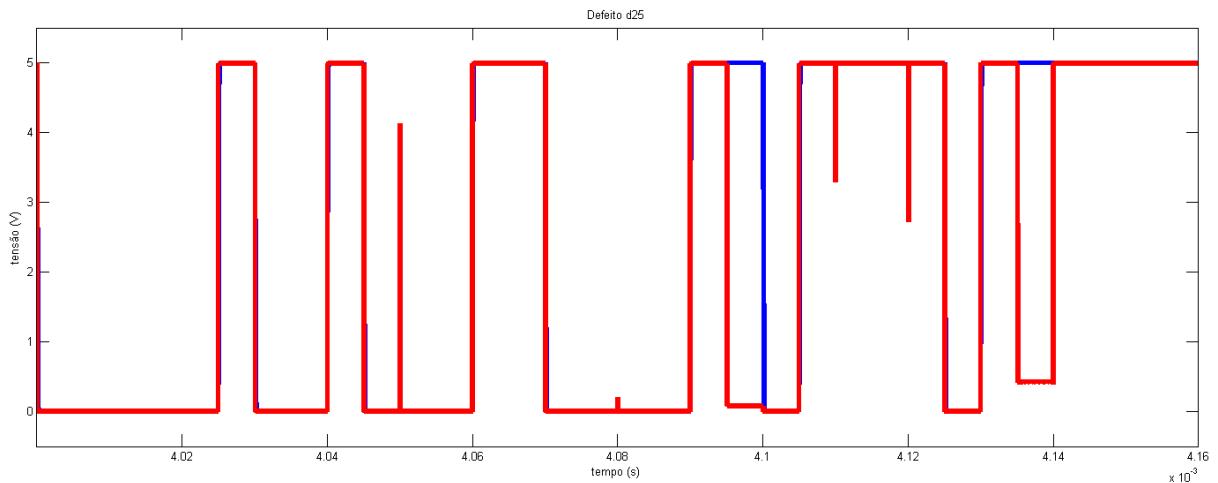

| Figura A.24–Resultado da simulação analógica com o defeito <b>d25</b> | 88  |

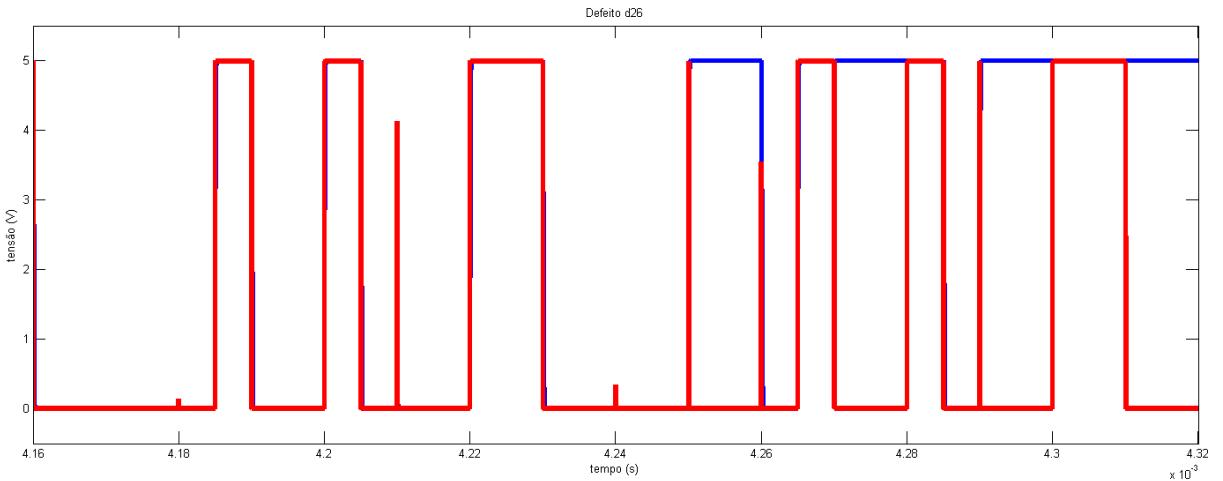

| Figura A.25–Resultado da simulação analógica com o defeito <b>d26</b> | 89  |

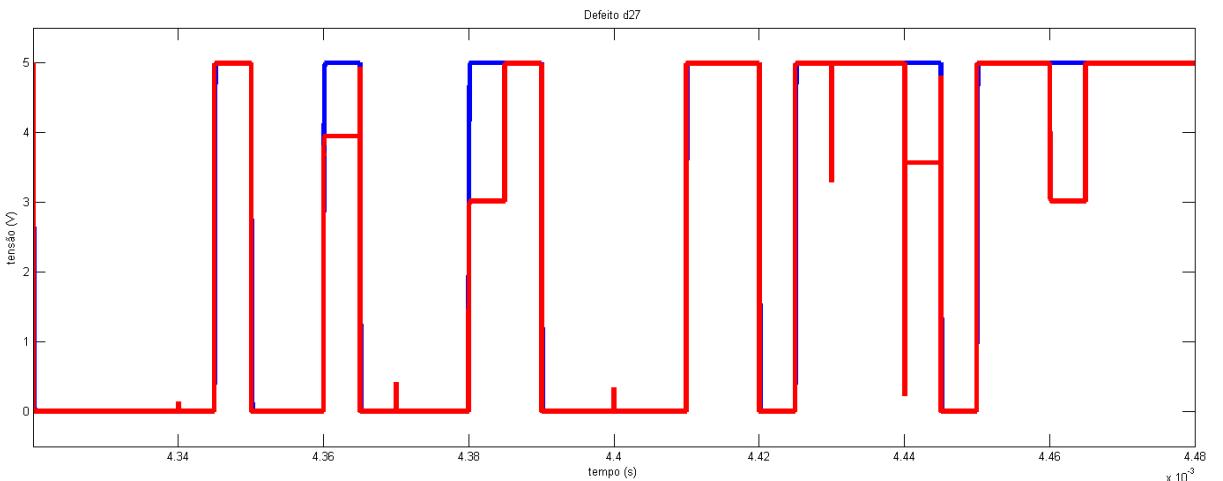

| Figura A.26–Resultado da simulação analógica com o defeito <b>d27</b> | 89  |

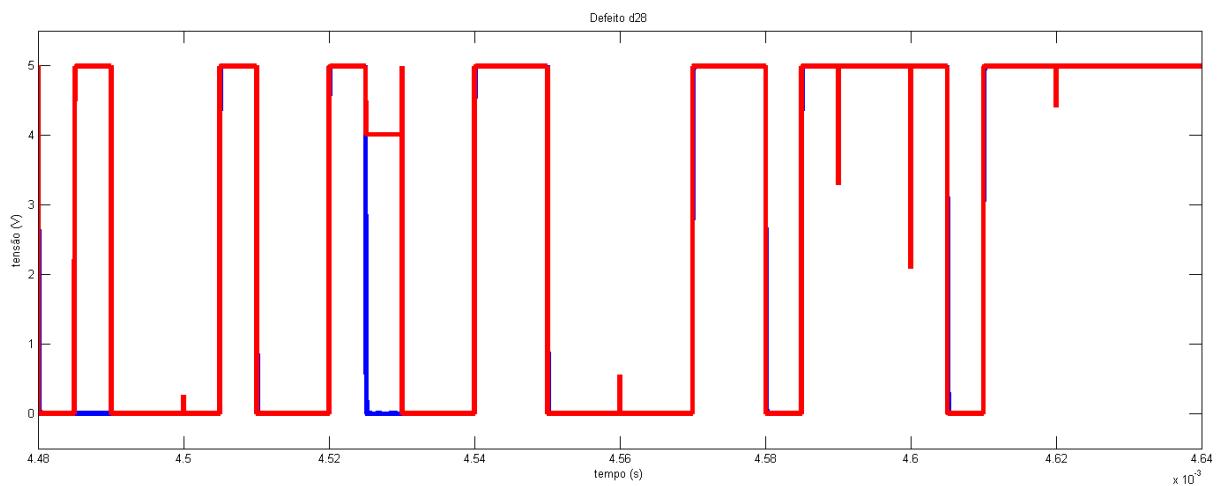

| Figura A.27–Resultado da simulação analógica com o defeito <b>d28</b> | 90  |

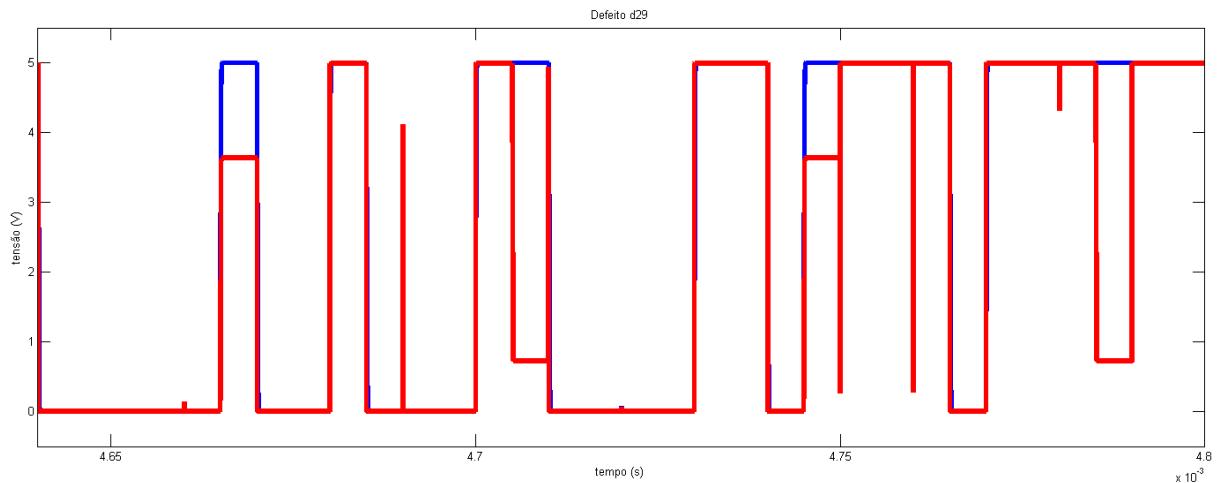

| Figura A.28–Resultado da simulação analógica com o defeito <b>d29</b> | 90  |

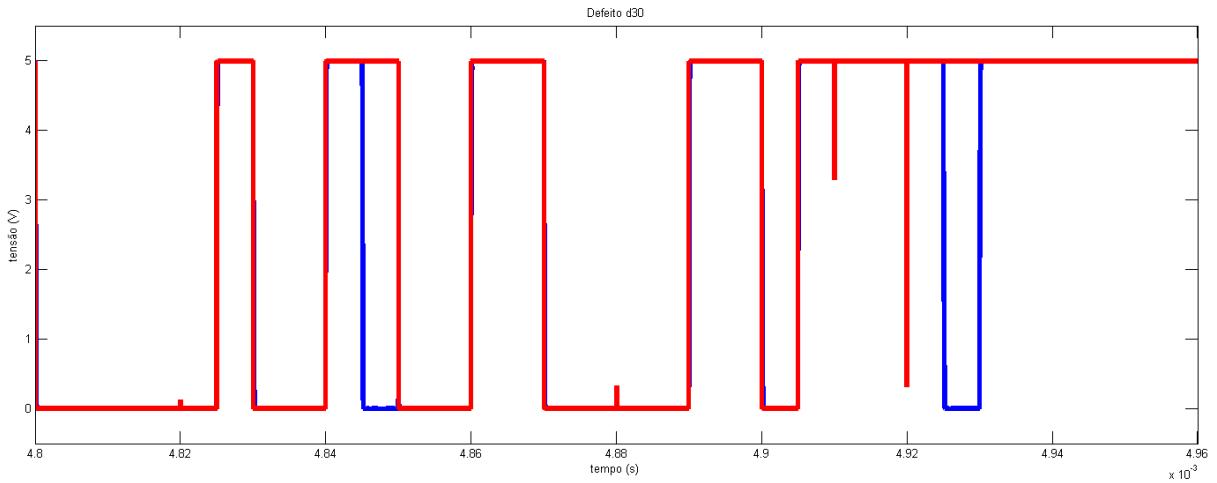

| Figura A.29–Resultado da simulação analógica com o defeito <b>d30</b> | 91  |

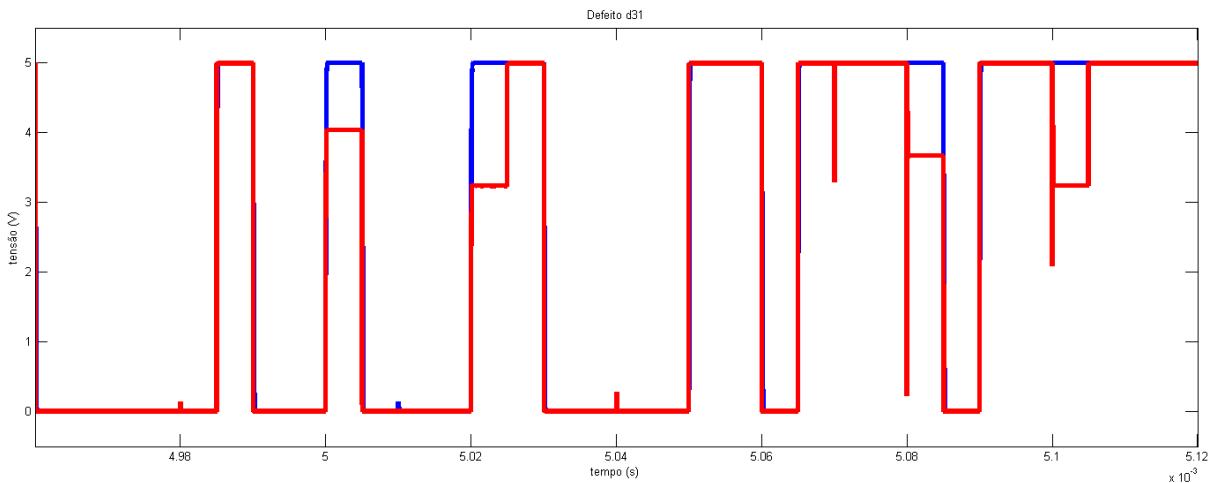

| Figura A.30–Resultado da simulação analógica com o defeito <b>d31</b> | 91  |

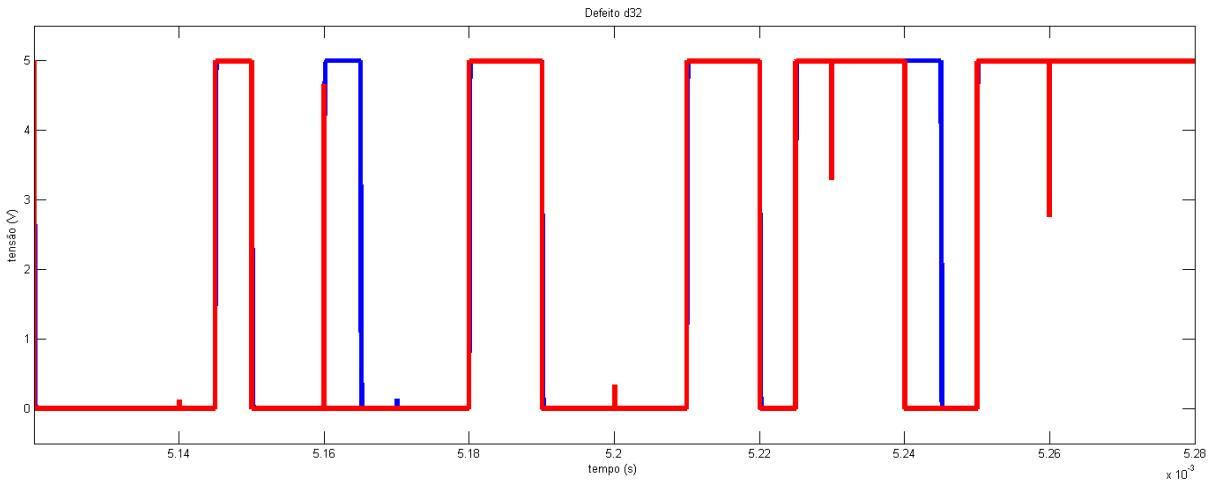

| Figura A.31–Resultado da simulação analógica com o defeito <b>d32</b> | 92  |

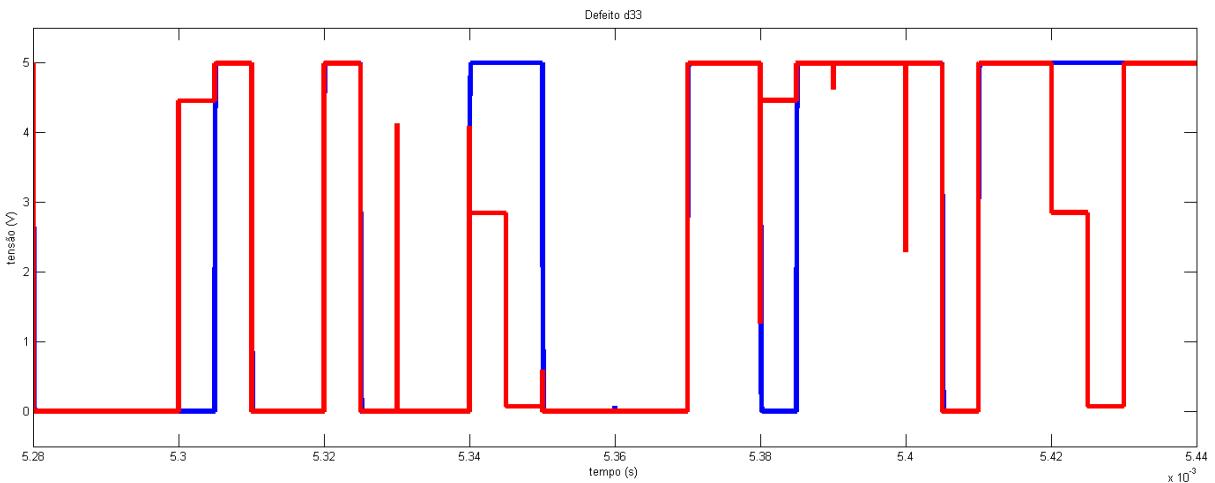

| Figura A.32–Resultado da simulação analógica com o defeito <b>d33</b> | 92  |

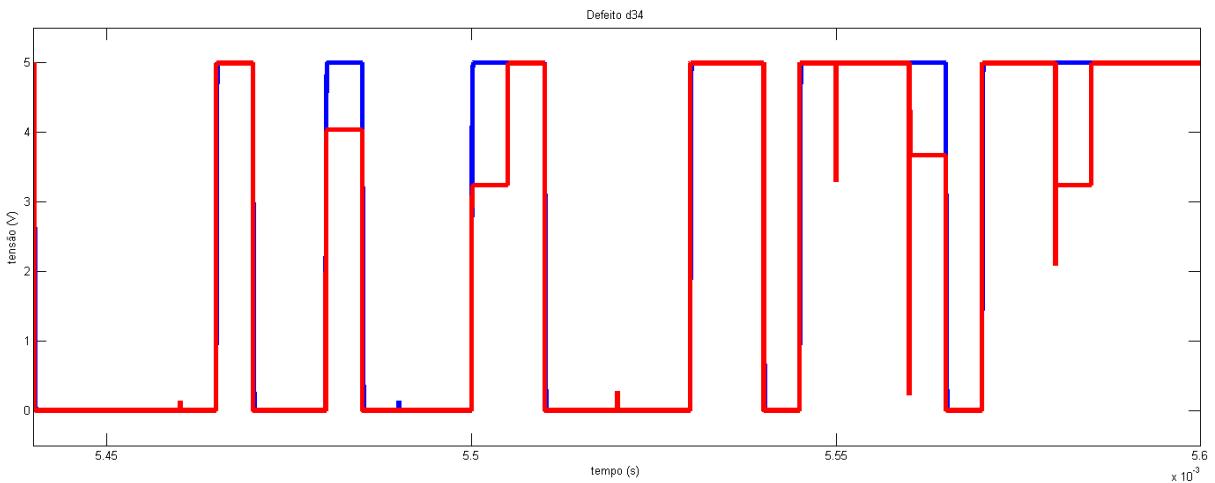

| Figura A.33–Resultado da simulação analógica com o defeito <b>d34</b> | 93  |

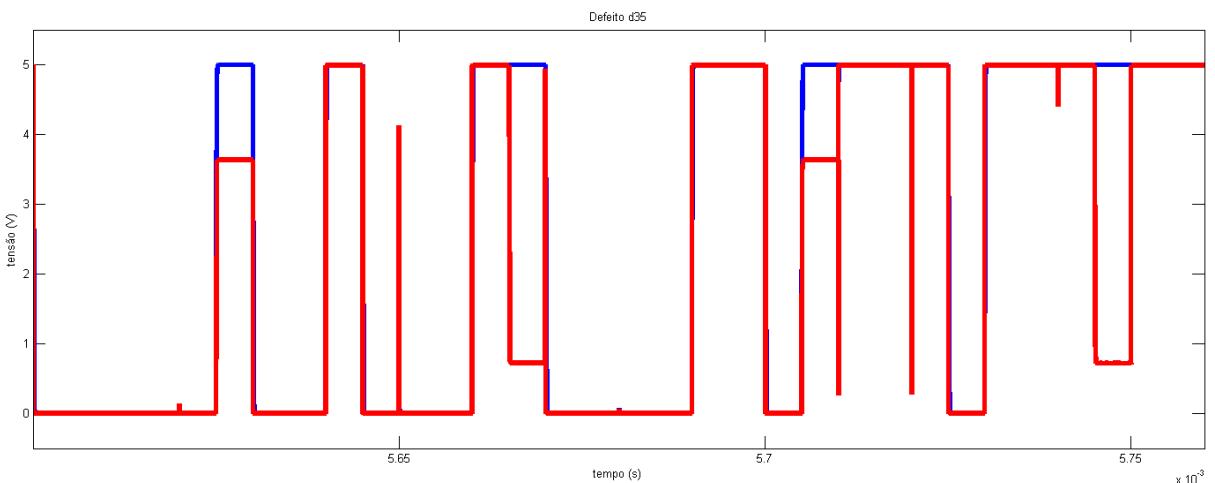

| Figura A.34–Resultado da simulação analógica com o defeito <b>d35</b> | 93  |

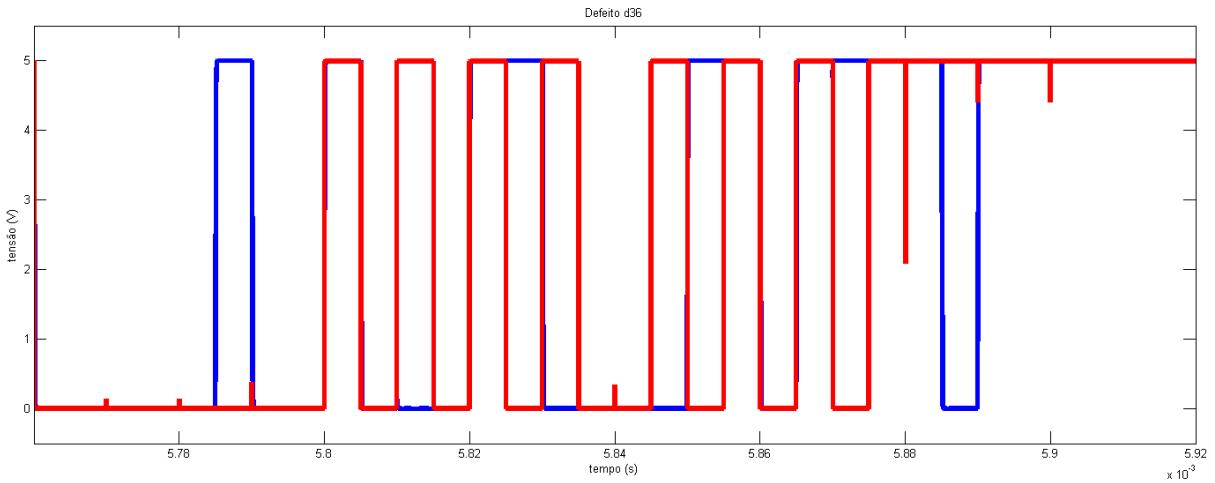

| Figura A.35–Resultado da simulação analógica com o defeito <b>d36</b> | 94  |

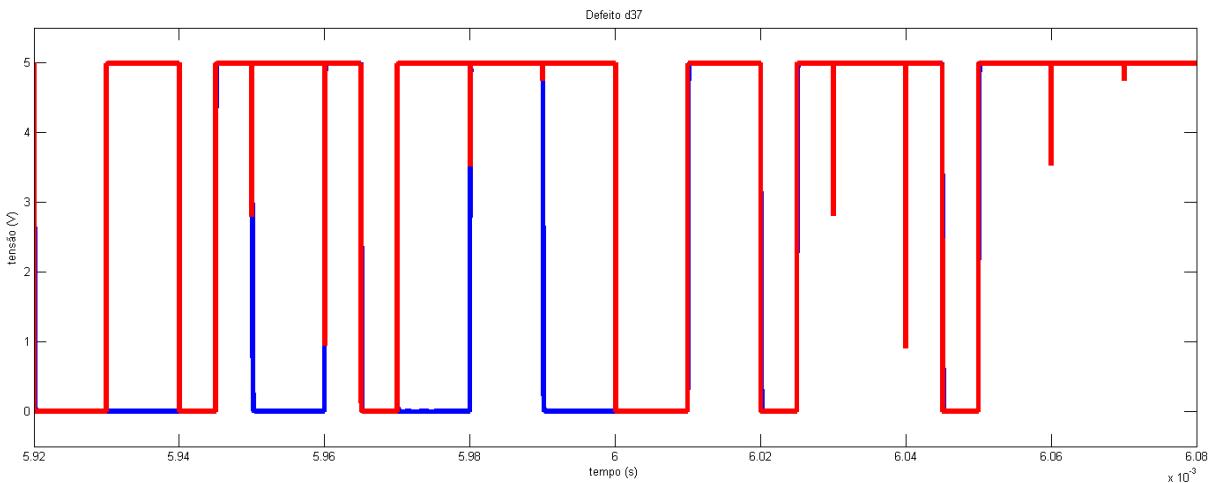

| Figura A.36–Resultado da simulação analógica com o defeito <b>d37</b> | 94  |

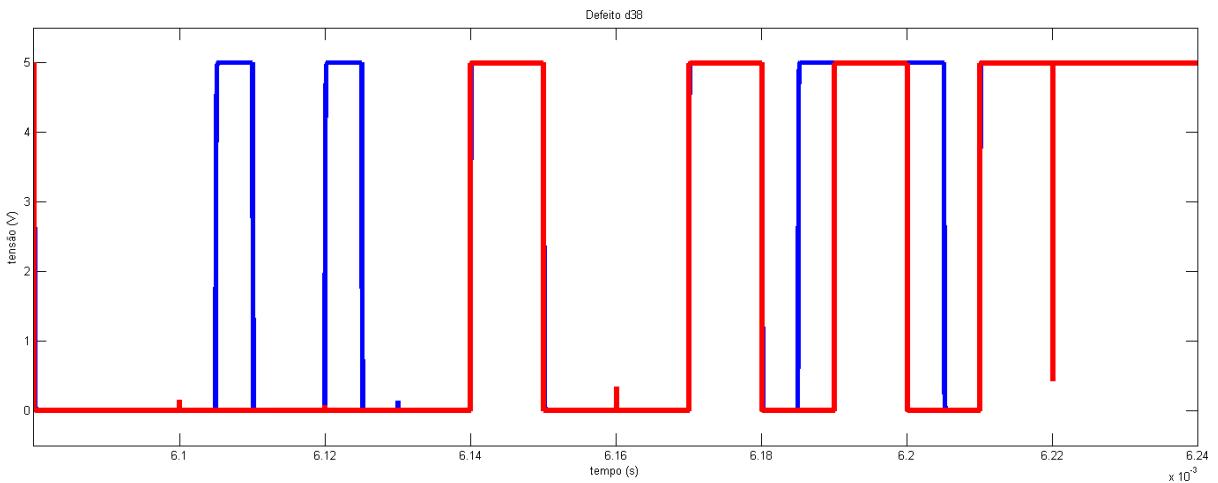

| Figura A.37–Resultado da simulação analógica com o defeito <b>d38</b> | 95  |

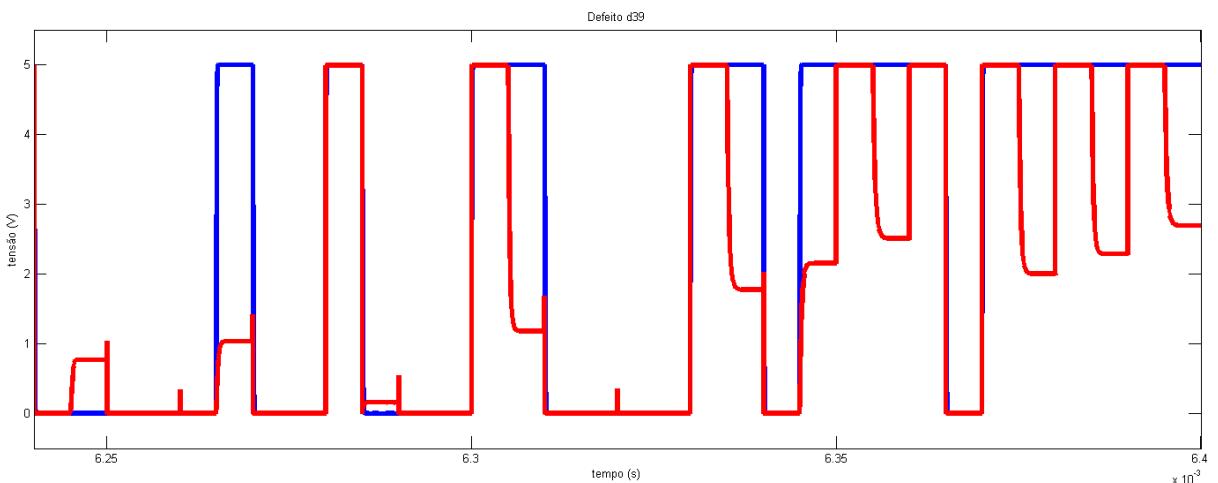

| Figura A.38–Resultado da simulação analógica com o defeito <b>d39</b> | 95  |

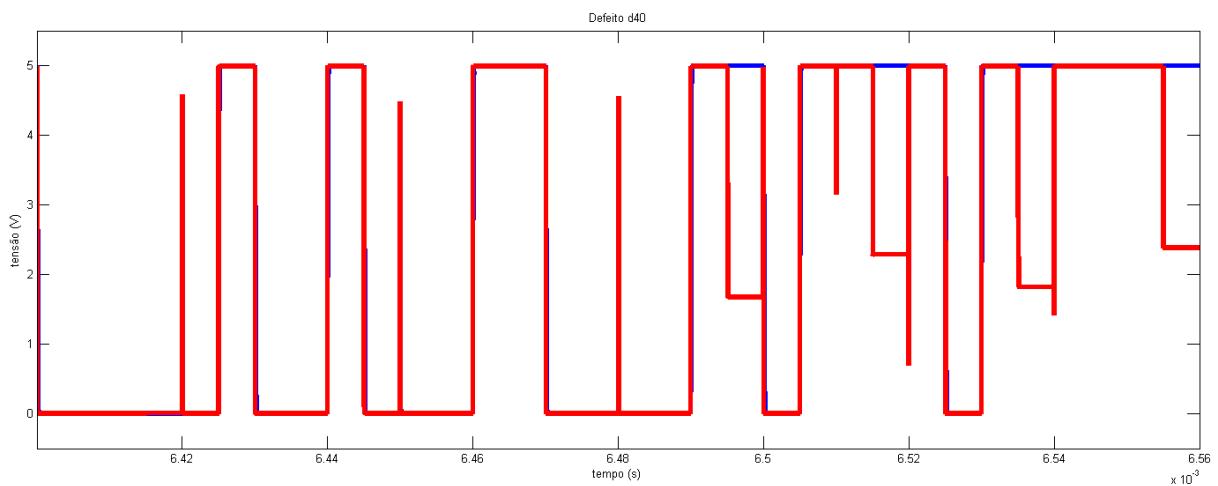

| Figura A.39–Resultado da simulação analógica com o defeito <b>d40</b> | 96  |

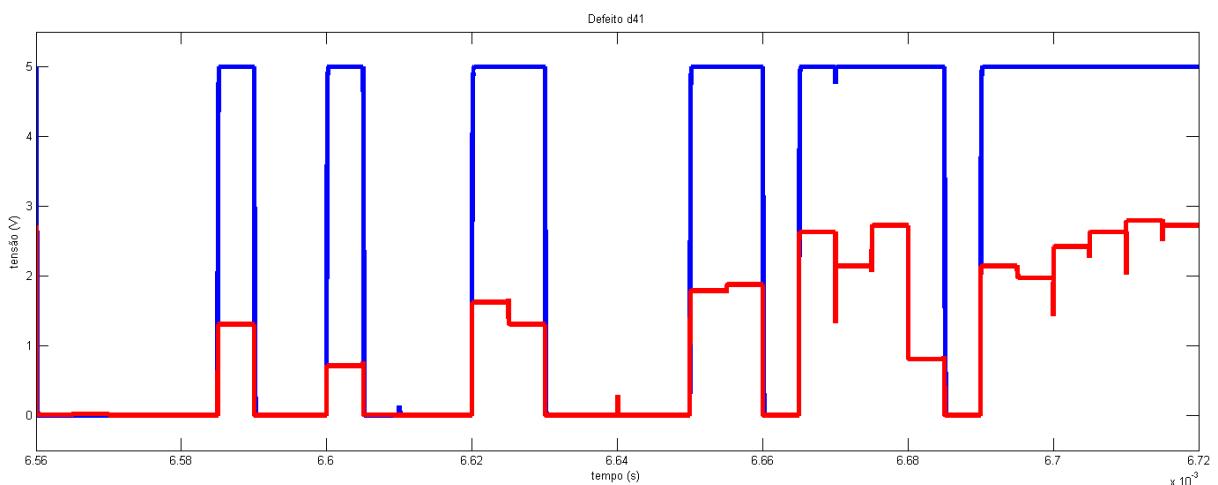

| Figura A.40–Resultado da simulação analógica com o defeito <b>d41</b> | 96  |

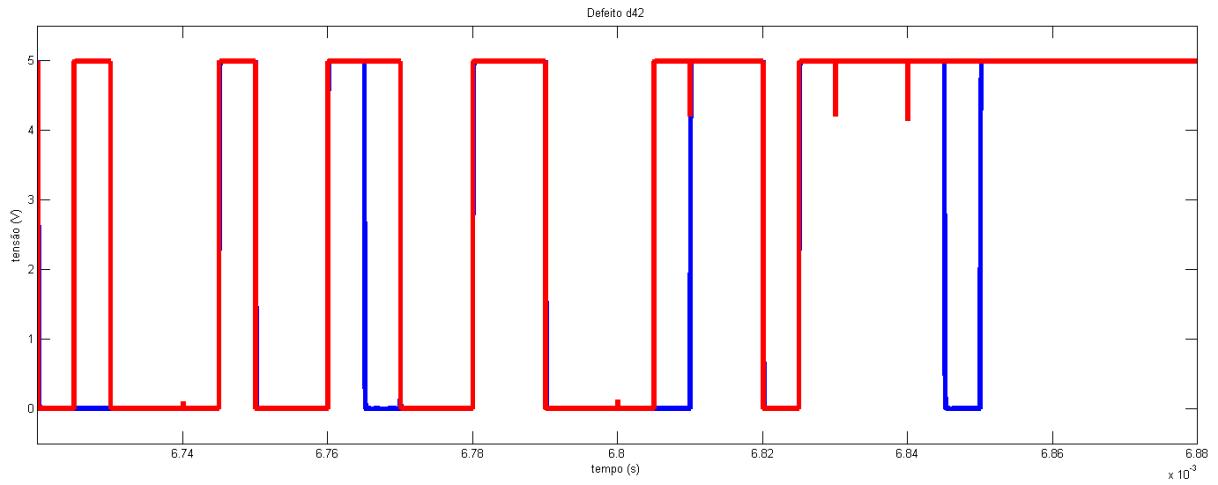

| Figura A.41–Resultado da simulação analógica com o defeito <b>d42</b> | 97  |

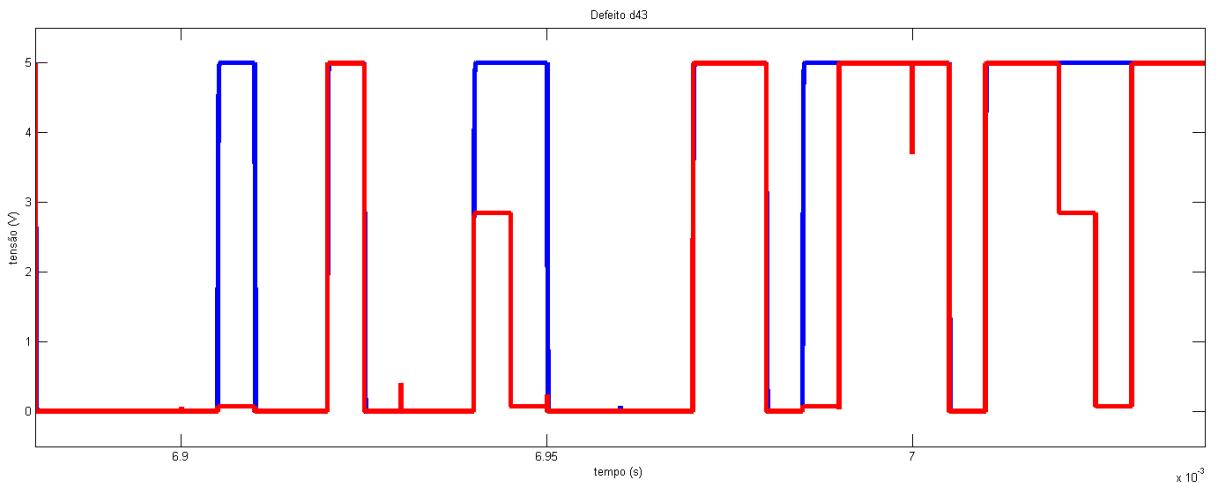

| Figura A.42–Resultado da simulação analógica com o defeito <b>d43</b> | 97  |

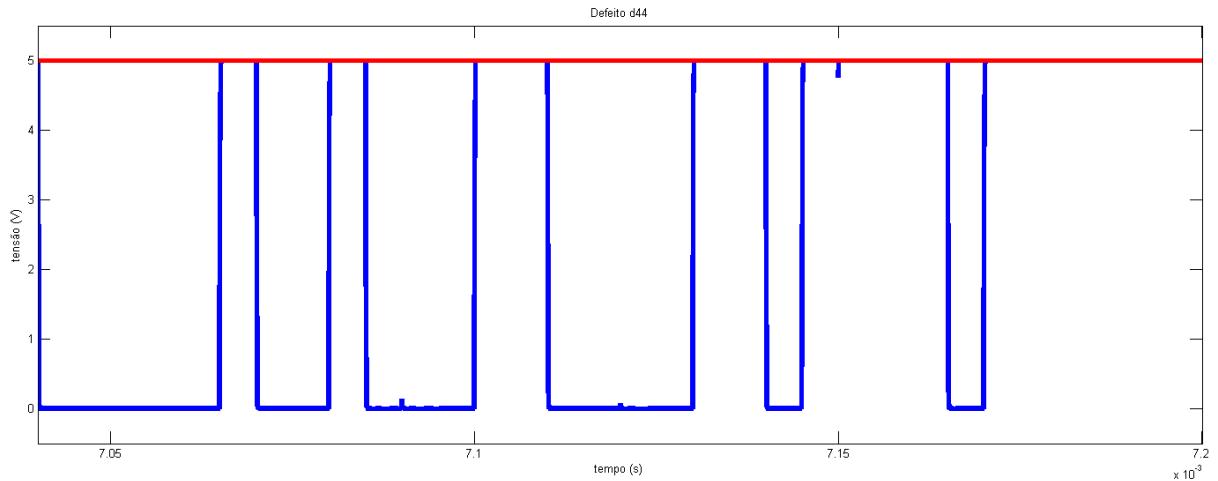

| Figura A.43–Resultado da simulação analógica com o defeito <b>d44</b> | 98  |

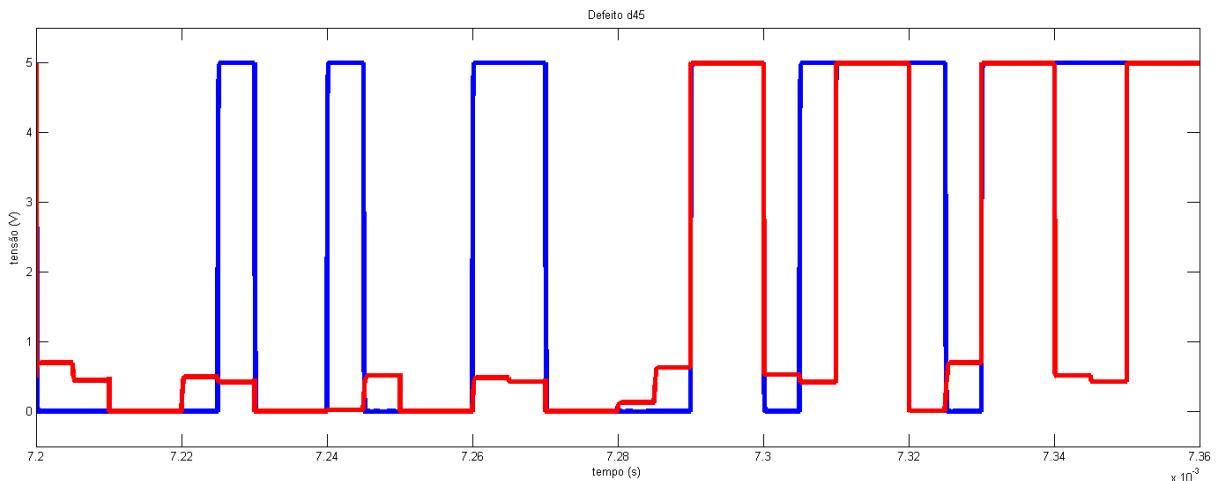

| Figura A.44–Resultado da simulação analógica com o defeito <b>d45</b> | 98  |

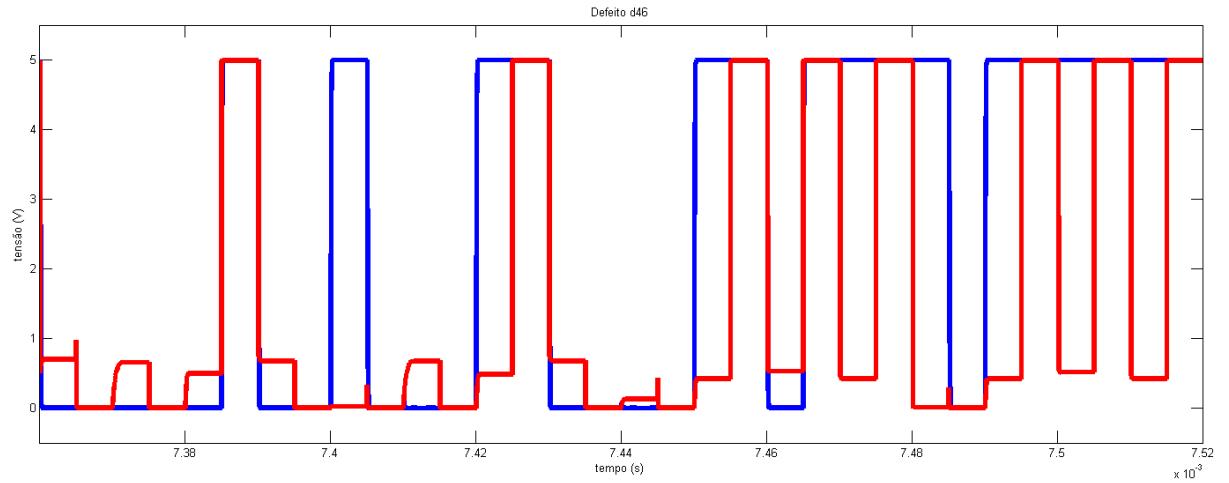

| Figura A.45–Resultado da simulação analógica com o defeito <b>d46</b> | 99  |

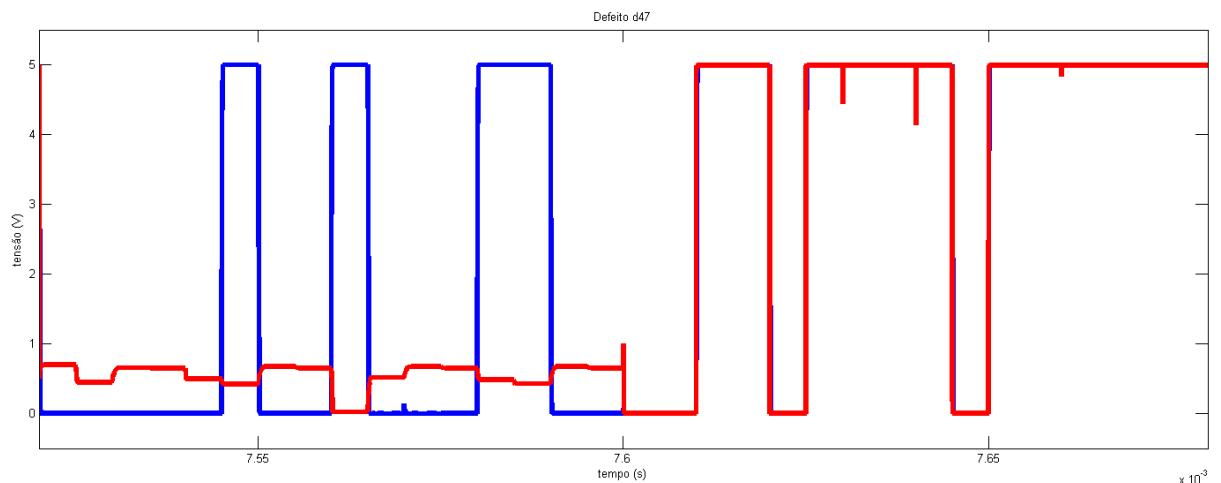

| Figura A.46–Resultado da simulação analógica com o defeito <b>d47</b> | 99  |

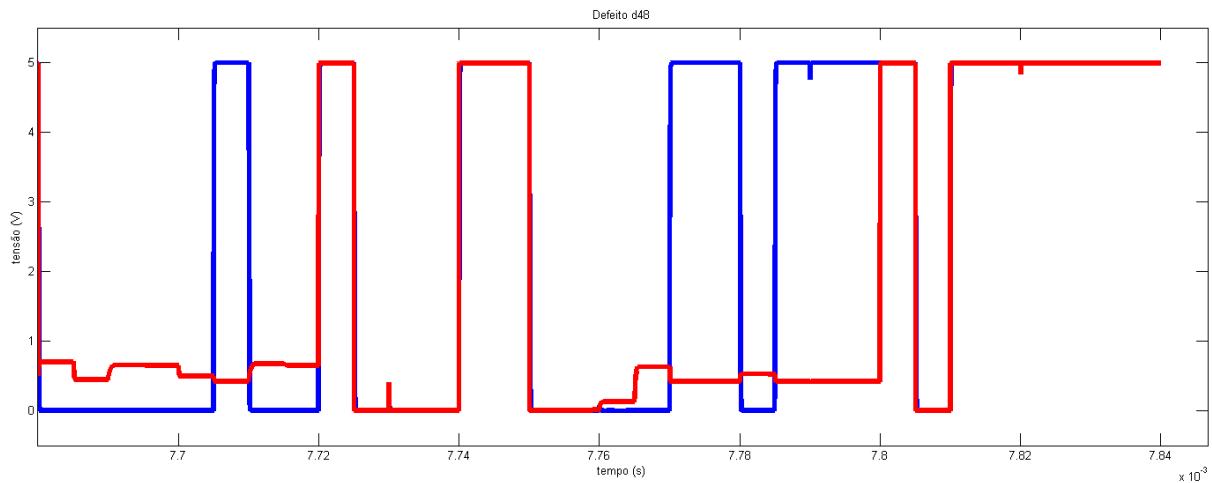

| Figura A.47–Resultado da simulação analógica com o defeito <b>d48</b> | 100 |

# **Lista de tabelas**

|                                                                            |    |

|----------------------------------------------------------------------------|----|

| Tabela 3.1 – Lista de defeitos . . . . .                                   | 27 |

| Tabela 3.2 – Matriz de Defeitos . . . . .                                  | 28 |

| Tabela 9.1 – Matriz de Defeitos obtidas por Simulação no CADENCE . . . . . | 70 |

# Lista de abreviaturas e siglas

|       |                                                            |

|-------|------------------------------------------------------------|

| ATE   | <i>Automatic Test Equipment</i>                            |

| ATPG  | <i>Automatic Test Pattern Generation</i>                   |

| BIST  | <i>Built-In Self Test</i>                                  |

| CAM   | <i>Cell-Aware Model</i>                                    |

| CAT   | <i>Cell-Aware Test</i>                                     |

| CDL   | <i>Compiler Description Language</i>                       |

| CI    | Circuito Integrado                                         |

| DFT   | <i>Design-for-Testability</i>                              |

| DRC   | <i>Design Rule Check</i>                                   |

| ERC   | Electrical Rule Check                                      |

| IBM   | <i>International Business Machine</i>                      |

| LVS   | <i>Layout Versus Schematic</i>                             |

| SPICE | <i>Simulated Program with Integrated Circuits Emphasis</i> |

| TPG   | <i>Test Pattern Generation</i>                             |

# Sumário

|           |                                                                                 |           |

|-----------|---------------------------------------------------------------------------------|-----------|

| <b>1</b>  | <b>Introdução</b>                                                               | <b>14</b> |

| 1.1       | Objetivos Gerais e Específicos                                                  | 19        |

| 1.2       | Materiais e Métodos                                                             | 20        |

| <b>I</b>  | <b>Referenciais teóricos</b>                                                    | <b>21</b> |

| <b>2</b>  | <b>Modelos de Falhas</b>                                                        | <b>22</b> |

| 2.1       | Modelo de falhas <i>Stuck-at</i>                                                | 22        |

| 2.2       | Modelo de falhas <i>Transition Delay</i>                                        | 23        |

| <b>3</b>  | <b>Cell-Aware Test</b>                                                          | <b>25</b> |

| <b>4</b>  | <b>Área Crítica</b>                                                             | <b>33</b> |

| <b>5</b>  | <b>Cálculo de Área Crítica baseado no Leiaute da Célula</b>                     | <b>37</b> |

| 5.1       | Função Densidade de Probabilidade do Defeito                                    | 38        |

| 5.2       | Área Crítica                                                                    | 39        |

| 5.3       | Contribuição de defeitos em interconexões paralelas                             | 40        |

| <b>6</b>  | <b>Processo de Fabricação CMOS</b>                                              | <b>44</b> |

| 6.1       | Processo de Fotolitografia, Criação de <i>n-well</i> e Crescimento do FOX       | 44        |

| 6.2       | Processo de Metalização                                                         | 46        |

| 6.3       | Tipos de Capacitâncias                                                          | 49        |

| 6.4       | Elementos Parasitas como Modelos de Falhas                                      | 51        |

| <b>II</b> | <b>Proposta</b>                                                                 | <b>53</b> |

| <b>7</b>  | <b>Extração de Elementos Parasitas no CADENCE</b>                               | <b>54</b> |

| <b>8</b>  | <b>Aplicação da Proposta do <i>Heat Map</i> em Células-Padrão da Biblioteca</b> | <b>62</b> |

| <b>9</b>  | <b>Implicações da Área Crítica em Cell-Aware Test</b>                           | <b>67</b> |

|           | <b>Conclusão</b>                                                                | <b>71</b> |

|           | <b>Referências</b>                                                              | <b>72</b> |

|           | <b>Apêndices</b>                                                                | <b>75</b> |

|           | <b>APÊNDICE A – Resultados de Simulação</b>                                     | <b>76</b> |

# 1 Introdução

Nos dias atuais, os sistemas eletrônicos estão cada vez mais presentes no nosso cotidiano. Nesse contexto, há um princípio fundamental: quanto maior é o benefício que esses sistemas oferecem ao nosso bem-estar, maior é o potencial de causarem algum dano quando falham ou não funcionam da maneira correta (SOUZA, 2005). Sistemas eletrônicos que são componentes de aviões, de aparelhos utilizados na medicina e de dispositivos eletrônicos de carros, são alguns exemplos em que a certeza de que esses sistemas funcionem corretamente é imprescindível. Quando esses sistemas não funcionam da forma esperada, danos graves podem ser causados e vidas podem ser perdidas (SOUZA, 2005). Então, para tais aplicações, é necessário o desenvolvimento de sistemas que tenham alta confiabilidade (SOUZA, 2005; CLIFFS, 1994).

A confiabilidade dos sistemas eletrônicos se dá com o aumento da confiabilidade dos componentes desses sistemas, que no exemplo citado são os **circuitos integrados** (CIs). Tal afirmativa sobre a confiabilidade baseia-se no princípio básico das técnicas de tolerância à falhas que explicam que o sistema como um todo depende da confiabilidade dos componentes que o constituem (CLIFFS, 1994).

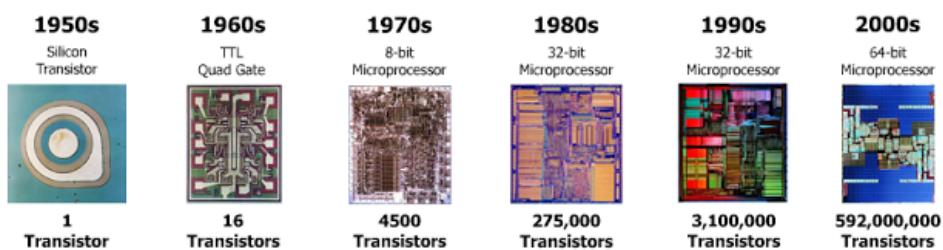

Figura 1.1 – Lei de Moore: A densidade de transistores dos circuitos integrados dobra a cada dois anos.

Fonte: Roberto et al. (2009).

Os circuitos integrados, a cada ano que passa, estão cada vez com áreas menores, com um número maior de transistores e mais integrados, como pode ser visto na Fig. 1.1. Uma das etapas de grande importância na fabricação de CIs são os testes que visam assegurar que o número de circuitos defeituosos que passem para os próximos níveis de manufatura do produto seja mínimo (SOUZA, 2005). Esses testes são necessários para verificar se o circuito integrado não está falho. Normalmente, testes de CIs são realizados utilizando **Equipamentos de Teste Automático** (ATE). Esses equipamentos são usados na aplicação de vetores de testes no circuito e no recebimento de suas respostas, e o objetivo final é verificar se o circuito está falho ou não, comparando a resposta do teste com a

esperada (SOUZA, 2005).

Para realizar os testes é necessário incluir, no projeto do CI, componentes tais como *flip-flops* e chaves que mudam o estado do CI para o estado de teste (HURST, 1998). A essa aplicação de componentes e técnicas de testes deu-se o nome de ***Design For Testability*** (DFT). A DFT é o desenvolvimento, projeto, aplicação de componentes e técnicas que serão aplicadas no CI (PLUSQUELLIC, 2006a).

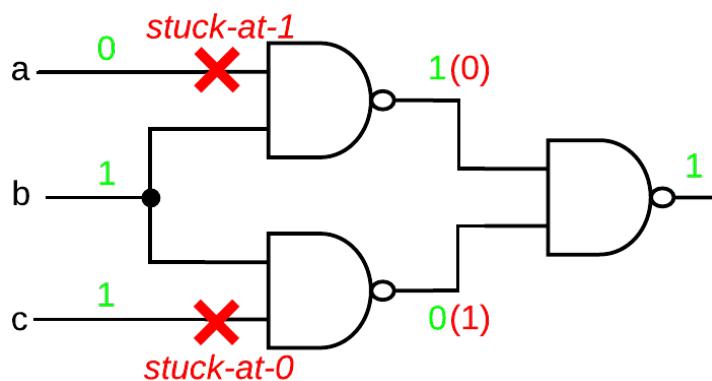

Para a proposição de métodos de testes em CIs é necessário utilizar modelos de falhas, que podem ser definidos como representações dos possíveis defeitos físicos presentes no CI. Por exemplo, para modelar um defeito em que a entrada da porta lógica está presa em nível lógico 1, como por exemplo quando há uma ligação fixa entre a entrada e VDD (tensão de alimentação), dizemos que pode ocorrer uma falha ***Stuck-At***. E, como é presa em nível lógico 1, dá-se o nome de ***stuck-at-1*** para essa falha. O mesmo modelo de falhas pode modelar vários tipos de defeitos físicos. Na Figura 1.2 observa-se que há uma falha *stuck-at-1* na entrada *a* e uma falha *stuck-at-0* na entrada *b*, o que significa que, por algum defeito físico, o valor lógico dessas entradas se manteve constante. Neste exemplo pode-se ver que as falhas nas entradas não ocasionaram um **erro** na saída. Então, isso significa que nem toda falha causa um erro no circuito integrado (PLUSQUELLIC, 2006b). No modelo *stuck-at*, curto-circuitos internos à célula como em transistores em curto ou aberto, são modelados como falhas nas entradas e saídas das portas lógicas. O modelo *stuck-at* é amplamente utilizado atualmente e cobre uma alta porcentagem dos defeitos físicos passíveis de ocorrer em um circuito integrado (PLUSQUELLIC, 2006b).

Figura 1.2 – Falha *Stuck-At*.

Fonte: Elaborada pela autora.

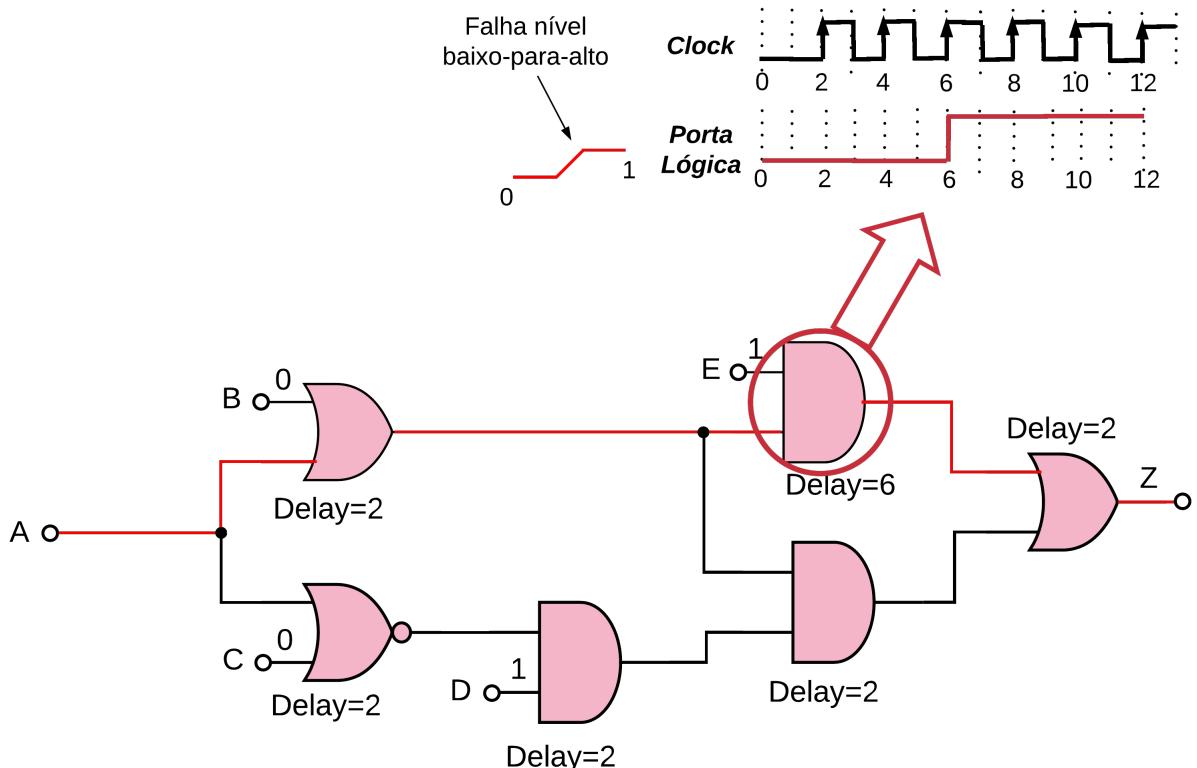

O modelo de falhas *stuck-at* é o mais conhecido e utilizado atualmente (PLUSQUELLIC, 2006b). O segundo modelo mais utilizado é o ***Transition Delay*** (COX; RAJSKI, 1988) que modela os defeitos que causam atraso na mudança de estado em portas lógicas. CIs que operam em alta frequência são mais afetados por falhas *transition delay*. Isso acontece devido à rapidez do chaveamento dos estados lógicos em cada porta lógica.

À medida que essas transições ocorrem em um curto espaço de tempo, há a necessidade de saber se estão ocorrendo de forma correta. Assim como nas falhas *stuck-at*, as falhas são modeladas nas entradas e saídas das portas lógicas. Existem dois tipos de falhas *transition delay*: a **falha nível baixo-para-alto**, que é quando o atraso é na transição de nível baixo para o nível alto e a **falha nível alto-para-baixo** em que atraso acontece na transição de nível alto para o nível baixo (WAICUKAUSKI et al., 1987).

Figura 1.3 – Falha *Transition Delay* (GARCIA, 2001).

Fonte: Elaborada pela autora.

Na Figura 1.3 pode ser visto um exemplo de falha *transistion delay*, em que a porta lógica em destaque está com um atraso maior do que o *clock* do circuito. Em consequência disso, a porta lógica que tem a falha demorará três pulsos de *clock* para responder à mudança de nível lógico. Esse atraso é dado na mudança de nível lógico de 0 para 1, ou seja, falha nível baixo-para-alto.

Tanto o modelo de falhas *Stuck-At* quanto o modelo *Transition Delay* representam defeitos físicos que podem ocorrer nos circuitos integrados. Os fabricantes precisam de modelos altamente eficientes para que um maior número de defeitos possam ser detectados. Com o tempo, os clientes (fabricantes de produtos que tem como componentes os circuitos integrados) começaram a reportar que recebiam CI's defeituosos de seus fabricantes, ou

seja, esses componentes passavam nos testes, mas na verdade estavam com problema. Ao investigar o problema, descobriu-se que a maioria dos defeitos que passavam despercebidos aos testes ocorriam dentro da biblioteca de células padrão, que são conjuntos de transistores e interconexões que formam funções booleanas tais como AND, OR, NAND, XOR (HAPKE et al., 2014). Muitos desses defeitos que, são internos à célula, permanecem não-detectados quando se usam ferramentas tradicionais de **Automatic Test Pattern Generator** (ATPG).

Além do problema de componentes defeituosos que passam nos testes, vale salientar que os modelos de falhas clássicos abordam o problema de defeitos apenas parcialmente (HAPKE et al., 2014). Com essas desvantagens apresentadas pelos modelos de falhas clássicos, alternativas estão sendo estudadas nos últimos anos para resolver estes problemas. Sendo a mais relevante a que trata do modelamento de falhas e simulações analógicas baseadas em *netlist* SPICE (*Simulated Program with Integrated Circuits Emphasis*) contendo apenas transistores e não os objetos parasitas (capacitores, resistores), mas ainda assim considerando o leiaute físico (HAPKE et al., 2014). Com isso, Hapke et al. (2014) juntamente com a Mentor Graphics<sup>©</sup> definiram o que é o **Cell-Aware Test** ou **CAT**, que são modelos de falhas na perspectiva do leiaute (HAPKE et al., 2009; HAPKE et al., 2010; HAPKE et al., 2014).

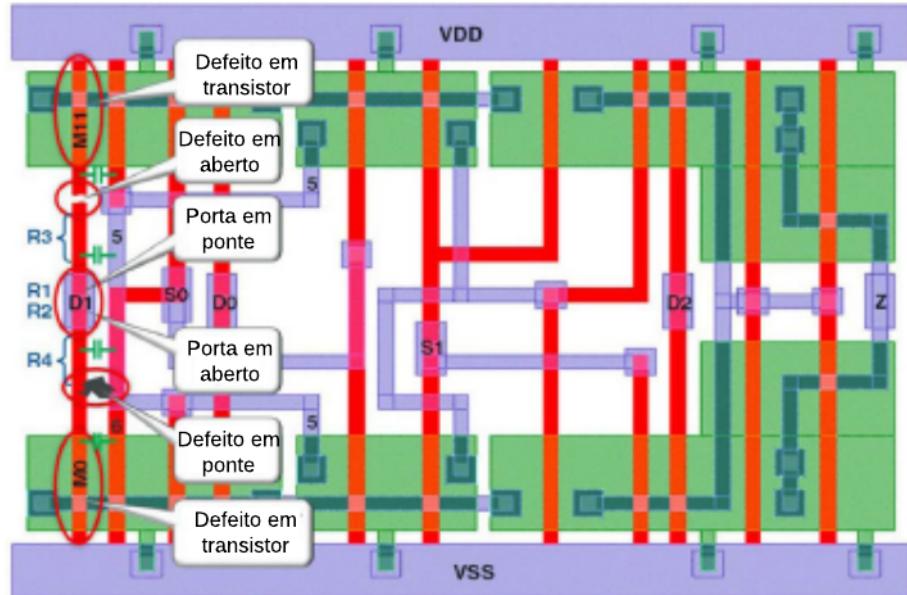

Nas pesquisas em torno do CAT é mostrada a necessidade atual de que os modelos de falhas sejam baseados no leiaute do circuito, e não apenas em modelos generalizados. Foram criados modelos de falhas específicos, baseado nos defeitos físicos que possam ocorrer, como pode ser visto na Figura 1.4. Os modelos de falhas do CAT se baseiam nas resistências e capacitâncias parasitas (que não são as componentes do circuito, e sim as que surgem pelas distâncias das interconexões), além das entradas e saídas dos circuitos integrados para criar os modelos (HAPKE et al., 2009; HAPKE et al., 2010; HAPKE et al., 2011; HAPKE et al., 2014).

Estudos baseados no leiaute já haviam sido feitos em anos anteriores (JACOMET; GUGGENBUHL, 1993; BABEL et al., 1995a; ALLAN; WALTON, 1997a; ALLAN; WALTON, 1998; ALLAN; WALTON, 1999a; Chao-Wen Tzeng; Han-Chia Cheng; Shi-Yu Huang, 2009). Esses estudos eram baseados no que se chamou de **Área Crítica**. Na Figura 1.5 pode-se observar que área crítica é a área entre as interconexões em que é mais provável de acontecer uma falha dado um defeito físico. Se tal defeito não conectar as interconexões, ele não é considerado uma falha. Esse conceito foi motivado pela necessidade de criar modelos que fossem baseados no leiaute dos circuitos integrados (ALLAN; WALTON, 1998). Dessa forma criou-se uma maneira de calcular a área crítica de acordo com o tamanho dos defeitos físicos que possam ocorrer. Dados os conceitos definidos pelo *Cell-Aware Test* (HAPKE et al., 2014) e de ÁREA CRÍTICA (JACOMET; GUGGENBUHL, 1993), ambos

Figura 1.4 – Defeitos extraídos de um leiaute.

Fonte: Adaptada de (HAPKE et al., 2014).

Figura 1.5 – Área Crítica.

Fonte: Elaborada pela autora.

baseados em leiaute, buscou-se com este trabalho relacionar os dois conceitos para que se possa comprovar que eles se complementam.

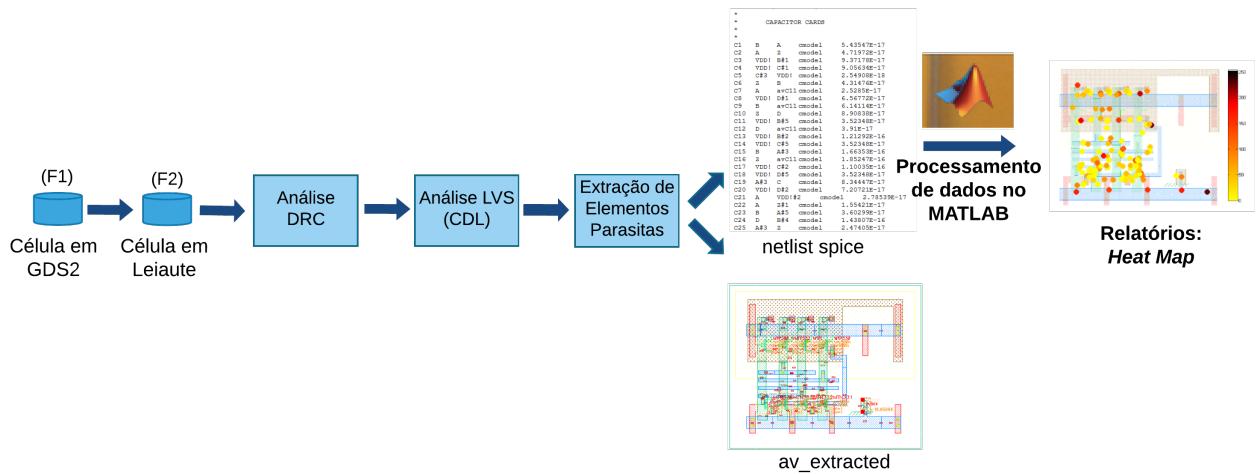

Ao relacionar os conceitos da área crítica com os cálculos necessários para criar os modelos de falhas CAT (HAPKE et al., 2014), viu-se que é possível uma análise visual das regiões com maior suscetibilidade à falhas através do *heat map*. Dada essa análise, a proposta do trabalho é de uma nova forma de avaliação na perspectiva do leiaute que utiliza *heat map* como forma de observação e estudos de regiões propícias à falhas. Nesse tipo de avaliação do leiaute, elementos parasitas são usados como parâmetros para identificar em que regiões defeitos físicos tem maior probabilidade de se tornarem falhas. O *heat map* é a representação gráfica de uma matriz de valores, sendo assim, uma matriz de valores de elementos parasitas foi usada como dados de um *heat map* para obtenção de regiões com

maior suscetibilidade à falhas. Essa proposta foi realizada usando ferramentas CADENCE, para obtenção do leiaute de um determinado circuito lógico e MATLAB, para gerar o *heat map*.

Neste trabalho será dissertado o conceito de modelo de falhas no Capítulo 1. No Capítulo 2 serão analisados os conceitos do *Cell-Aware Test* (CAT), em seguida, no Capítulo 3 será analisada Área Crítica. No Capítulo 4 serão relacionados os dois conceitos e serão vistas as implicações da Área Crítica em *Cell-Aware Test*. No Capítulo 5 será analisado o Processo de Fabricação CMOS, Metalização e Tipos de Capacitâncias Parasitas. Na sequência, no Capítulo 6 serão analisados do Elementos Parasitas como Modelos de Falhas, e no Capítulo 7 como é feita essa Extração de Elementos Parasitas no CADENCE. Para em seguida, no Capítulo 8 ser mostrada a Aplicação da Proposta *Heat Map* em Células-Padrão da Biblioteca. Para em seguida, ser retomada as Implicações de Área Crítica em *Cell-Aware Test*. Na Conclusão será dissertado sobre os trabalhos feitos com o CADENCE, tanto em simulações analógicas quanto em extração de elementos parasitas, que irão comprovar os conceitos apresentados neste trabalho.

## 1.1 Objetivos Gerais e Específicos

O objetivo geral do trabalho é fazer uma análise de defeitos na perspectiva do leiaute em células de bibliotecas padrão. Ao analisar trabalhos que vem sendo feitos no estado-da-arte observou-se uma crescente aplicação e estudos de modelos de falhas baseados no leiaute. As pesquisas atuais utilizam ao invés de portas lógicas, transistores e elementos parasitas para se basear nos modelos falhas (HAPKE et al., 2009; HAPKE; SCHLOEFFEL, 2012; HAPKE et al., 2014). Nesse contexto, neste trabalho foram feitas simulações analógicas com a inclusão de falhas extraídas de um multiplexador exemplo do artigo do Hapke para observar como as saídas seriam afetadas pelas falhas, para em seguida documentar os resultados na chamada Matriz de Defeitos, que a posteriori é utilizada para obter padrões de testes. Após essas análises, foram feitos estudos dos conceitos de área crítica, densidade de defeitos, função densidade de probabilidade de defeitos e cálculo dos defeitos, para compreender como essas falhas são modeladas. Esses conceitos são de grande importância, pois com eles conseguiu-se desenvolver neste trabalho um fluxograma de análise de defeitos próprio. O fluxograma proposto começa com a extração dos elementos parasitas do leiaute de uma célula-padrão, para em seguida obter o arquivo de capacitâncias parasitas que será utilizado para fazer um *heat map* das regiões em que serão mais prováveis de que um defeito se torne uma falha. A proposta é de que a análise na perspectiva do leiaute seja baseada em *heat maps* com seus valores dados por capacitâncias parasitas e não mais pelos modelos de falhas matemáticos.

Os objetivos específicos do trabalho são:

- Realizar simulações analógicas com modelos de falhas na perspectiva do leiaute;

- Analisar como extrair elementos parasitas do leiaute;

- Associar os valores de capacitâncias à níveis de defeitos;

- Proposta de análise do leiaute a partir do *heat map*; e

- Proposta do *heat map* realizado no CADENCE e MATLAB.

## 1.2 Materiais e Métodos

A metodologia utilizada para simulação de modelos de falhas na perspectiva do leiaute, foi baseada em realizações de simulações analógicas na ferramenta spectre do CADENCE para observar as respostas de um multiplexador com falhas em ponte pré-definidas (HAPKE et al., 2009). A metodologia para o desenvolvimento do fluxograma de extração de *heat map*, proposto neste trabalho para análise na perspectiva do leiaute, foi a extração de elementos parasitas para a avaliação das regiões de maior probabilidade de falhas no leiaute. Essa extração foi feita com o Assura RCX, que extrai elementos parasitas como resistores, capacitores e indutâncias. Após a extração foi utilizado o MATLAB com os valores de capacitâncias e localizações (x,y) para a obtenção do *heat map* do dado leiaute.

A obtenção do *heat map* se inicia ao exportar a imagem do leiaute do CADENCE para o MATLAB. Com a imagem do leiaute no MATLAB é possível avaliar em que localizações estão contidos os elementos parasitas (capacitâncias). Para obter as regiões de suscetibilidade à falhas, os cálculos são feitos a partir da matriz bidimensional dos elementos parasitas, que dará como resultado, com as dadas funções do MATLAB, o *heat map*.

# Parte I

## Referenciais teóricos

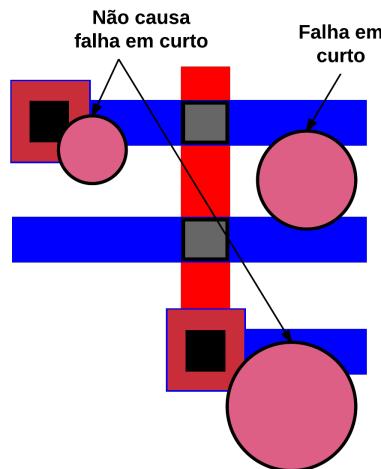

## 2 Modelos de Falhas

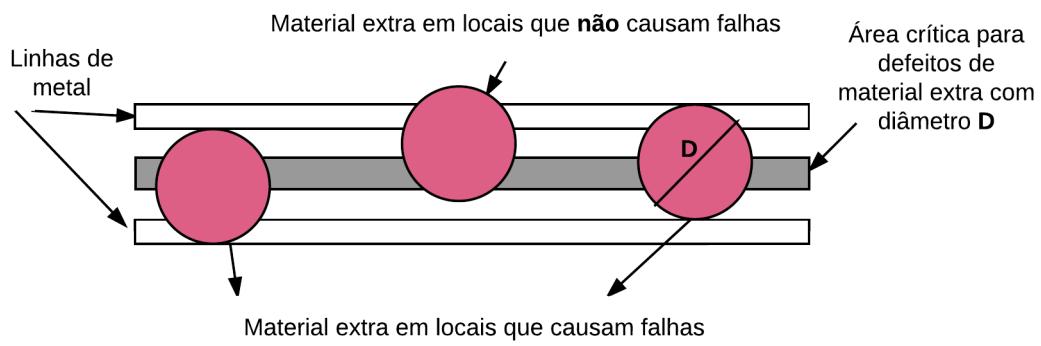

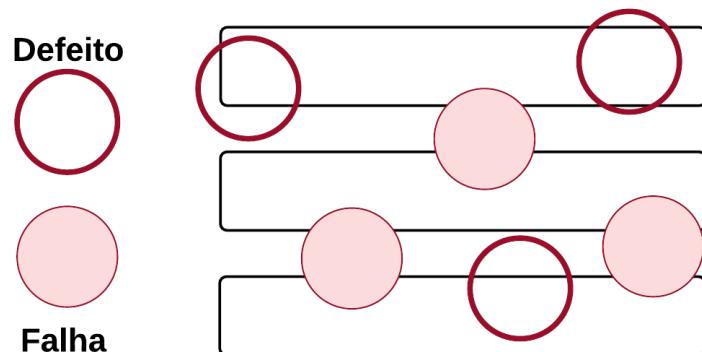

Antes de descrever sobre modelos de falhas, é necessário definir alguns conceitos essenciais para se tratar de testes e que serão utilizados ao longo de todo o trabalho. Um desses conceitos são os defeitos físicos, que podem ser causados por material extra no processo de fabricação, ou seja, é o que pode ocorrer fisicamente no CI (ALLAN, 1998). Falha é a possível consequência do defeito físico, se houver material extra que cause um curto entre as interconexões, por exemplo, haverá uma falha. Esse conceito, da diferença entre falha e defeito é demonstrado na Figura 2.1.

Figura 2.1 – Diferença entre **falha** e **defeito**.

Fonte: Elaborada pela autora.

Uma etapa primordial no processo de testes é a etapa da aplicação dos modelos de falhas. Modelos de falhas são representações de defeitos físicos que podem ocorrer em circuitos integrados (ALLAN, 1998). Defeitos como curto-circuitos, abertos e em ponte são os mais comuns de ocorrerem (HAPKE et al., 2014). Para isso, modelos de falhas vem sendo estudados ao longo dos anos para que a maior parte desses possíveis defeitos físicos possa ser modelada.

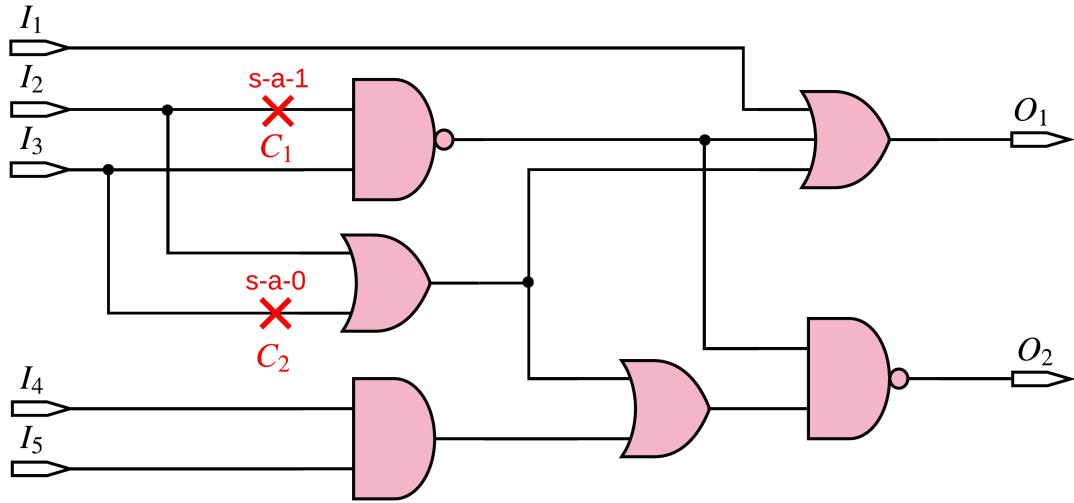

### 2.1 Modelo de falhas *Stuck-at*

Um dos primeiros modelos de falhas e mais conhecido na área de testes foi criado em 1963 é o modelo *Stuck-at* (MEI, 1974). Esse modelo é amplamente utilizado e modelam diferentes tipos de defeitos, como entradas/saídas fixas em nível lógico (*stuck-at-1*) e entradas/saídas fixas em nível lógico (*stuck-at-0*). Pode-se observar pela Figura 2.2 que esses nomes podem ser abreviados como *s-a-1* e *s-a-0*.

Figura 2.2 – Circuito com falhas, C1 stuck-at-1 e C2 stuck-at-0 (WU; LEE, 2014).

Fonte: Elaborada pela autora.

O modelo de falhas *stuck-at* é muito utilizado na indústria (HAPKE et al., 2010). As empresas responsáveis pela fabricação dos circuitos integrados da indústria automotiva, como exemplo Freescale Semicondutores, tem por objetivo entregar chips com 99% de cobertura de falhas *stuck-at* para os fabricantes automotivos. Isso significa dizer que os testes projetados para o circuito integrado cobrem 99% das falhas *stuck-at* que possam ocorrer. Apesar de amplamente utilizado atualmente, esse modelo de falhas vem apresentando uma dificuldade em atingir a cobertura que é requisitada. Fato esse que é dado por um considerável número de defeitos físicos que não são modelados pelas falhas *stuck-at*. Para isso, são usados outros modelos de falhas que considerem esses defeitos físicos.

## 2.2 Modelo de falhas *Transition Delay*

Defeitos que causam falhas mas que não são relacionados com tempo de mudança de estado na porta lógica são chamados **defeitos estáticos**. Já defeitos que causam falhas e são relacionados com as mudança de estado da porta lógica, são os chamados **defeitos de *delay*** (CHENG et al., 2008). Para detectar defeitos de *delay*, padrões específicos são utilizados.

Para inserir os padrões específicos para falhas *transition delay* é necessário fazer transições de níveis lógicos a cada pulso de *clock* para verificar se há falhas (CHENG et al., 2008). Como são observadas as transições de níveis lógico, o modelo de falha *transition delay* requer pelo menos dois pulsos de *clock* para serem detectadas. Para testar a falha é necessário colocar valor de transição nesses dois ciclos, mudar de 0 – 1 (borda de subida)

ou  $1 - 0$  (borda de descida) e verificar se há mudança de estados de um ciclo para o outro. Essa é a definição para os testes do modelos de falhas *transition delay*.

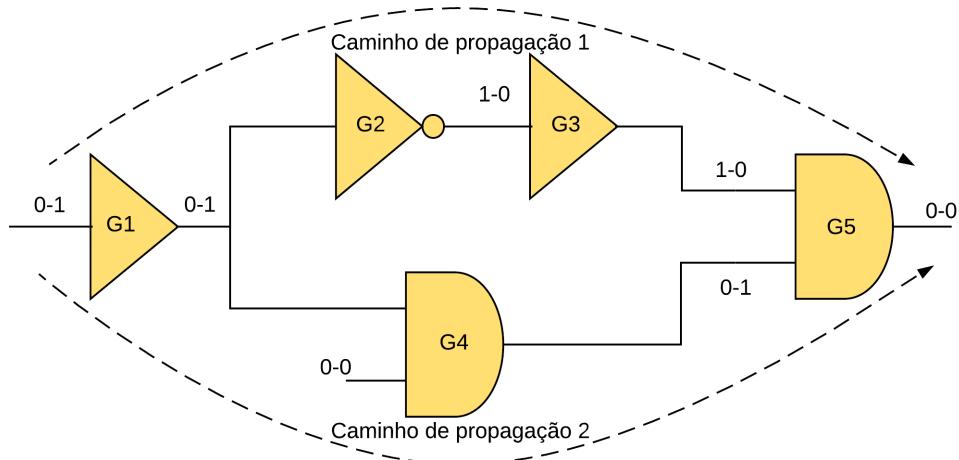

Na Figura 2.3 pode-se observar como exemplo de modelo de falhas *transition delay* um circuito com cinco portas lógicas. O efeito da transição ( $0 - 1$ ) é colocado na entrada da primeira porta lógica podendo se propagar através de caminhos múltiplos e, finalmente convergir para algum ponto (CHENG et al., 2008). No caso do exemplo, o efeito da transição na entrada da porta G1 pode propagar-se para G5 em dois diferentes caminhos. Como o caminho de propagação 1 é maior do que o caminho de propagação 2, causará um efeito de falha na saída 0-1-0.

Figura 2.3 – Se Caminho de propagação 1 > Caminho de propagação 2, o efeito da falha na NAND da saída seria 0-1-0.

Fonte: Elaborada pela autora.

### 3 Cell-Aware Test

O *Cell-Aware Test* ou CAT é uma metodologia de testes que tem como principal metodologia modelos de falhas baseados no leiaute (HAPKE et al., 2009). O resultado é um teste na perspectiva do leiaute, ou seja, o leiaute da célula é analisado, bem como os transistores, resistências e capacitâncias parasitas são analisadas. E, a partir de todas essas informações, os modelos das falhas são descritos para esse leiaute em específico. Sabendo-se disso, pode-se ter modelos de falhas diferentes, e até mesmo um número distinto de modelos de falhas para a mesma célula. Isso acontece porque, dependendo da forma como o leiaute é projetado, os valores das capacitâncias e resistências parasitas mudam, e as falhas podem ser determinadas de acordo com esses valores (HAPKE et al., 2009).

A primeira citação do CAT foi em Hapke et al. (2009), sua contribuição foi uma nova metodologia para detectado defeitos internos à célula. Isso porque estudos feitos para analisar os defeitos, que não estavam sendo cobertos pelos modelos de falhas atuais, mostraram que os defeitos internos às células eram os que estavam passando pelos testes sem serem detectados, gerando assim, uma necessidade de pesquisas mais aprofundadas para a resolução desse problema. A nova metodologia *Cell-Aware* foi avaliada para tecnologias de 90nm e 150nm em 1671 células de biblioteca, testado em 10 *designs* industriais reais com até 50 milhões de falhas. Os resultados experimentais mostraram, em média, um crescimento de 1,2% na cobertura de defeitos (HAPKE et al., 2009).

Figura 3.1 – Etapas do *Cell-Aware*.

Fonte: Elaborada pela autora.

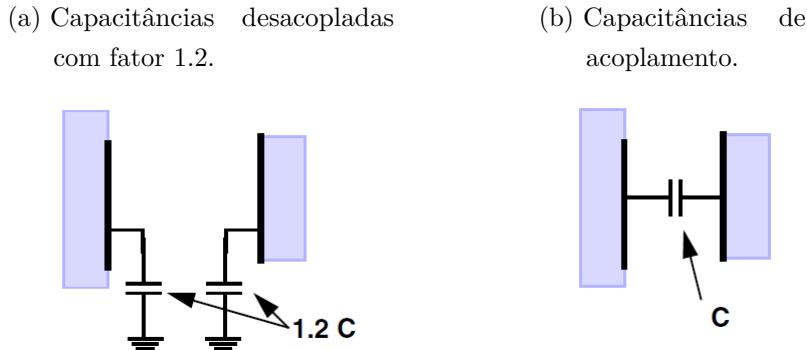

Para entender o *Cell-Aware Test* é necessário entender o fluxograma dessa metodologia. Na Fig. 3.1 é descrito o fluxograma do CAT, que começa com os dados do leiaute da célula que serão armazenados em um arquivo que contém os leiautes das bibliotecas. A esse arquivo dá-se o nome de *F1*. Em seguida, é feita a extração dos parâmetros desse leiaute, como resistências e capacitâncias parasitas. De acordo com os valores extraídos pode-se inferir quais locais são mais prováveis de haver falhas, conforme as regras do

*Cell-Aware*. Essas informações do leiaute são armazenadas em  $F2$ , os prováveis defeitos físicos são armazenados em  $F3$ . Com as informações das falhas, pode ser feita a ‘matriz de defeitos que ficará em  $F4$ . Depois da síntese do modelo de falhas, têm-se a análise de cobertura, e finalmente o CAM (*Cell-Aware Model*) em  $F5$  (HAPKE et al., 2014).

Para que o teste tenha uma eficiência alta é preciso que o modelo de falhas seja baseado no leiaute, isso porque quando baseia-se no leiaute os defeitos físicos são modelados com maior precisão (HAPKE et al., 2014). Para isso, a primeira etapa proposta pelo CAT é obter o leiaute da célula em que serão criados os modelos e armazená-los em um arquivo para a próxima etapa do fluxograma *Cell-Aware*.

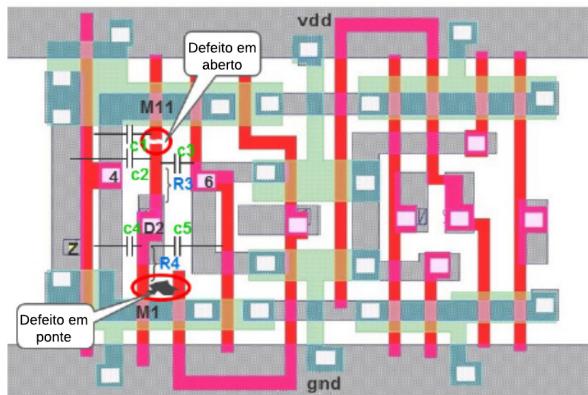

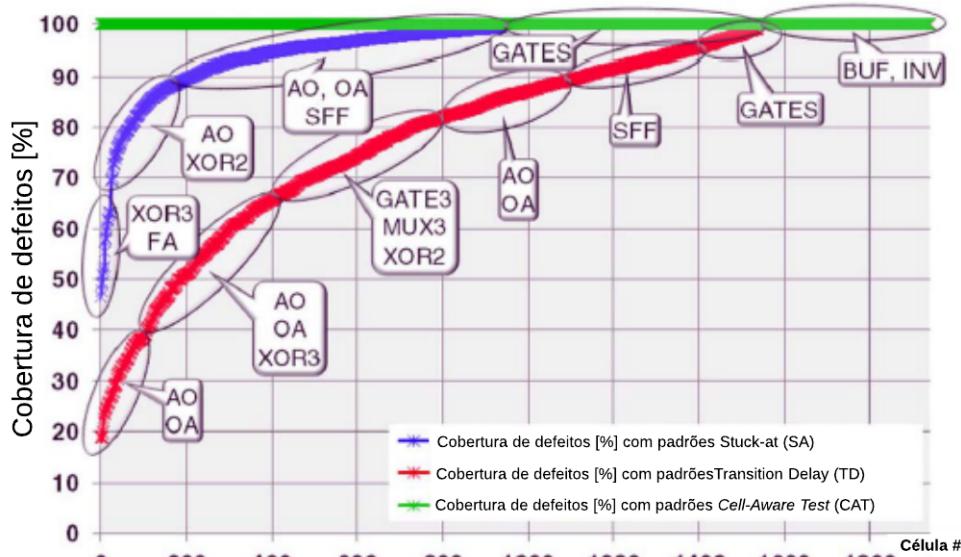

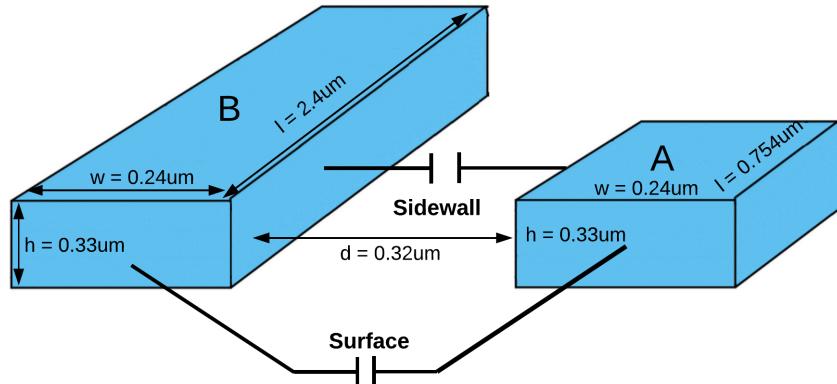

Na Figura 3.2 são mostrados exemplos de defeitos físicos modelados em falhas. Alguns dos defeitos são: **defeito em aberto** (*Open defect*), que na simulação é representado por altas resistências; e **defeito em ponte** (*Bridge defect*), que é representado por capacitâncias. No trabalho descrito em Hapke et al. (2014) não são apresentados os valores das resistências e capacitâncias que correspondem às falhas. Esses valores foram investigados baseado em outros artigos, e serão analisados no Capítulo 4.

Figura 3.2 – Leiaute da célula de um multiplexador.

Fonte: Adaptada de Hapke e Schloeffel (2012).

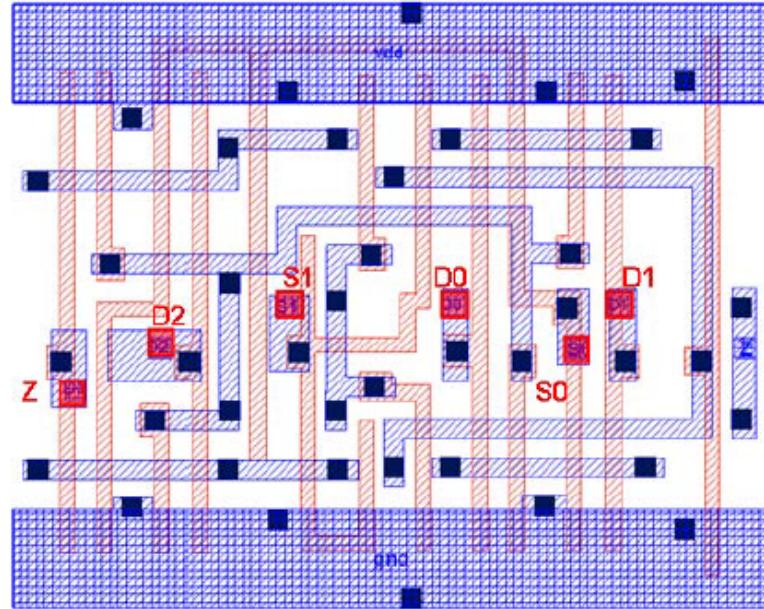

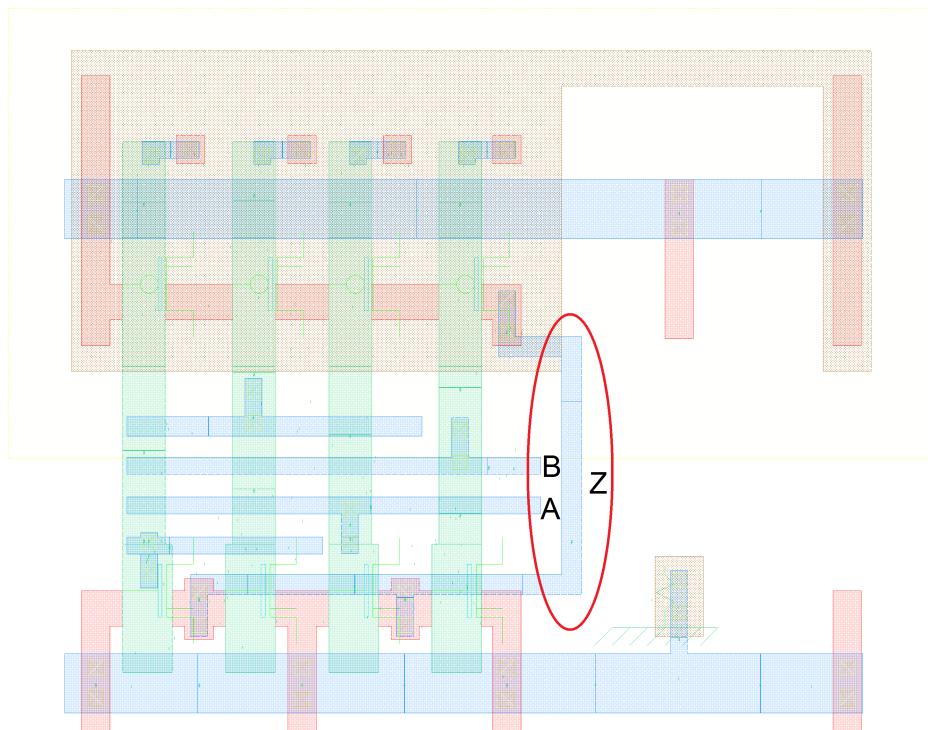

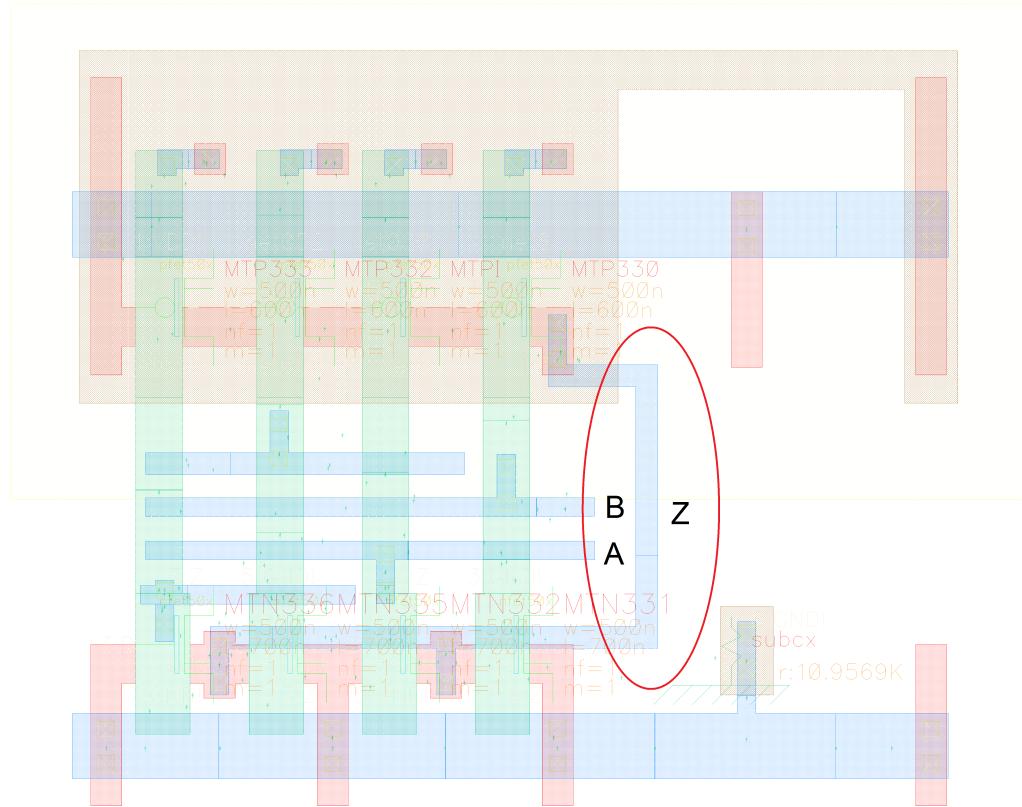

Na Figura 3.3 é representado um exemplo do arquivo em  $F1$ , que é o leiaute de um multiplexador de três entradas ( $D0, D1, D2$ ), dois seletores ( $S0, S1$ ) e a saída  $Z$ . Esse será o primeiro arquivo a ser usado para o fluxo do CAT.

Depois de examinar o leiaute ( $F1$ ) e analisar os possíveis defeitos que a célula possui, têm-se na Tabela 3.1 a lista de falhas consideradas em  $F2$  para o MUX31X4.

Por exemplo, sabendo que os seletores do multiplexador são  $S0$  e  $S1$ , as saídas desses seletores negadas serão dadas, respectivamente, por  $S0N$  e  $S1N$ . Sabendo disso, pode-se analisar a lista de falhas possíveis: analisando **d0** pode-se dizer que, é possível ocorrer uma falha em que a saída negada do seletor  $S0$ , dada por  $S0N$  esteja fixa em

Figura 3.3 – Leiaute da célula do multiplexador MUX31X4.

Fonte: Hapke et al. (2009).

Tabela 3.1 – Lista de defeitos

|                  |                 |                  |

|------------------|-----------------|------------------|

| d1 = S0N, gnd    | d17 = D0, gnd   | d33 = net38, D1  |

| d2 = S1N, gnd    | d18 = vdd, gnd  | d34 = net81, D0  |

| d3 = net65, gnd  | d19 = Z, net65  | d35 = net38, D0  |

| d4 = net57, gnd  | d20 = S1, S0N   | d36 = S1, S0     |

| d5 = net19, gnd  | d21 = S1N, S1   | d37 = D2, S1     |

| d6 = net81, gnd  | d22 = net65, S1 | d38 = S0, D1     |

| d7 = net38, gnd  | d23 = S0N, S0   | d39 = vdd, S0N   |

| d8 = net85, gnd  | d24 = net81, S1 | d40 = vdd, S1N   |

| d9 = net35, gnd  | d25 = S1, net38 | d41 = vdd, net65 |

| d10 = net31, gnd | d26 = D2, S1N   | d42 = D0, S0     |

| d11 = net69, gnd | d27 = net81, D0 | d43 = net38, vdd |

| d12 = Z, gnd     | d28 = net65, D2 | d44 = vdd, Z     |

| d13 = S1, gnd    | d29 = net38, S0 | d45 = vdd, S1    |

| d14 = S0, gnd    | d30 = S0N, D1   | d46 = vdd, S0    |

| d15 = D2, gnd    | d31 = net81, D1 | d47 = vdd, D2    |

| d16 = D1, gnd    | d32 = S0N, D0   | d48 = vdd, D1    |

GND. Este é um exemplo, os outros 47 defeitos seguem o mesmo exemplo, **dxx** é o nome do defeito; o primeiro termo antes da vírgula é a entrada, saída ou *net* onde está localizado o defeito; o termo após a vírgula é em que elemento o defeito está fixo. Por exemplo, o **d1** representa o defeito em que o seletor *S0N* está preso em **gnd**.

A partir dessa lista de defeitos em potencial têm-se 48 *netlists* adicionais, além da *netlist* sem defeitos, que é chamada de *golden netlist* (HAPKE et al., 2009). Cada

Tabela 3.2 – Matriz de Defeitos

| Input | d1 | d2 | d3 | d4 | ... | d41 | d42 | d43 | d44 | d45 | d46 | d47 | d48 |

|-------|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 00000 | -  | -  | -  | -  |     | -   | -   | -   | D   | -   | -   | -   | -   |

| 00001 | D  | D  | -  | -  |     | D   | D   | D   | -   | D   | D   | -   | -   |

| 00010 | -  | -  | -  | -  |     | -   | -   | -   | D   | -   | D   | -   | -   |

| 00011 | -  | D  | -  | -  |     | D   | -   | D   | -   | D   | -   | -   | -   |

| 00100 | -  | -  | -  | -  |     | -   | -   | -   | D   | D   | -   | -   | -   |

| 00101 | D  | -  | -  | -  |     | D   | D   | D   | -   | -   | D   | -   | -   |

| 00110 | -  | -  | -  | -  |     | -   | -   | -   | D   | D   | D   | -   | -   |

| 00111 | -  | -  | -  | -  |     | D   | -   | D   | -   | -   | -   | -   | -   |

| 01000 | -  | -  | -  | -  |     | -   | -   | -   | D   | -   | -   | -   | D   |

| ...   |    |    |    |    |     |     |     |     |     |     |     |     |     |

| 11111 | -  | -  | -  | -  |     | D   | -   | -   | -   | -   | -   | -   | -   |

uma das 49 *netlists* são simuladas, no entanto, como cada uma possui 5 bits de entrada, serão necessárias 32 simulações para cada *netlist*, totalizando 1568 simulações. As saídas das simulações são analisadas e comparadas com a saída *golden*. Se a saída para uma dada entrada for igual à resposta *golden* significa que a entrada não-detectou o defeito. Se a resposta for diferente à *golden* significa que a entrada expôs a falha, ou seja, que ela detectou a falha.

Durante a análise de todas as simulações, pode-se construir o que é denominado de **Matriz de Defeitos** (Tabela 3.2). A Matriz de Defeitos da célula é uma tabela que contém todas as 32 entradas possíveis da célula representadas nas **linhas** da matriz e, os 48 defeitos que são representados nas **colunas** na matriz. Por exemplo, na linha que tem a entrada '11111', essa entrada detecta (**D**), dentre outros, o defeito *d41* o qual é um curto-circuito entre a *net65* e *vdd* (HAPKE; SCHLOEFFEL, 2012).

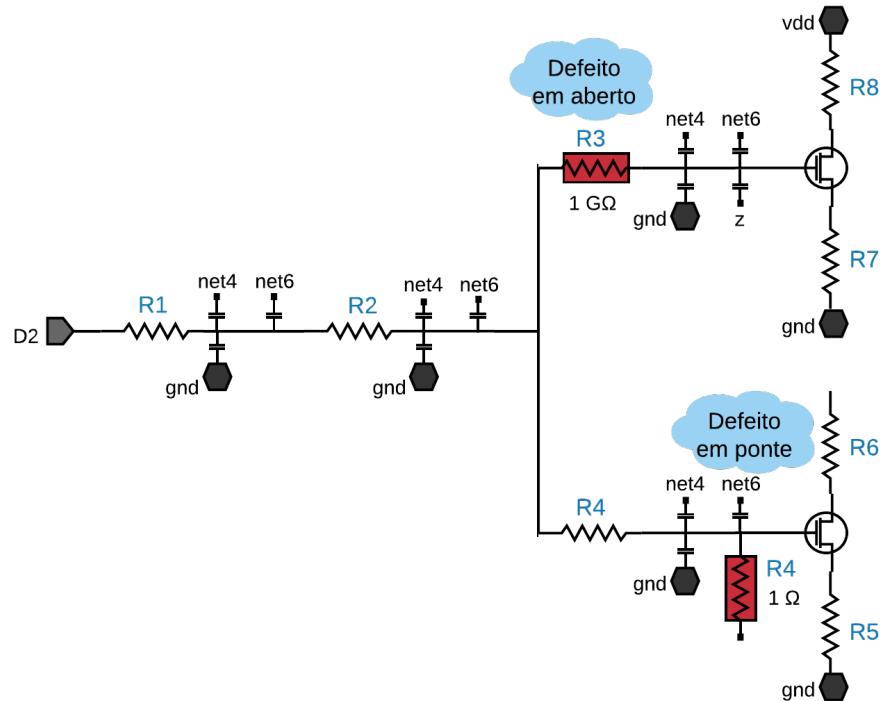

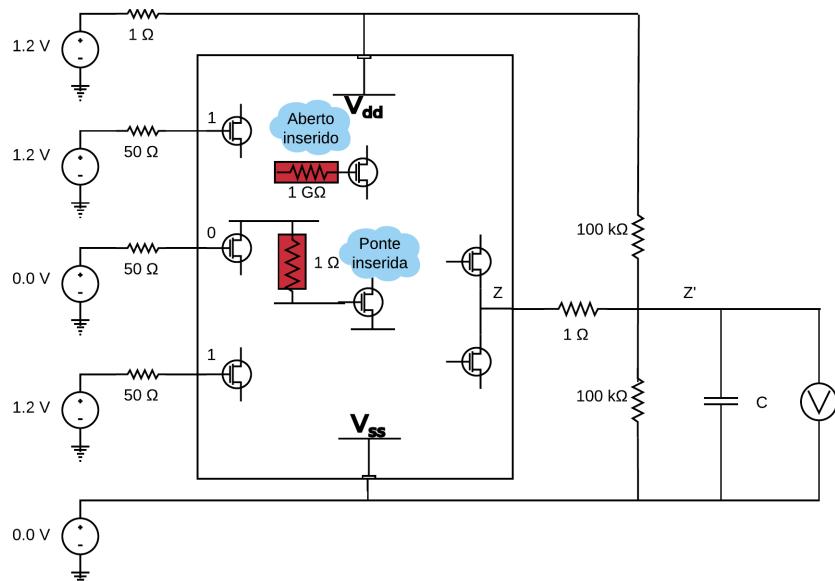

Na Figura 3.4 é ilustrada **uma parte** dos componentes (resistores, capacitâncias, entradas, transistores, VDD e GND) do MUX31X4. Além dos componentes que são do leiaute, a *netlist* contém os possíveis defeitos. Cada um dos defeitos é colocado por vez, um em cada netlist para que possa ser feita análise das saídas com cada defeito por vez. Os resistores que estão em vermelho são os defeitos que não são do leiaute, que foram colocados para simular defeitos físicos. Os outros elementos são extraídos do leiaute da célula que está sendo analisada.

Na Figura 3.5 pode-se ver um exemplo de como ficam os componentes e a alimentação das entradas em uma das simulações analógicas. Os elementos extraídos da *netlist*, incluindo objetos parasitas, são usados como entrada para a simulação analógica, em que cada defeito é simulado (HAPKE; SCHLOEFFEL, 2012). É possível observar na Figura 3.5 a entrada '101' com os defeitos em aberto e em ponte. Nas simulações analógicas, um defeito é considerado detectado se pelo menos uma das entradas resulte em uma saída

Figura 3.4 – Transistores extraídos da netlist.

Fonte: Adaptada de Hapke e Schloeffel (2012).

que desvia em mais do que 50% da sua tensão de alimentação VDD.

Figura 3.5 – Ambiente de simulação analógica.

Fonte: Adaptada de Hapke e Schloeffel (2012).

O processo de inserção das falhas com o SA-ATPG para análise das saídas é diferente para o CAT-ATPG. Como pode ser visto na Figura 3.6 o modelo de falhas *stuck-at-0* é modelado na entrada *D0* da célula MUX31X4 e a condição para que essa falha

seja observada na saída é  $D0 = 1$ ,  $S0 = 1$  e  $S1 = 1$ . Assim, o ATPG *stuck-at* tradicional que irá gerar os padrões só irá precisar dessa entrada para essa falha em específico (HAPKE et al., 2009). Ou seja, a condição de excitação da falha interna é colocada na entrada da célula. E o ATPG não precisará inserir deterministicamente outras entradas.

Figura 3.6 – Processo do ATPG normal.

Fonte: Adaptada de Hapke et al. (2009).

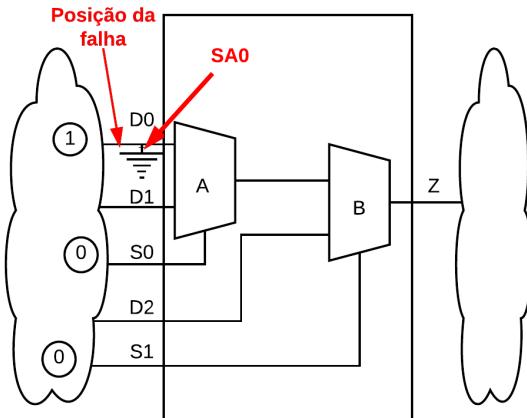

O processo de gerar padrões do CAT-ATPG para o mesmo multiplexador pode ser visto na Fig. 3.7. Neste caso, assume-se uma falha em ponte entre as nets *A* e *B* como está indicado no leiaute da figura (HAPKE et al., 2009).

A posição inicial para uma falha baseada no CAT é sempre a saída da porta. A condição para a excitação da falha e a sua propagação para a saída não tem relação com as entradas pré-definidas do ATPG (HAPKE et al., 2009). O ATPG aplica estritamente as condições necessárias nas entradas da porta da célula, como definido pelo modelo CAT correspondente (HAPKE et al., 2009).

Figura 3.7 – TPG para uma falha em ponte interna à célula.

Fonte: Adaptada de Hapke et al. (2009).

Assim, ao considerar uma falha em ponte  $B1$ , é necessário que as entradas sejam  $D0 = 1$ ,  $D2 = 1$ ,  $S0 = 1$  e  $S1 = 0$ . Isso significa que o CAT-ATPG forçou o valor de uma entrada a mais, no caso  $D2$ , unicamente com o objetivo de detectar uma possível falha em ponte  $B1$  (HAPKE et al., 2009). Ou seja, o que diferencia o CAT-ATPG do ATPG tradicional é a aplicação do padrão de forma determinística com a finalidade de detectar falhas internas à célula.

Depois de finalizada todas as simulações analógicas e de obter a matriz de defeitos, é possível fazer uma comparação dos resultados obtidos pelo CAT com os modelos de falhas *Stuck-At* e *Transition Delay* (HAPKE et al., 2014).

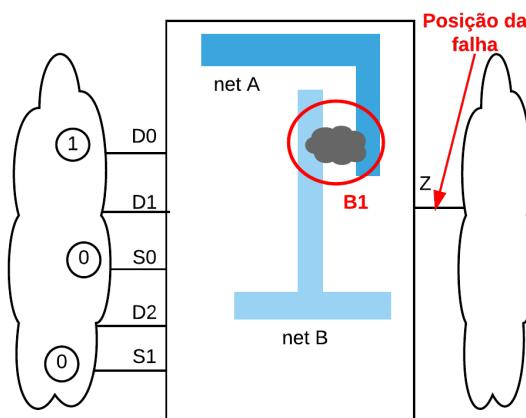

Na Figura 3.8 é apresentado o gráfico com relação entre as células e a cobertura de defeitos. O eixo horizontal representa as células da biblioteca, sendo numeradas de 1 a 1940. O eixo vertical indica a porcentagem de cobertura de defeitos da seguinte forma: a curva em azul é a cobertura de defeitos para as pontes, abertos e defeitos em transistores que são detectáveis, e que é conseguido usando apenas os padrões dos modelos de falhas *Stuck-At*; a curva em vermelho é a cobertura para os mesmos defeitos que são detectáveis, agora usando apenas os padrões dos modelos de falhas *Transistion Delay*; a curva em verde é a cobertura de defeitos em porcentagem quando são utilizados padrões baseados no CAT.

No gráfico da Figura 3.8 é mostrado que, para os padrões baseados em modelos *Stuck-At*, a cobertura de defeitos é menor do que 100% para cerca de 50% das células, e em algumas células a cobertura gira em torno de 46%. Mas a cobertura é menor quando se trata de padrões *Transition Delay*, em que aproximadamente 80% das células não alcançam os 100% de cobertura de defeitos e em torno de 200 células têm a cobertura de defeitos com menos de 50%, algumas células com apenas 20%, como por exemplo AO (AND-OR) e OA (OR-AND) (HAPKE et al., 2014). Ao fazer uma análise do gráfico observou-se que os modelos de falhas utilizados foram os do CAT, enquanto os padrões de testes aplicados foram os do *stuck-at*, *transition delay* e CAT, ou seja, se o CAT modela 30 modelos de falhas para um leiaute em específico, os padrões gerados a partir do modelo *stuck-at* deverão ser capazes de cobrir essas 30 falhas. Sendo que, os padrões baseados em *stuck-at* modelaram apenas 12 falhas no mesmo circuito. Assim, os padrões que foram gerados a partir de 12 falhas modeladas não seriam capazes de cobrir as 30 falhas do CAT. O mesmo acontece com o modelo de falhas *transition delay*, se ele modelar 16 falhas, os padrões irão cobrir essas 16 falhas. No gráfico os padrões CAT que modelaram 30 falhas geram padrões para cobrir essas 30 falhas; os padrões *stuck-at* que geram padrões pra 12 falhas devem cobrir 30 falhas; os padrões *transition delay* que geram padrões pra 16 falhas devem cobrir 30 falhas. O resultado parece injusto quando se fala da cobertura das falhas específicas do CAT.

Figura 3.8 – Cobertura de defeitos do CAT em comparação com *Stuck-At* e *Transition Delay*.

Fonte: Adaptada de Hapke et al. (2014).

Além disso, no desenvolvimento desta pesquisa sobre os conceitos do *Cell-Aware Test*, surgiram dúvidas em relação aos parâmetros que seriam usados para estabelecer os valores de resistência e capacitâncias correspondentes a cada modelagem de falhas. Como os modelos de falhas são baseado no leiaute da célula, e cada leiaute da mesma célula pode ser diferente, com ligações feitas de formas e distâncias distintas, a lista de defeitos será diferente, e a forma de modelar falhas também. Os valores de resistências e capacitâncias para a simulação analógica serão então distintos. Não fica claro, nos exemplos expostos nos artigos sobre o CAT publicados nos últimos anos, que valores de parâmetros são usados. Por isso, para este trabalho foram feitos estudos mais aprofundados para saber como podem ser definidos os parâmetros. Na próxima seção, ir-se-á descrever alguns conceitos que serão base para a determinação de quais locais do leiaute são mais possíveis probabilisticamente de ocorrerem falhas. Tal estudo é de grande importância, pois pelo modelo CAT é possível o estabelecimento de inúmeros pontos de falhas tornando a tarefa do ATPG impraticável.

## 4 Área Crítica

Jacomet e Guggenbuhl (1993) relataram que modelos clássicos de falhas, como o modelo *Stuck-At*, não consideram o leiaute da célula. Além disso, não tem relação com a geometria do leiaute do circuito e, em alguns casos, não são baseados na tecnologia de fabricação. Outro fator importante é que, com a diminuição dos circuitos integrados e o consequente aumento na densidade de transistores, as falhas em ponte estão se tornando cada vez mais relevantes (JACOMET; GUGGENBUHL, 1993). Esses problemas foram analisados e soluções estudadas para que os modelos de falhas cobrissem o maior número de defeitos possíveis. Com isso, chegou-se à modelos de falhas que fossem baseados no estudo da área crítica do leiaute.

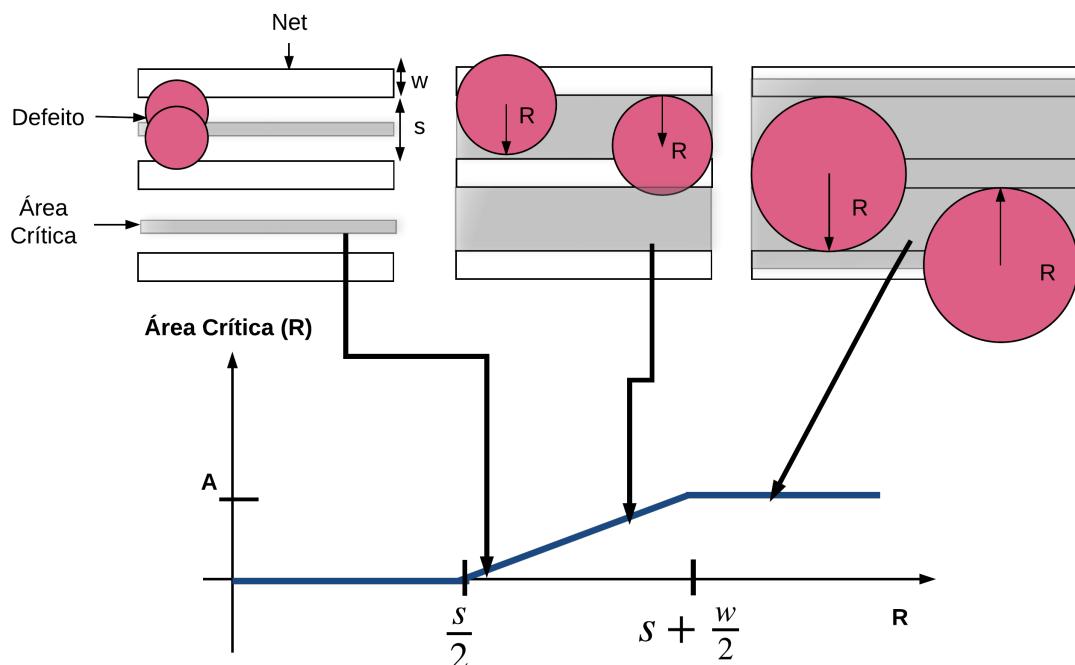

Nos anos seguintes, Bubel et al. (1995a) definiram o conceito de Área Crítica como sendo a probabilidade de uma dada área do leiaute conter defeitos, ou seja, quanto maior o defeito e menor o espaçamento entre as nets, maior a probabilidade dele causar uma falha (BUBEL et al., 1995a).

Figura 4.1 – Função da Área Crítica (BUBEL et al., 1995a).

Fonte: Elaborada pela autora.

Na Figura 4.1 é mostrado o gráfico da função Área Crítica ( $R$ ), em que  $R$  é o valor do raio do defeito. Quando se tem duas interconexões com distância  $s$  e largura  $w$ , analisa-se qual a probabilidade de um defeito de raio  $R$  entre as nets causar uma

falla (BUBEL et al., 1995a). Na primeira parte da figura nota-se que os defeitos tem o menor raio, mas que ainda criam uma área crítica. Os demais defeitos tem raio maior, e quanto maior o raio do defeito, maior a área crítica. Quando os defeitos circulares tem um diâmetro ( $x = 2R$ ) menor do que espaçamento ( $s$ ) entre as interconexões eles não conseguem conectar os eletricamente e a probabilidade de causar uma falha é nula. Quando o diâmetro é maior do que o espaçamento, a probabilidade aumenta de acordo com essa variação de diâmetro.

Formalmente, a probabilidade de área crítica,  $h(x)$ , pode ser definida como uma função do diâmetro do defeito e da distância entre as interconexões. O cálculo que é feito conforme Figura 4.1 é dado pela equação Eq. 4.1.

$$h(x) = \begin{cases} 0, & \text{para } 0 < x \leq s \\ \frac{x-s}{s+w}, & \text{para } s \leq x \leq 2s + w \\ 1, & \text{para } (2s + w) \leq x \end{cases} \quad (4.1)$$

em que  $w$  é a largura da interconexão,  $s$  é o espaçamento entre duas interconexões,  $x$  é o diâmetro do defeito e a função  $h(x)$  é a sensibilidade à defeito, ou seja, a probabilidade do defeito ocasionar uma falha (ALLAN; WALTON, 1998). As funções de sensibilidade são representações da área crítica do leiaute ou a região a qual o defeito de um diâmetro  $x$  provavelmente causará uma falha.

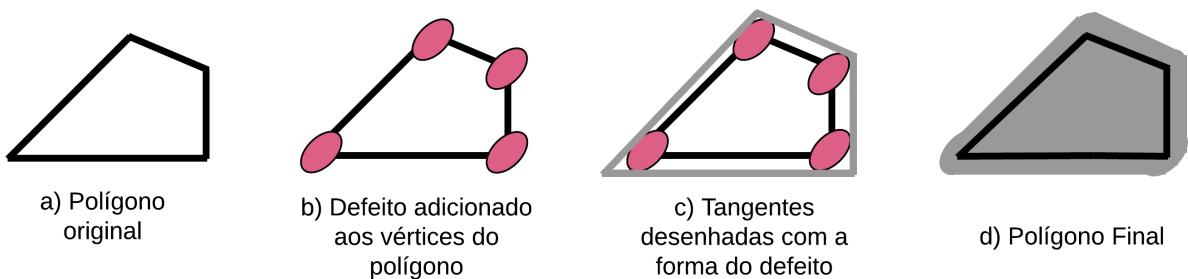

Figura 4.2 – Método de expansão de polígonos para defeitos convexos arbitrários (ALLAN; WALTON, 1997a).

Fonte: Elaborada pela autora.

Em Allan e Walton (1997a) completaram o conceito de área crítica ao conceituar que ela pode ser encontrada pela interseção de regiões expandidas da forma geométrica. Na Figura 4.2 é mostrado um polígono de geometria arbitrária que é expandido através dos defeitos inseridos em suas vértices. Nela pode-se observar que o primeiro polígono é o original, o segundo está com defeitos elípticos em seus vértices, para que, na próxima etapa possam haver a expansão do polígono e, na quarta e última etapa pode ser vista a expansão desse polígono em área crítica. Esse método é importante pois nem todas as

interconexões ficam paralelas, então é necessário expandir essa áreas e verificar quando elas se cruzam. Quando isso acontecer, essa será considerada área crítica (Figura 4.3).

Figura 4.3 – Dinâmica do algoritmo que computa a Área Crítica (BUBEL et al., 1995a).

Fonte: Elaborada pela autora.

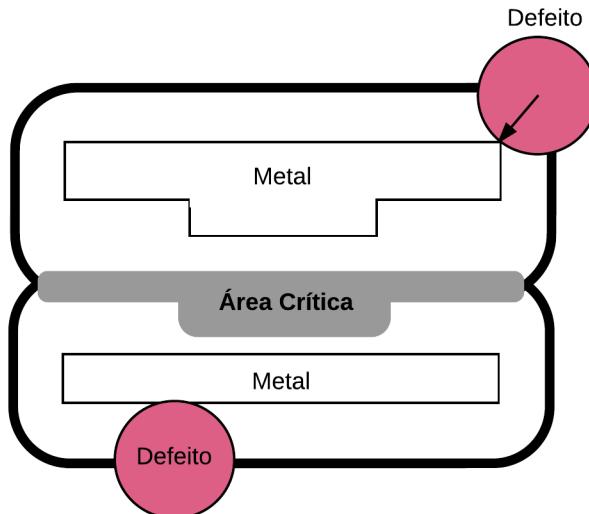

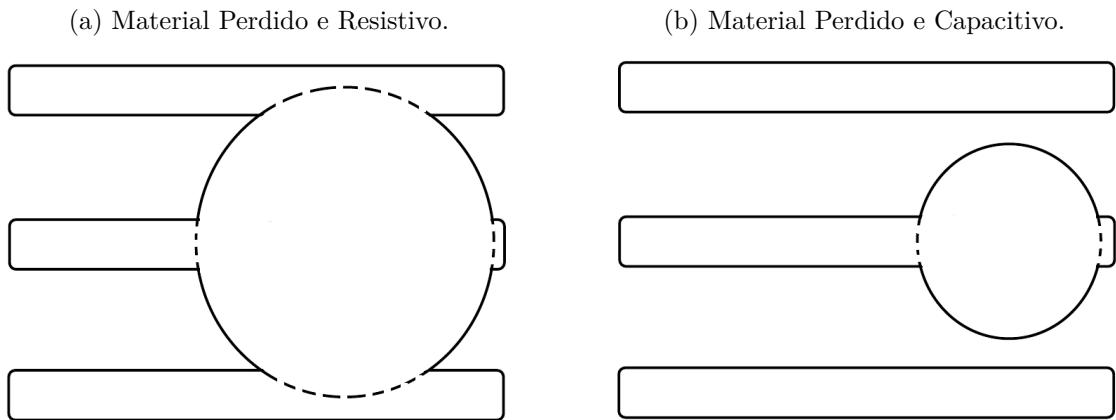

Em Allan e Walton (1998) foram definidos os conceitos de **Material Extra ou Perdido** e **Falha Resistiva ou Capacitiva**, os quais serão conceituados a seguir.

**Falhas causadas por Material Extra:** é quando um defeito físico é um partícula a mais no circuito integrado podendo causar um curto-circuito entre interconexões (Figuras 4.4a e 4.4b) (BUBEL et al., 1995a).

Figura 4.4 – Material Extra (ALLAN; WALTON, 1998).

(a) Material Extra e Resistivo.

(b) Material Extra e Capacitivo.

Fonte: Elaborada pela autora.

**Falhas causadas por Material Perdido:** é quando o defeito físico causa perda de material do circuito integrado. Esse fato ocorre com menos frequência mas também é

objeto de estudo. Esse tipo de defeito físico acaba fazendo com que o material do CI seja danificado com a perda de material, e consequentemente, pode causar o mal funcionamento do circuito (Figuras 4.5a e 4.5b) (BUBEL et al., 1995a).

Figura 4.5 – Material Perdido (ALLAN; WALTON, 1998).

Fonte: Elaborada pela autora.

**Falhas Resistivas:** são os defeitos que causam um curto-circuito entre duas interconexões distintas, como pode ser visto na Figuras 4.4a e 4.5a. Essas falhas podem ser modeladas eletricamente por resistores de baixo valor, para simular o curto, conectados entre as interconexões (ALLAN; WALTON, 1998).

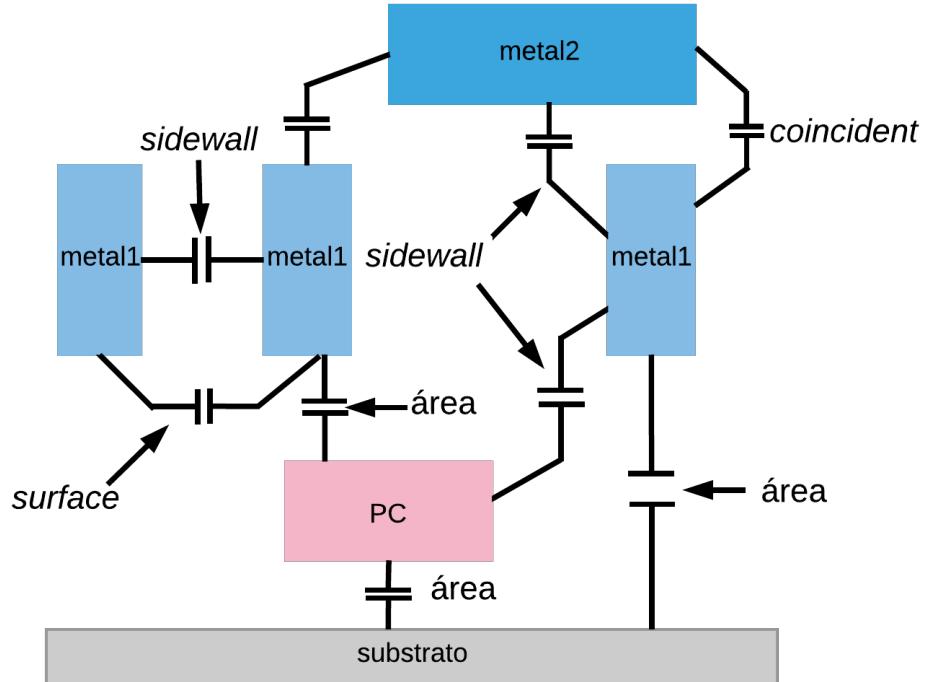

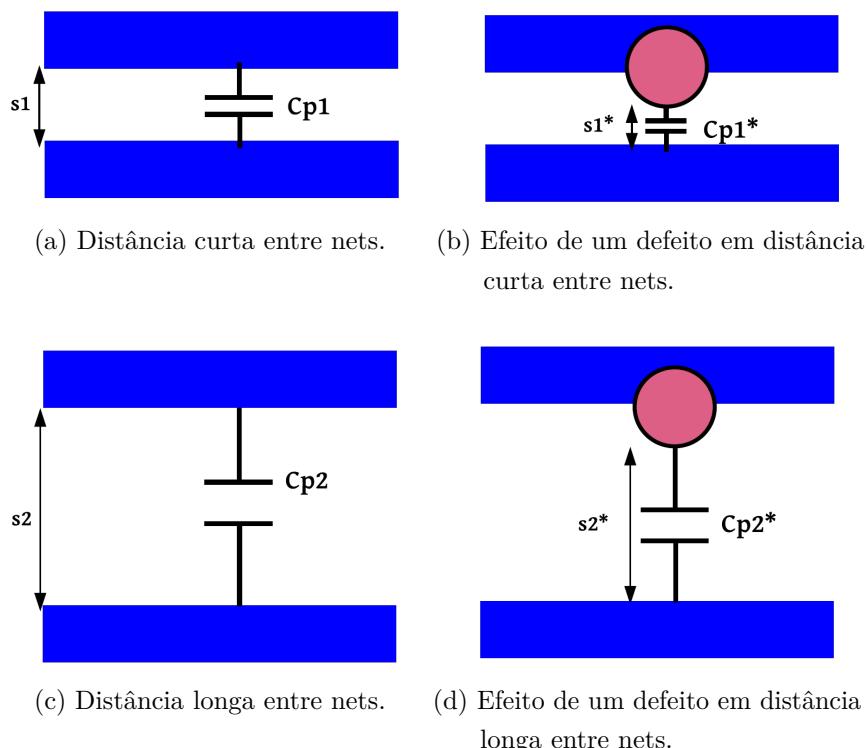

**Falhas Capacitivas:** são os defeitos que não chegam a conectar as interconexões eletricamente, mas encurtam a distância entre elas. Essa representação pode ser vista na Figuras 4.4b e 4.5b. Essa distância reduzida pode ser representada por um capacitor. As falhas capacitivas são difíceis de se detectar e podem causar falhas de *transition delay*. O ponto principal deste trabalho é calcular a área crítica de acordo com os cálculos propostos no próximo capítulo. Esses cálculos são necessário para analisar o quanto os elementos parasitas poderão interferir no leiaute da célula.

## 5 Cálculo de Área Crítica baseado no Leiaute da Célula

Gkatziani et al. (2007) abordaram o problema dos modelos de falhas que usaram somente o conceito de área crítica para criar seus modelos baseados em leiaute. Eles relataram que os métodos tradicionais de cálculo de área crítica relacionavam a proximidade e o tamanho das interconexões no cálculo do tamanho do defeito, mas não indicavam a contribuição de pontes induzidas por defeitos aleatórios. Nesse artigo foi mostrado como capacitâncias de acoplamento podem ser inseridas para o cálculo de área crítica, até mesmo quando estão em níveis de metal diferentes (GKATZIANI et al., 2007).

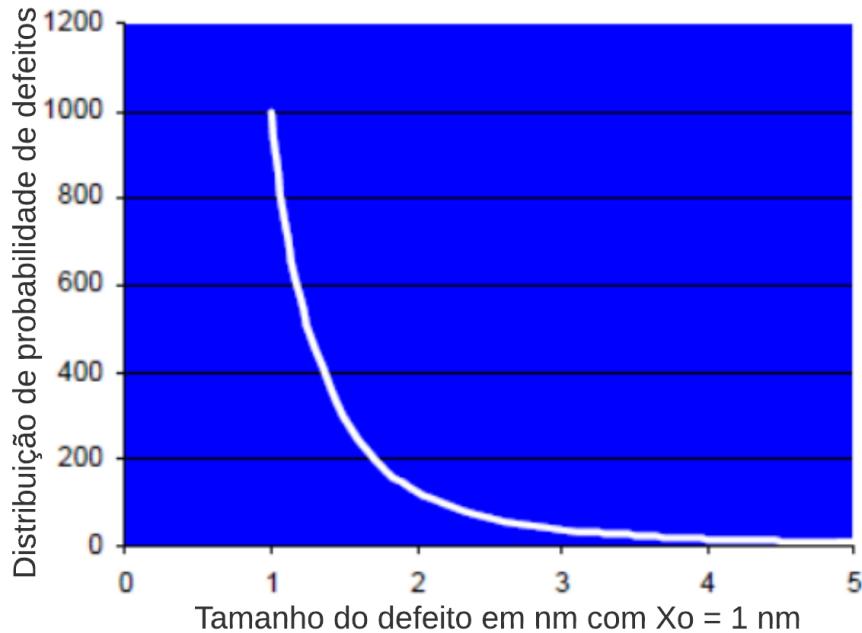

A análise da área crítica é o ponto de partida para identificar pontos do circuito integrado em que os defeitos físicos tem maior probabilidade de causar uma falha. Para isso, calcula-se a probabilidade de ocorrência um defeito físico em um circuito integrado. Sabe-se que o processo de fabricação é minuciosamente feito em uma sala limpa, então, a possibilidade de uma partícula interferir nesse processo é pequena, mas não inexistente. O gráfico da Figura 5.1 ilustra essa afirmativa. Nela, é mostrada a distribuição de probabilidade para o tamanho do defeito inicial dado por  $X_0 = 1nm$  e, observa-se que quanto maior o defeito, menor a probabilidade dele ocorrer em um circuito integrado. Enquanto que, quanto menor a partícula, maior a probabilidade dela interferir no processo de fabricação do CI.

A fundamentação do gráfico da Figura 5.1 é dada pela Eq. 5.1 (GKATZIANI et al., 2007).

$$f(x) = \frac{(p-1)x_0^{(p-1)}}{x^p}, \quad \text{para } x_0 \leq x \leq \infty \quad (5.1)$$

em que  $x$  é o diâmetro do defeito, sendo  $p$  dado pelo ITRS Roadmap e  $f(x)$  é a **função densidade de probabilidade de defeito** para um dado tamanho de defeito.

Para analisar os tamanhos dos defeitos, a integral de  $f(x)$  é calculada, como pode ser visto na Eq. 5.2. A equação a seguir será satisfeita se  $p \neq 1$  ou  $2$ .

$$\int_{x_0}^{\infty} f(x) dx = \int_{x_0}^{\infty} \frac{(p-1)x_0^{(p-1)}}{x^p} dx = \frac{(p-1)x_0^{(p-1)}}{-(p-1)} x^{-(p-1)} \Big|_{x_0}^{\infty} = 1 \quad (5.2)$$

Para simplificar o entendimento dos cálculo da área crítica associado às capacitâncias de acoplamento, iremos dividir em três partes: **Função Densidade de Probabi-**

Figura 5.1 – Distribuição de probabilidade para o tamanho do defeito

Fonte: Adaptada de Gkatziani et al. (2007).

**Lidade do Defeito, Área Crítica e Contribuição dos defeitos em interconexões paralelas.**

## 5.1 Função Densidade de Probabilidade do Defeito

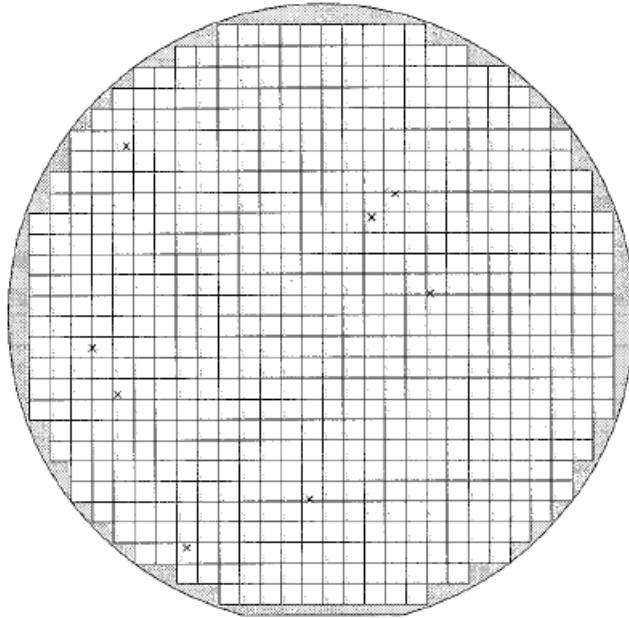

O primeiro dado que deve ser levado em consideração é a densidade de defeitos dada pela tecnologia (GKATZIANI et al., 2007). Para um *wafer* específico de uma dada tecnologia, o rendimento  $Y$  é calculado usando o mapa do *wafer*, que é ilustrado na Figura 5.2 (HESS; WEILAND, 1998).

O cálculo do rendimento é dado pelo número de chips que passam pelo processo de testes, ou seja, que não estão defeituosos, e pelo número total de chips (HESS; WEILAND, 1998).

$$Y = \frac{\text{nº de chips não defeituosos}}{\text{nº total de chips}} \quad (5.3)$$

Baseado na área do chip  $A$ , o valor da densidade de defeitos  $D$  pode ser calculado usando a Eq. 5.4.

$$D = \frac{1 - Y}{A} \quad (5.4)$$

Figura 5.2 – Wafer contendo 648 chips.

Fonte: Hess e Weiland (1998).

Considera-se que a Distribuição de Defeitos é dada pela multiplicação da densidade de defeitos de uma dada tecnologia,  $D_0$ , e a função densidade de probabilidade de defeitos  $f(x)$ , resultando assim, na Eq. 5.5.

$$F(x) = D_0 f(x) \quad (5.5)$$

Concluída a primeira parte dos equacionamentos, o próximo conceito é o da **Área Crítica**.

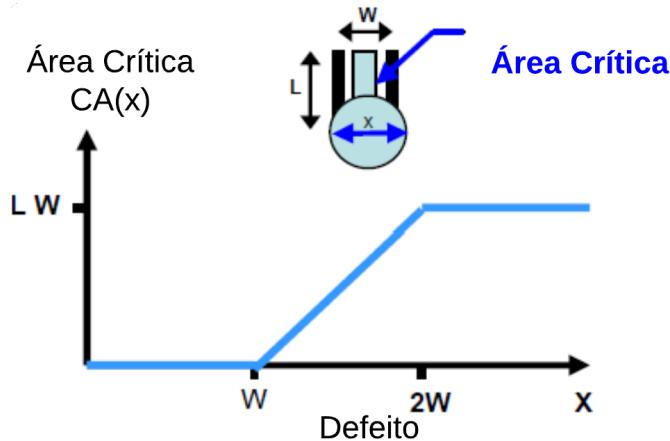

## 5.2 Área Crítica

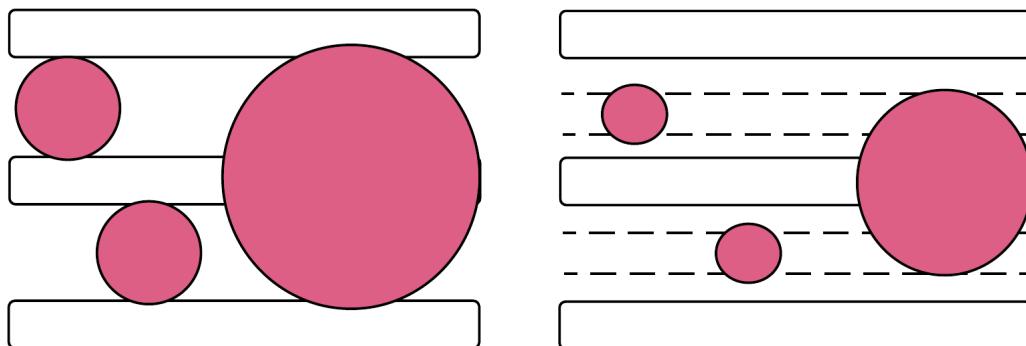

Para determinar a área crítica, analisam-se duas interconexões adjacentes com tamanho  $L$  e espaçamento entre elas  $W$ , obtendo assim as funções da Área Crítica, dada pela Eq. 5.6 e é ilustrada na Figura 5.3.

Na Fig. 5.3 é representado um gráfico da função da área crítica,  $CA(x)$ . Nessa função a área crítica é nula quando o diâmetro  $x$  é menor do que a distância  $W$  entre as interconexões. Já quando a diâmetro é entre  $W$  e  $2W$  há a possibilidade de conexão, então a área crítica é dada por  $Lx - LW$ . E, quando o diâmetro do defeito é igual ou maior do que  $2W$  a área crítica é  $LW$ .

$$CA(x) = \begin{cases} 0, & \text{para } 0 \leq x \leq W \\ Lx - LW, & \text{para } W < x < 2W \\ LW, & \text{para } x \geq 2W \end{cases} \quad (5.6)$$

Figura 5.3 – Área Crítica para um defeito de diâmetro  $x$ .

Fonte: Adaptada de Gkatziani et al. (2007)

A partir da Eq. 5.6 pode-se calcular o número de defeitos que se pode ter no leiaute, incluindo no cálculo a densidade de defeito,  $D_0$ , e a função densidade de probabilidade de um tamanho de defeito,  $f(x)$ . Para essa análise serão consideradas duas interconexões paralelas, então,  $F(x)$ , que é igual a  $D_0 f(x)$ , é a **distribuição do tamanho do defeito**, e a unidade de  $F(x)$  é dada em defeitos por unidade de área. Se forem multiplicados o valor de  $F(x)$  pela área crítica e integrado o defeito de tamanho  $x$ , tem como resultado a **Contribuição de defeitos para o par de interconexões** (GKATZIANI et al., 2007).

### 5.3 Contribuição de defeitos em interconexões paralelas

Considerando  $D_{LW}$  como sendo a contribuição de defeitos para duas interconexões paralelas, pode-se introduzir os conceitos anteriores de área crítica, densidade de defeitos e função densidade de probabilidade de defeitos em uma integral, obtendo-se assim  $D_{LW}$  como pode ser visto na Eq. 5.7:

$$D_{LW} = \int_0^\infty CA(x) D_0 f(x) dx \quad (5.7)$$

Desenvolvendo os termos da Eq. 5.7 em soma de integrais para as três diferentes possibilidades de áreas críticas:

$$D_{LW} = \int_0^W 0 D_0 \frac{(p-1) x_0^{(p-1)}}{x^p} dx \quad (5.8)$$

$$+ \int_W^{2W} (Lx - LW) D_0 \frac{(p-1) x_0^{(p-1)}}{x^p} dx$$

$$+ \int_{2W}^\infty LW D_0 \frac{(p-1) x_0^{(p-1)}}{x^p} dx$$

Resolvendo o primeiro termo da Eq. 5.8 tem-se o resultado da integral:

$$\int_0^W 0D_0 \frac{(p-1)x_0^{(p-1)}}{x^p} dx = 0$$

Ao resolver o segundo termo da Eq. 5.8 tem-se:

$$\begin{aligned} & \int_W^{2W} (Lx - LW) D_0 \frac{(p-1)x_0^{(p-1)}}{x^p} dx \\ &= \int_W^{2W} (Lx) D_0 \frac{(p-1)x_0^{(p-1)}}{x^p} dx - \int_W^{2W} (LW) D_0 \frac{(p-1)x_0^{(p-1)}}{x^p} dx \end{aligned} \quad (5.9)$$

Para o primeiro termo da Eq. 5.9, o resultado é:

$$\int_W^{2W} (Lx) D_0 \frac{(p-1)x_0^{(p-1)}}{x^p} dx \quad (5.10)$$

Desenvolvendo a Eq. 5.10:

$$\begin{aligned} &= LD_0 \int_W^{2W} \frac{(p-1)x_0^{(p-1)}}{x^{(p-1)}} dx \\ &= -LD_0 (p-1) x_0^{(p-1)} \left( \frac{1}{(p-2)x^{(p-2)}} \right) \Big|_W^{2W} \\ &= -LD_0 (p-1) x_0^{(p-1)} \left( \frac{1}{(p-2)(2W)^{(p-2)}} \right) + LD_0 (p-1) x_0^{(p-1)} \left( \frac{1}{(p-2)W^{(p-2)}} \right) \\ &= LD_0 (p-1) x_0^{(p-1)} \left( \frac{1}{(p-2)} \right) \left( \frac{1}{W^{(p-2)}} \right) \left( 1 - \frac{1}{2^{(p-2)}} \right) \end{aligned}$$

Para o segundo termo da Eq. 5.9 temos:

$$- \int_W^{2W} (LW) D_0 \frac{(p-1)x_0^{(p-1)}}{x^p} dx \quad (5.11)$$

Desenvolvendo a Eq. 5.11:

$$\begin{aligned} &= -LWD_0 (p-1) x_0^{(p-1)} \left( \frac{1}{-(p-1)x^{(p-1)}} \right) \Big|_W^{2W} \\ &= LWD_0 x_0^{(p-1)} \left( \frac{1}{x^{(p-1)}} \right) \Big|_W^{2W} \end{aligned}$$

$$\begin{aligned}

&= LWD_0 x_0^{(p-1)} \left( \frac{1}{(2W)^{(p-1)}} - \frac{1}{W^{(p-1)}} \right) \\

&= -LWD_0 x_0^{(p-1)} \left( \frac{1}{W^{(p-1)}} \right) \left( 1 - \frac{1}{2^{(p-1)}} \right)

\end{aligned}$$

Para o terceiro termo da Eq. 5.8 tem o resultado:

$$\int_{2W}^{\infty} LWD_0 \frac{(p-1)x_0^{(p-1)}}{x^p} dx \quad (5.12)$$

Desenvolvendo a Eq. 5.12

$$\begin{aligned}

&= LWD_0 (p-1) x_0^{(p-1)} \left( \frac{-1}{(p-1)x^{(p-1)}} \right) \Big|_{2W}^{\infty} \\

&= LWD_0 (p-1) x_0^{(p-1)} \left( \frac{1}{(p-1)(2W)^{(p-1)}} \right)

\end{aligned}$$

Considerando os resultados anteriores, então:

$$D_{LW} = 0 + \int_W^{2W} (Lx - LW) D_0 \frac{(p-1)x_0^{(p-1)}}{x^p} dx + \int_{2W}^{\infty} LWD_0 \frac{(p-1)x_0^{(p-1)}}{x^p} dx \quad (5.13)$$

$$\begin{aligned}

&= LD_0 (p-1) x_0^{(p-1)} \left( \frac{1}{(p-2)} \right) \left( \frac{1}{W^{(p-2)}} \right) \left( 1 - \frac{1}{2^{(p-2)}} \right) \\

&\quad - LWD_0 x_0^{(p-1)} \left( \frac{1}{W^{(p-1)}} \right) \left( 1 - \frac{1}{2^{(p-1)}} \right) \\

&\quad + LWD_0 x_0^{(p-1)} \left( \frac{1}{(2W)^{(p-1)}} \right) \\

\\

D_{LW} &= LD_0 x_0^{(p-1)} \left( \frac{1}{W^{(p-2)}} \right) \left[ (p-1) \left( \frac{1}{(p-2)} \right) \left( 1 - \frac{1}{2^{(p-2)}} \right) - \left( 1 - \frac{1}{2^{(p-1)}} \right) + \left( \frac{1}{2^{(p-1)}} \right) \right] \quad (5.14)

\end{aligned}$$

De acordo com o ITRS (*International Technology Roadmap for Semiconductors*), o valor de  $p$  mais comum de ser usado para todas as camadas é de  $p = 3$ , então, substituindo os valores de  $p$  na Eq. 5.14 tem-se:

$$D_{LW} = LD_0 x_0^2 \left( \frac{1}{W} \right) \left[ \left( 2 \cdot \frac{1}{1} \cdot \frac{1}{2} \right) - \left( \frac{3}{4} \right) + \left( \frac{1}{4} \right) \right] = LD_0 x_0^2 \left( \frac{1}{W} \right) \left[ 1 - \left( \frac{3}{4} \right) + \left( \frac{1}{4} \right) \right]$$

$$D_{LW} = LD_0x_0^2 \left( \frac{1}{W} \right) \left[ \frac{1}{4} + \left( \frac{1}{4} \right) \right] = LD_0x_0^2 \left( \frac{1}{W} \right) \left[ \frac{1}{2} \right] = \frac{LD_0x_0^2}{2W}$$

Então, tem-se o seguinte resultado final para  $D_{LW}$ :

$$D_{LW} = \frac{LD_0x_0^2}{2W} \quad (5.15)$$

Ao obter  $D_{LW}$  resolve-se o cálculo da contribuição dos defeitos em interconexões paralelas. Para obter os parâmetros de resistências e capacitâncias para as interconexões de cada nível de metal, é necessário saber as propriedades de *timing*. As capacitâncias de acoplamento entre as interconexões são os parâmetros que precisam ser extraídos (GKATZIANI et al., 2007). A capacitância de acoplamento é dada pela Eq. 5.16:

$$C = \frac{\varepsilon_R \varepsilon_0 L h}{W} \quad (5.16)$$

em que  $L$  e  $W$ , que foram vistos na Figura 5.3, dados pelo comprimento e pela distância entre as interconexões, respectivamente, e  $h$  é dado pela altura das interconexões no metal. Nessa equação  $\varepsilon_0$  é o valor do dielétrico no vácuo e  $\varepsilon_R$  é a constante dielétrica do material entre as duas interconexões. Para o dióxido de silício o  $\varepsilon_0$  é aproximadamente 3,9 (GKATZIANI et al., 2007). Substituindo a Eq. 5.16 em 5.15 tem-se o resultado de  $D_{LW}$  na Eq. 5.17:

$$D_{LW} = \frac{LD_0x_0^2}{2W} = C \times \left( \frac{D_0x_0^2}{2\varepsilon_R \varepsilon_0 h} \right) \quad (5.17)$$

Com o cálculo da Contribuição de Defeitos  $D_{LW}$  associadas às capacitâncias de acoplamento, pode-se precisar em quais locais se tem a maior probabilidade de defeitos causarem falhas, ou seja, ao se fazer a análise do leiaute e verificar todos os pontos de capacitâncias, tem-se modelos de falhas específicos para a célula em estudo.

# 6 Processo de Fabricação CMOS

Como o processo de fabricação de um CI geralmente se utiliza diferentes camadas, é necessário saber como ocorre o processo de fabricação do CMOS e como as capacitâncias parasitas surgem durante esse processo. Esse entendimento faz-se necessário pois, através dele, obter-se-á os conceitos sobre como as capacitâncias são formadas entre os metais e o isolante.

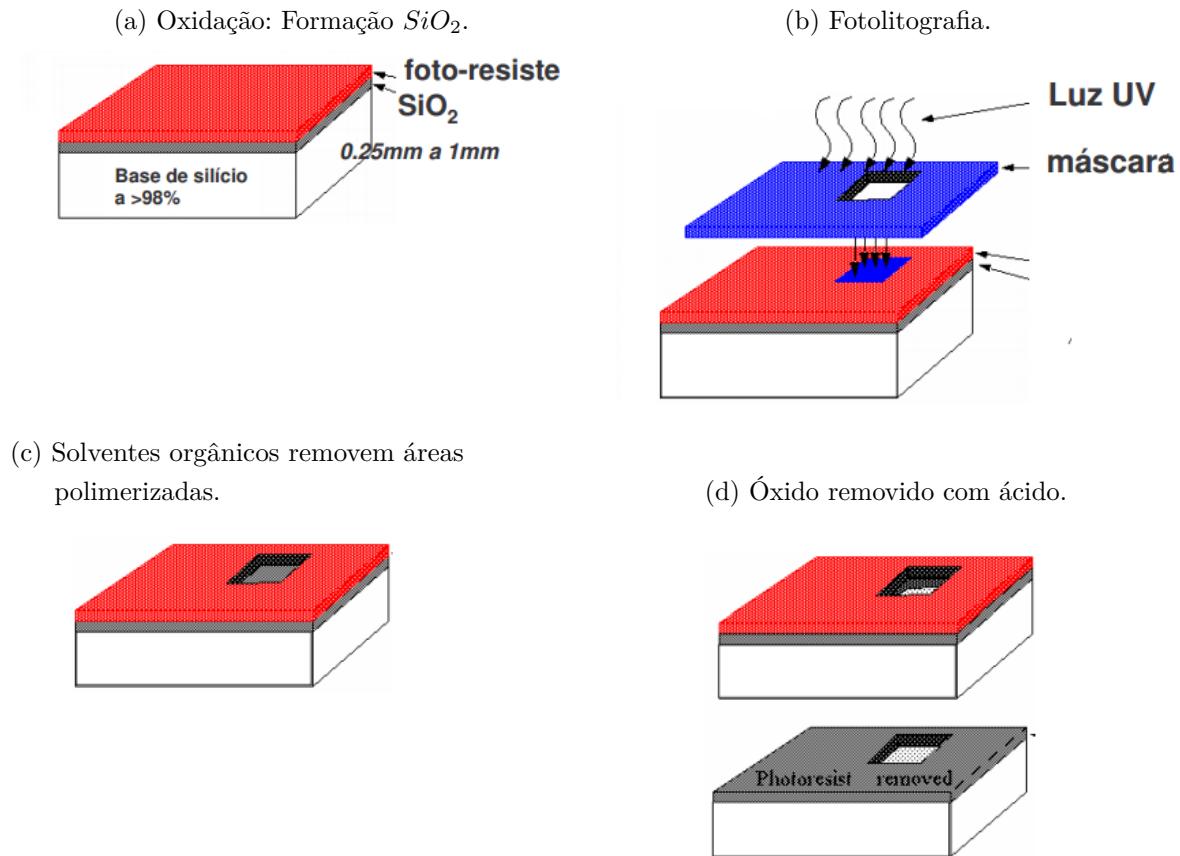

## 6.1 Processo de Fotolitografia, Criação de *n-well* e Crescimento do FOX

Os circuitos CMOS são fabricados em uma *wafer* de silício. Esses *wafers* são fatias circulares de silício de cristal único, com pureza maior do que 98%, como pode ser visto na Fig. 6.1a, e são levemente dopados (SILVA, 2007). O substrato é comum a todos os dispositivos. Considerando um substrato dopado com impurezas do tipo p, para produzir transistor de canal P, que requerem substrato do tipo n, faz-se necessário dopar uma região com impurezas do tipo n.

Em seguida, é feito o processo de fotolitografia, que é o processo pelo qual áreas predefinidas são mascaradas (protegidas). Na fotolitografia, processo que pode ser visto na Fig. 6.1b, o *wafer* é coberto por um polímero denominado *photoresist*. Este material é posteriormente sensibilizado pela incidência de luz, ou seja, se torna sensível (positivo) ou resistente (negativo) à remoção por um solvente orgânico (SILVA, 2007).

Após a ação dos solventes ter-se-á regiões com material exposto (Fig. 6.1c), que pode ser removido por ácidos (Fig. 6.1d). Nesta etapa o fotoresiste é removido e o substrato fica exposto, pronto para se criar o *n-well* (poço n). O fotoresiste é removido pois poderia derreter no processo de implante (SILVA, 2007).

Figura 6.1 – Fabricação CMOS: Primeiras etapas.

Fonte: (SILVA, 2007)

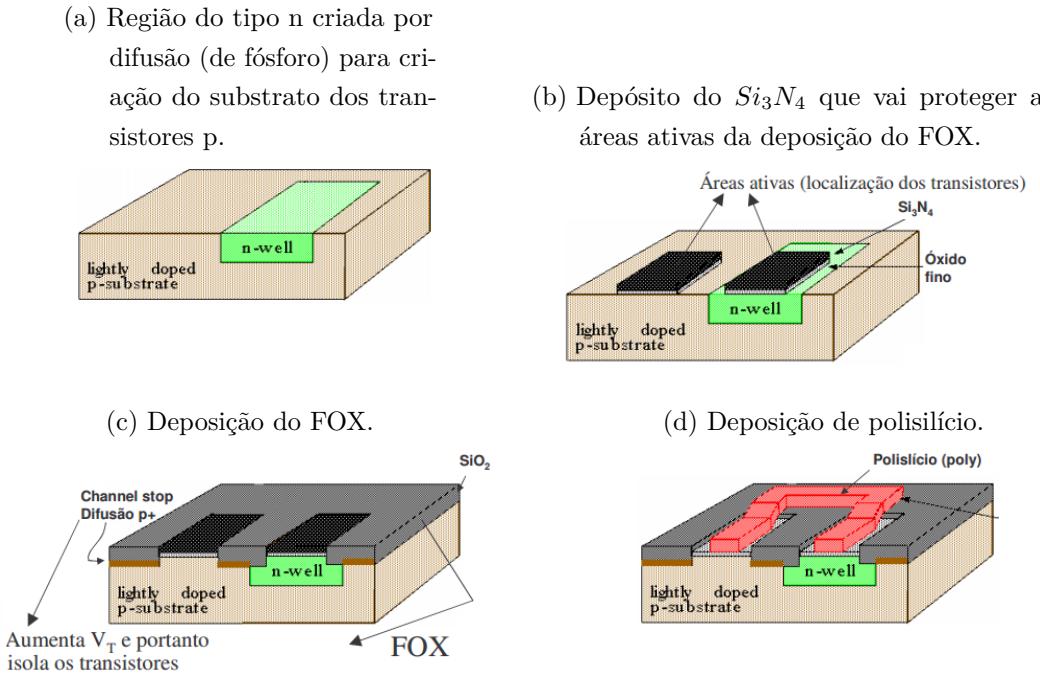

Depois da remoção do óxido ter sido feita pelo ácido, a próxima etapa é a criação da *n-well* (Fig. 6.2a). Nessa etapa a região do tipo n é criada por difusão (de fósforo) para criação do substrato dos transistores p. Em que primeiro é depositado  $Si_3N_4$  que vai proteger as áreas ativas da deposição do FOX (Field Oxide:  $SiO_2$ ), como pode ser visto na Fig. 6.2b. Para, na sequência, acontecer o crescimento de FOX (Fig. 6.2c) (SILVA, 2007).

Figura 6.2 – Fabricação CMOS: Criação do *n-well* e Crescimento de óxido de campo.

Fonte: (SILVA, 2007)

## 6.2 Processo de Metalização

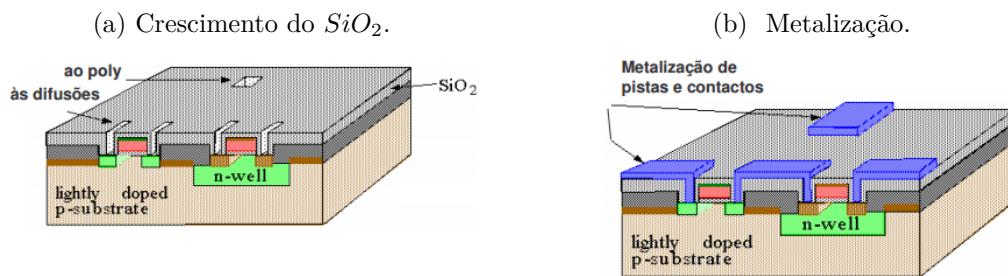

Após as primeiras etapas, todo o wafer é coberto com uma camada de  $SiO_2$  (isolante), como pode ser visto na Fig. 6.3a. Nessa etapa serão deixados espaços para a inserção de contatos. Na Fig. 6.3b pode ser vista a metalização, ou seja, a camada de metal é disposta nos espaços vazios deixados pelo crescimento do isolante (SILVA, 2007).

Figura 6.3 – Fabricação CMOS: Máscaras.

Fonte: (SILVA, 2007)

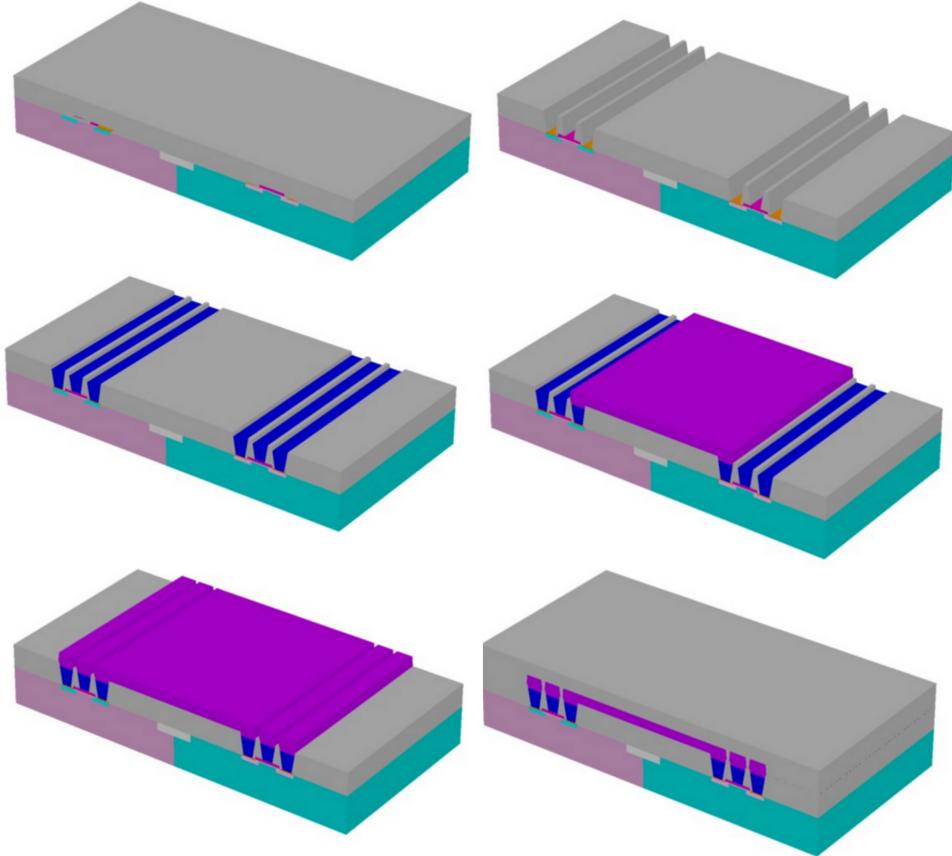

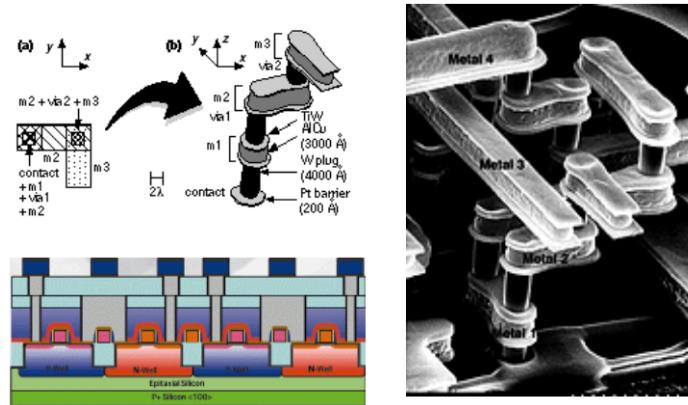

Na Fig. 6.4 pode ser visto como é realizado o processo de metalização. Durante toda a evolução desse processo, o isolante é colocado ( $SiO_2$  em cinza), em seguida é tirado

parte dele para a deposição das vias ou contatos (azul), para somente depois, ser colocada a camada de metal (roxo). É nessa etapa que as capacitâncias parasitas se formam, da conjunção de metal-isolante-metal que ocorre durante esse processo de metalização.

Figura 6.4 – Camadas de metal e vias (ou contatos).

Fonte: (MOSHTAQ KEYVAN ALIREZA ZAD, 2016)