Elmo Luiz Fechine Sette

# Layout-Oriented Design of a 60 GHz Power Amplifier in SiGe Technology

#### Elmo Luiz Fechine Sette

# Layout-Oriented Design of a 60 GHz Power Amplifier in SiGe Technology

Thesis presented in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

Universidade Federal da Paraíba — UFPB Centro de Energiais Alternativas e Renováveis Programa de Pós-Graduação em Engenharia Elétrica

Advisor: Antonio Augusto Lisboa de Souza Co-advisor: Emmanuel Benoit Jean-Baptiste Dupouy

> João Pessoa, Brasil 2018

#### Catalogação na publicação Seção de Catalogação e Classificação

S4951 Sette, Elmo Luiz Fechine.

Layout-Oriented Design of a 60 GHz Power Amplifier in SiGe Technology / Elmo Luiz Fechine Sette. - João Pessoa, 2018.

89 f. : il.

Orientação: Antonio Augusto Lisboa de Souza. Coorientação: Emmanuel Benoit Jean-Baptiste Dupouy. Dissertação (Mestrado) - UFPB/CEAR.

1. Cascode. 2. Layout-Oriented. 3. Load-Pull. 4. Millimeter Wave. 5. Power Amplifier. 6. SiGe. 7. 60 GHz. I. de Souza, Antonio Augusto Lisboa. II. Dupouy, Emmanuel Benoit Jean-Baptiste. III. Título.

UFPB/BC

# UNIVERSIDADE FEDERAL DA PARAÍBA – UFPB CENTRO DE ENERGIAS ALTERNATIVAS E RENOVÁVEIS – CEAR PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA - PPGEE

A Comissão Examinadora, abaixo assinada, aprova a Dissertação

# LAYOUT-ORIENTED DESIGN OF A 60 GHZ POWER AMPLIFIER IN SIGE TECHNOLOGY

Elaborado por

#### **ELMO LUIZ FECHINE SETTE**

como requisito parcial para obtenção do grau de Mestre em Engenharia Elétrica.

COMISSÃO EXAMINADORA

PROF. DR. ANTONIO AUGUSTO LISBOA DE SOUZA (Presidente)

PROF. DR. EMMANUEL BENOIT JEAN-BAPTISTE DUPOUY

Washon Terllizzie A. hopes PROF. DR. WASLON TERLLIZZIE ARAUJO LOPES

PROF. DR. ROBSON NUNES DE LIMA

João Pessoa/PB, 31 de julho de 2018.

# Acknowledgements

This study was financed in part by the Coordenação de Aperfeiçoamento de Pessoal de Nível Superior - Brasil (CAPES) - Finance Code 001.

The author also would like to acknowledge MOSIS for the fabrication of the chip and the IMEP-LAHC (Grenoble-INP) for providing measurement infrastructure.

### **Abstract**

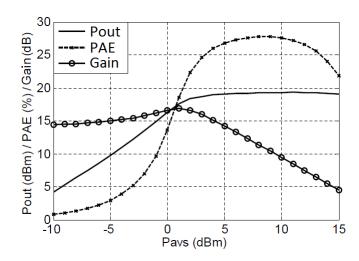

This work presents the design of a fully integrated cascode single-stage power amplifier for 60 GHz band. The technology used in the design was Global Foundries SiGe of  $0.13\mu\mathrm{m}$  (BiCMOS8HP). A load-pull analysis of the cascode was done including optimization of the bias and geometry parameters aiming at finding the best performance of this topology. A layout-oriented design approach was adopted to decide upon different combinations/arrangements of passive components and interconnections, aiming at reducing the global losses and, thus, increasing the energy efficiency of the amplifier. Post-layout simulations show a saturated output power of 19.32 dBm, 27.8% of power added efficiency (PAE) and a power gain of 10.4 dB at 60 GHz. The amplifier consumes 63 mA from a 4.4 V power supply and occupies an area of approximately 0,475 mm<sup>2</sup>. The circuit was taped-out in late 2017. Experimental results are presented at the end of the text.

**Keywords:** Cascode, Layout-oriented, Load-Pull, Millimeter Wave, Power Amplifier, SiGe, 60 GHz.

## Resumo

Este trabalho apresenta o projeto de um amplificador de potência totalmente integrado de estágio único e com topologia cascode para a banda de 60 GHz. Foi utilizada no projeto a tecnologia da Global Foundries em SiGe de 0,13  $\mu$ m (BiCMOS8HP). Uma análise loadpull do cascode foi feita incluindo otimização dos parâmetros de polarização e geometria visando encontrar o melhor desempenho possível desta topologia. Uma abordagem de projeto orientado a layout foi adotada para decidir entre diferentes combinações/arranjos de componentes passivos e interconexões, visando reduzir as perdas globais e, portanto, aumentar a eficiência energética do amplificador. Simulações pós-layout demonstram uma potência de saída saturada de 19,32 dBm, 27,8 % de PAE e um ganho de potência de 10,4 dB em 60 GHz. O amplificador consome 63 mA de uma fonte de alimentação de 4,4 V e ocupa uma área de aproximadamente 0,475 mm². O circuito foi enviado para fabricação no final de 2017. Os resultados experimentais são apresentados ao final do texto.

**Palavras-chave:** Amplificador de Potência, Cascode, *Load-Pull*, Ondas Milimétricas, Orientado a *Layout*, SiGe, 60 GHz.

### Resumen

Este proyecto presenta el diseño de un amplificador de potencia cascode de etapa única completamente integrado para la banda de 60 GHz. La tecnología utilizada en el diseño fue Global Foundries SiGe de  $0,13~\mu m$  (BiCMOS8HP). Se realizó un análisis de load-pull del cascode que incluyó la optimización de los parámetros de polarización y geometría con el objetivo de encontrar el mejor rendimiento posible de esta topología. Se adoptó un enfoque de diseño orientado a layout para decidir sobre diferentes combinaciones/arreglos de componentes pasivos e interconexiones, con el objetivo de reducir las pérdidas globales y así aumentar la eficiencia energética del amplificador. Las simulaciones posteriores al layout demuestran una potencia de salida saturada de 19,32 dBm, 27,8% de PAE y una ganancia de potencia de 10,4 dB a 60 GHz. El amplificador consume 63 mA de una fuente de alimentación de 4,4 V y ocupa un área de aproximadamente 0,475 mm². El circuito fue enviado a la fabricación a finales de 2017. Los resultados experimentales se presentan al final del texto.

**Palabras clave:** Amplificador de Potencia, Cascode, *Load-Pull*, Ondas Milimétricas, Orientado a *Layout*, SiGe, 60 GHz.

# List of Figures

| Figure 1 –  | Typical architecture of a transceiver                                               |

|-------------|-------------------------------------------------------------------------------------|

| Figure 2 –  | Simplified diagram of a power amplifier                                             |

|             | PA power balance                                                                    |

| Figure 4 –  | Output power and saturated output power of an implemented generic PA. 19            |

| Figure 5 –  | 1 dB compression point. Black (fundamental), blue (extrapolation) 22                |

| Figure 6 –  | Current waveforms for various conduction angles (ROGERS; PLETT,                     |

|             | 2010)                                                                               |

| Figure 7 –  | Power combining techniques: a) using transformer b) equivalent circuit              |

|             | of Wilkinson combiner/splitter                                                      |

| Figure 8 –  | Unlicensed frequency bands near 60 GHz around the world                             |

|             | Specific attenuation due to atmospheric gases as a function of frequency            |

|             | (YILMAZ; FADEL; AKAN, 2014)                                                         |

| Figure 10 – | Equivalent circuit for an incremental length of transmission line (POZAR,           |

|             | 2005)                                                                               |

| Figure 11 – | Representation of the S parameters in a quadripole                                  |

|             | Smith chart. Points A and B are two examples of impedances in the chart. 33         |

| _           | Circuit for stability analysis                                                      |

|             | Load-pull diagram for a bipolar cascode topology. Output power in red               |

|             | and PAE in blue                                                                     |

| Figure 15 – | Load-pull diagram for a input level of -15 dBm (green) and 5 dBm (red). 37          |

|             | a) effect of the addition of capacitive and inductive ideal components              |

|             | on the Smith chart. b) example of an impedance synthesis at 60 GHz                  |

|             | using ideal components                                                              |

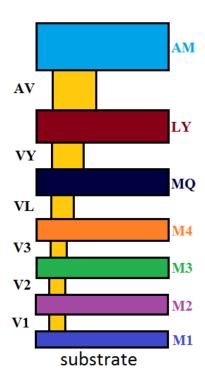

| Figure 17 – | BiCMOS8HP metal layers                                                              |

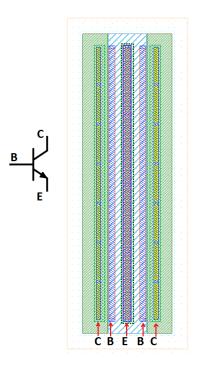

|             | Transistor HBT (18 $\mu$ m) npn CBEBC                                               |

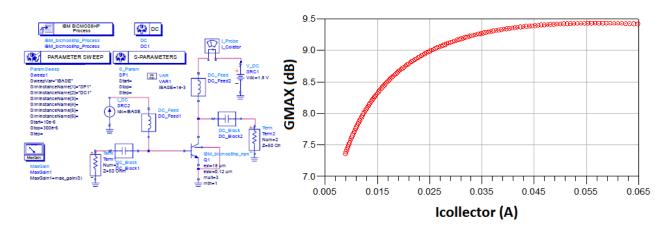

|             | GMAX of HBT (CBEBC), $VCE = 1.8 \text{ V.} \dots 42$                                |

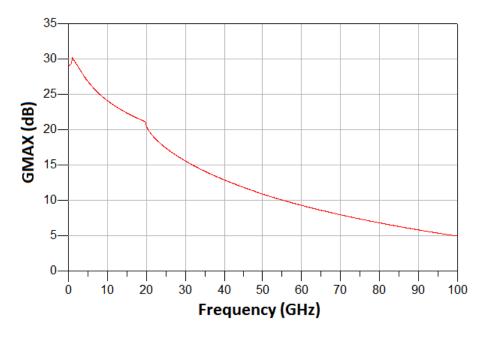

|             | GMAX as a function of frequency at 60 mA                                            |

| Figure 21 – | Oppperes (3.694 k $\Omega$ ) and oprrpres (991 $\Omega$ ) resistors 43              |

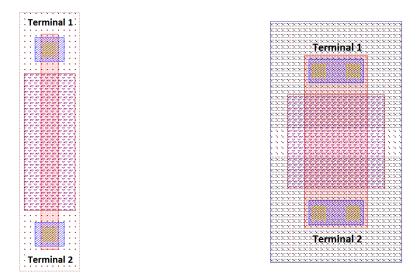

| Figure 22 – | a) MIM capacitor (93 fF) used for matching purpose. b) MIM capacitor                |

|             | (523 fF) used for AC feed. c) DualMIM capacitor (4.15 pF) used to                   |

|             | filter supply noise                                                                 |

| Figure 23 – | Behavior of the capacitors of Figure 22 as a function of frequency 44               |

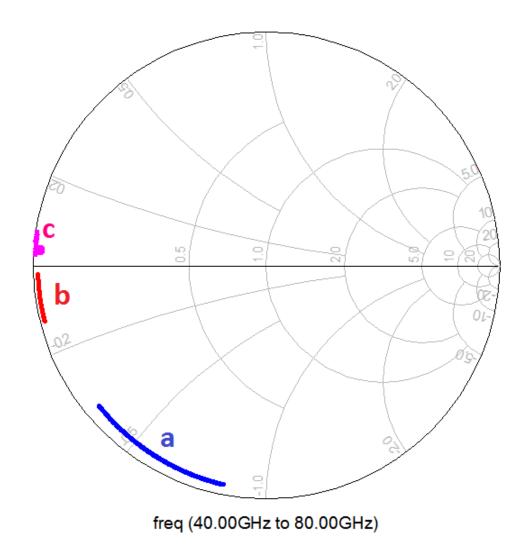

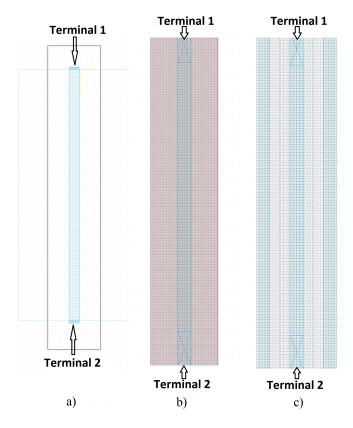

|             | Transmission lines (Access by AM): a) rfline, b) singlewire and c)                  |

|             | singlecpw                                                                           |

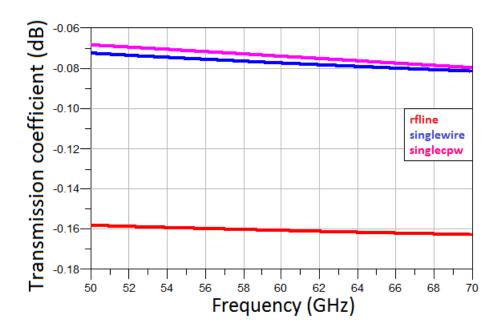

| Figure 25 – | Transmission coefficient of the transmission lines (L = 100 $\mu$ m, 50 $\Omega$ ): |

|             | rfline (red), singlewire (blue) and singlecpw (pink)                                |

| Figure 26 – | Simplified block diagram of an amplifier                                            |

| Figure 27 – | Amplifier Topologies                                                                |

|             | Design flow block diagram                                                           |

| _           | Generic Setup of a load pull                                                        |

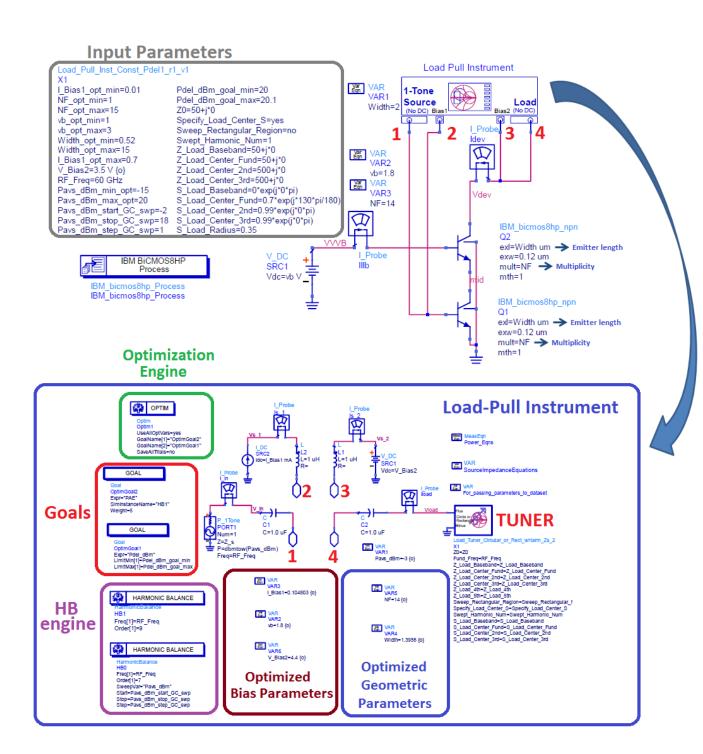

| _           | Our load-pull setup in ADS                                                          |

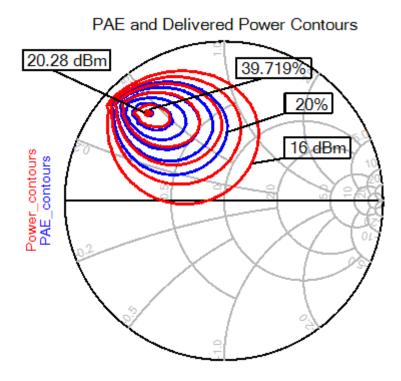

|             | Load-pull diagram for the cascode configuration with the parameters of              |

|             | table 4. Pavs = 5 dBm and 60 mA of collector current                                |

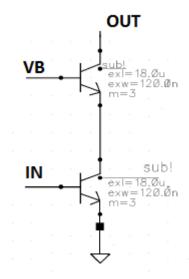

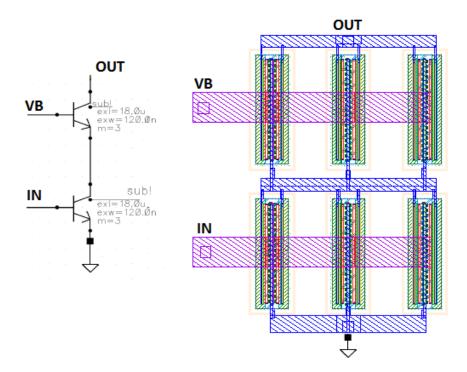

| Figure 32 – | Cascode circuit                                                                     |

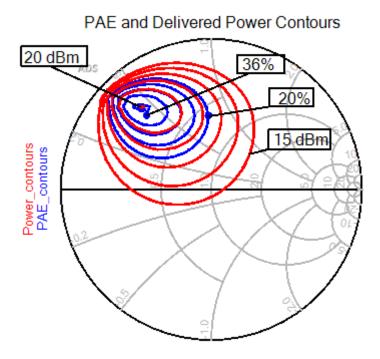

| Figure 33 – | Load-pull diagram for the cascode configuration with: 1.8 V (VB) , 4.4 V (VDD), exl = $18\mu m$ , Mult = 3 , Pavs = 5 dBm and 60 mA of |    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------|----|

|             | collector current                                                                                                                      | 56 |

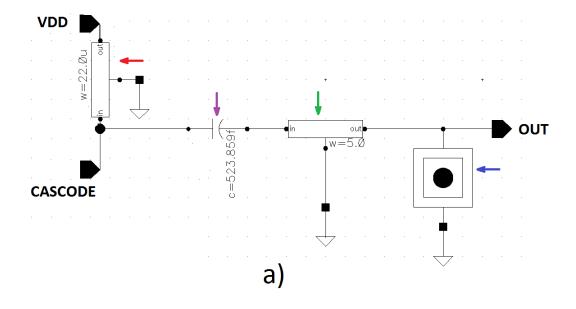

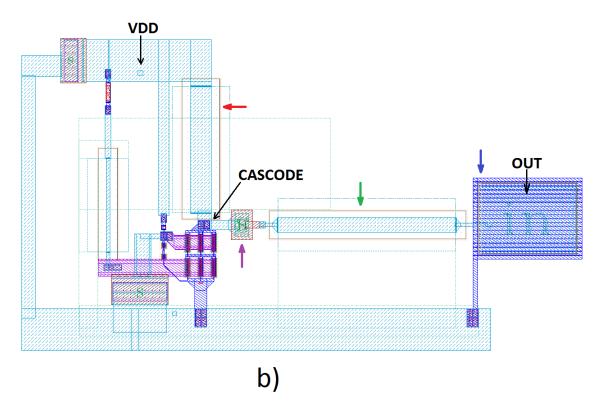

|             | Core's layout.                                                                                                                         | 56 |

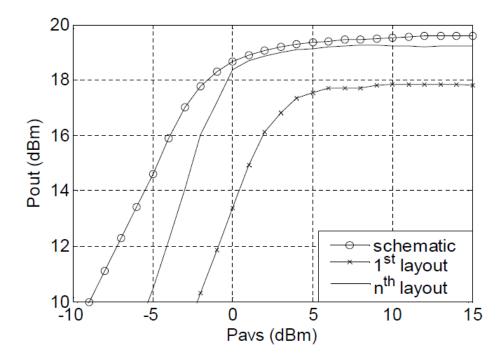

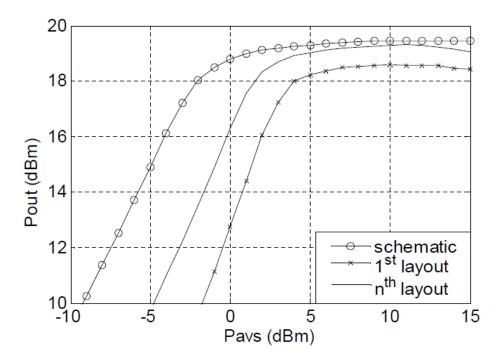

| Figure 34 – | Power delivered to the load (Pout) at schematic level, first and last                                                                  |    |

|             | layout (1st stage)                                                                                                                     | 57 |

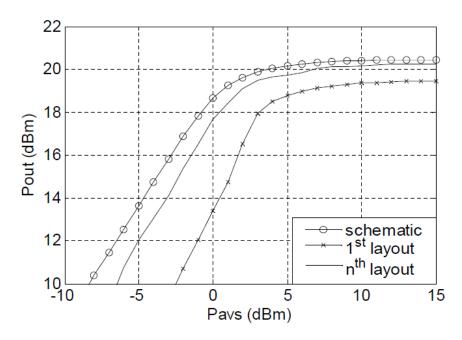

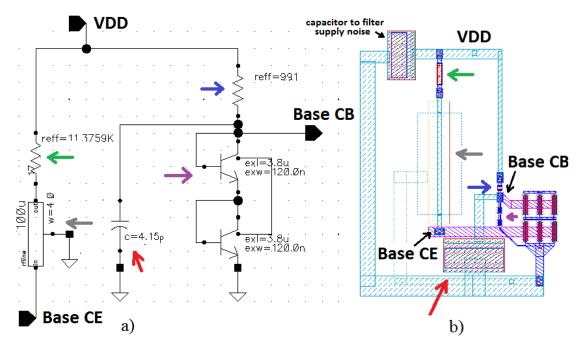

| Figure 36 – | Schematic of the bias circuit (a) and its layout (b)                                                                                   | 58 |

| Figure 37 – | Power delivered to the load (Pout) at schematic level, first and last                                                                  |    |

|             | layout (2nd stage)                                                                                                                     | 58 |

| Figure 38 – | Synthesis of the output network.                                                                                                       | 60 |

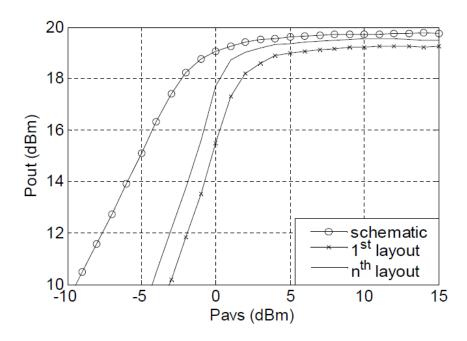

| Figure 39 – | Circuit of the output matching (a) and its layout (b)                                                                                  | 61 |

| Figure 40 – | Power delivered to the load at schematic, first and last layout (3rd stage).                                                           | 62 |

| Figure 41 – | Power delivered to the load at schematic, first and last layout (4th stage).                                                           | 63 |

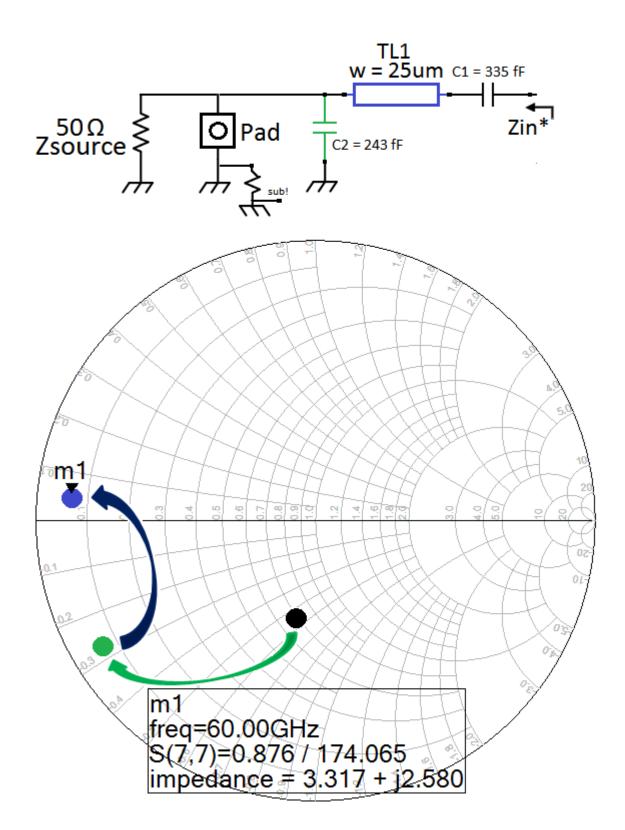

| Figure 42 – | Synthesis of the input network                                                                                                         | 64 |

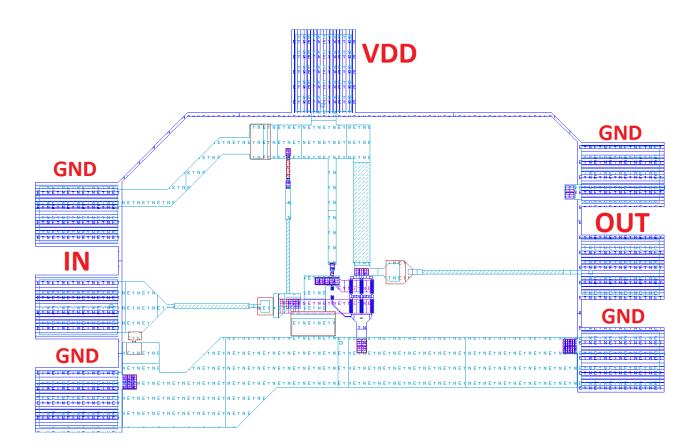

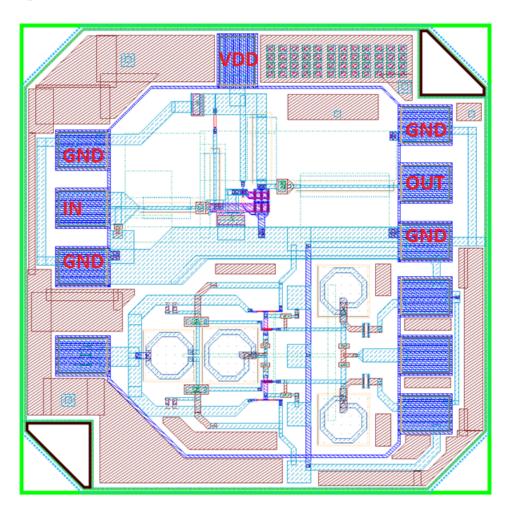

| Figure 44 – | Final layout of the power amplifier                                                                                                    | 65 |

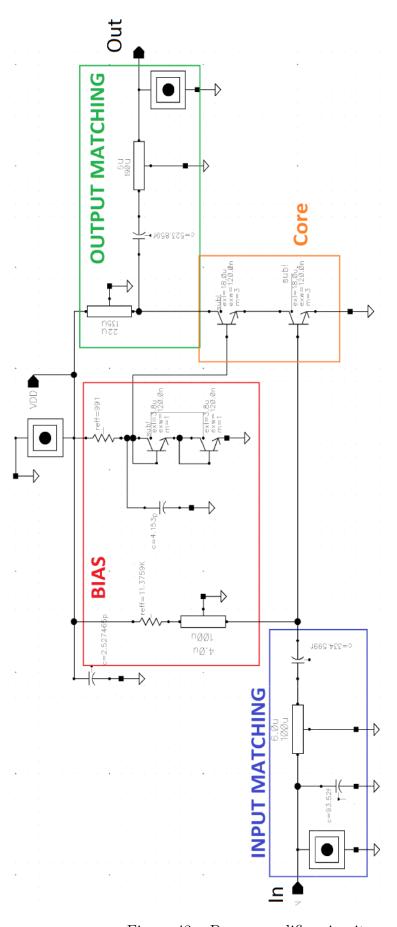

| Figure 43 – | Power amplifier circuit                                                                                                                | 66 |

| Figure 45 – | Power delivered to the load (Pout), PAE and power gain after parasites                                                                 |    |

|             | extraction.                                                                                                                            | 67 |

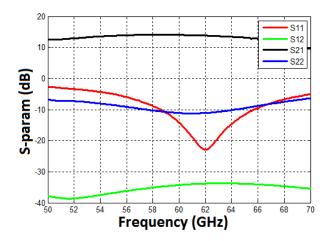

| Figure 46 – | S-parameters of the amplifier by a LSSP analysis with 5 dBm of input                                                                   |    |

|             | power                                                                                                                                  | 67 |

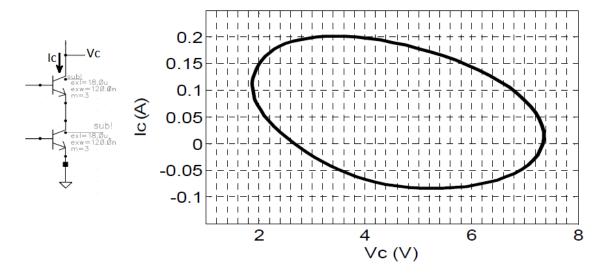

| Figure 47 – | Dynamic load-line of the cascode                                                                                                       | 68 |

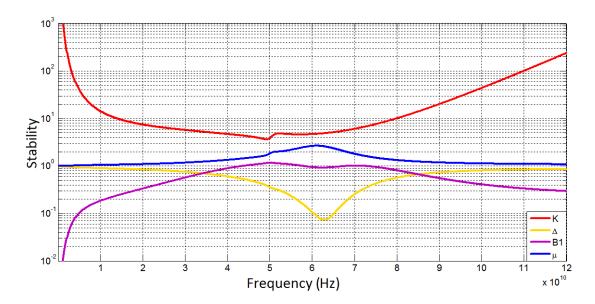

| Figure 48 – | Stability criteria                                                                                                                     | 69 |

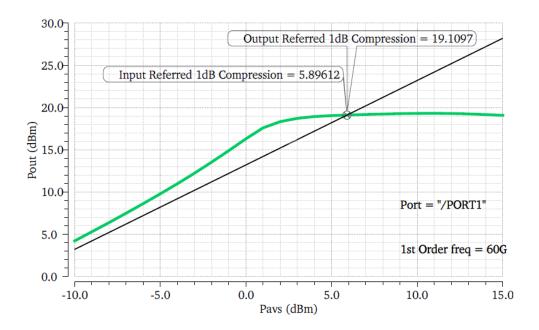

| Figure 49 – | 1 dB compression point referred to the input and output                                                                                | 70 |

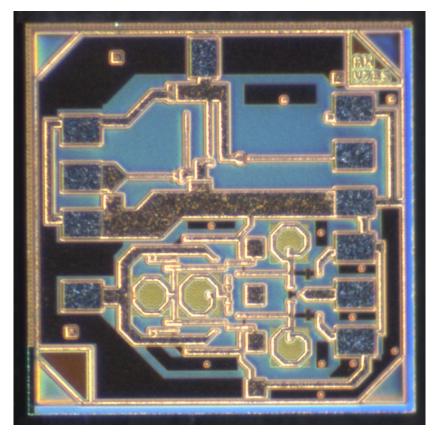

|             | Chip with a die area of $1 \text{ mm}^2$                                                                                               | 72 |

| Figure 51 – | Microphotography of the chip of Figure 50                                                                                              | 73 |

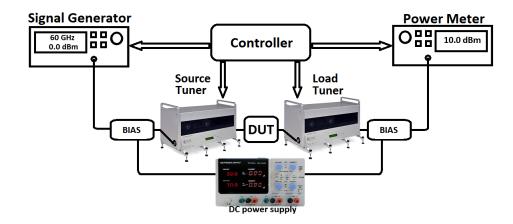

| Figure 52 – | Measurement bench used for characterizing our chips (IMEP-LAHC)                                                                        | 74 |

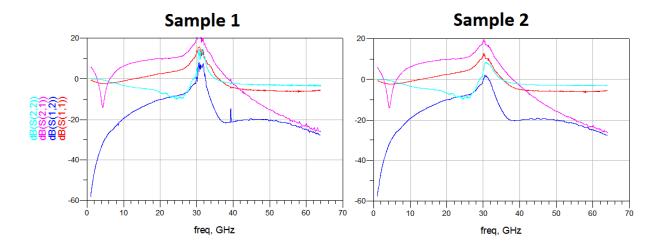

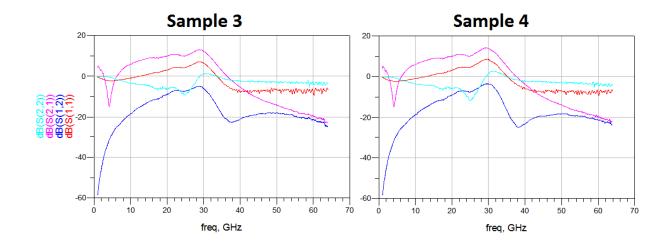

| Figure 53 – | S-parameters results for two samples of the circuit with supply voltage                                                                |    |

|             | lower than nominal (VDD = $3.5 \text{ V}$ )                                                                                            | 74 |

| Figure 54 – | S-parameters results for two samples of the circuit with supply voltage                                                                |    |

|             | lower than nominal (VDD = $3.7 \text{ V}$ ), and with the addition of a substrate                                                      |    |

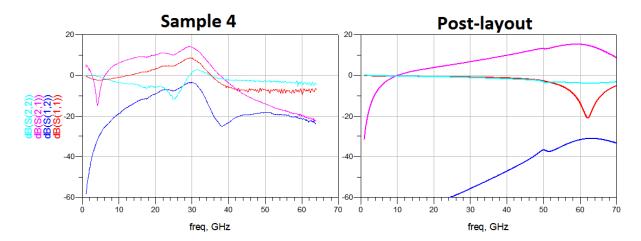

|             | of alumina.                                                                                                                            | 74 |

| Figure 55 – | S-parameters results of the sample 4 (VDD = $3.7 \text{ V}$ ) and post-layout                                                          |    |

|             | $(VDD = 3.7 V) \dots $           | 75 |

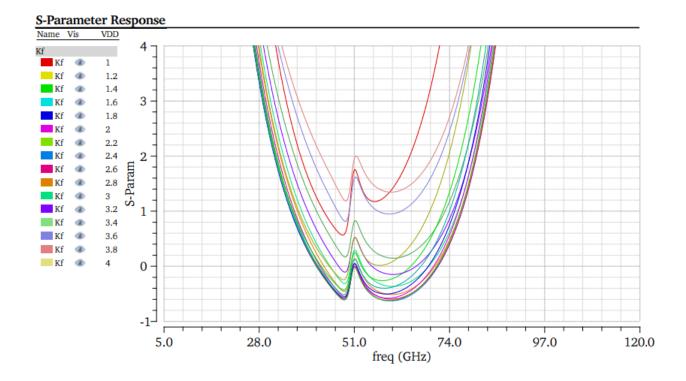

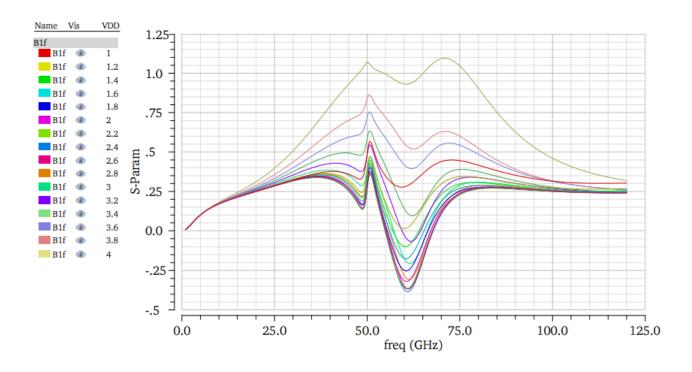

| Figure 56 – | K and B1 parameter analyses under different bias                                                                                       | 76 |

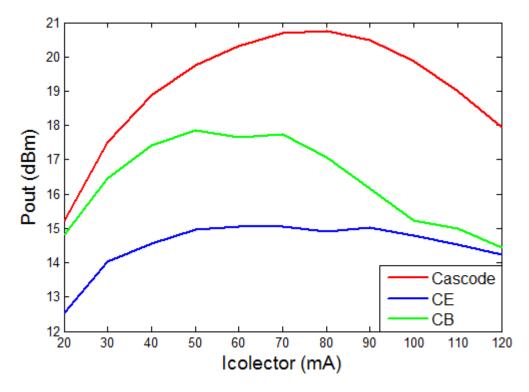

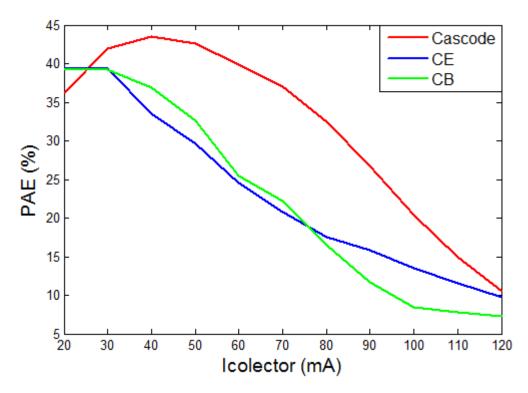

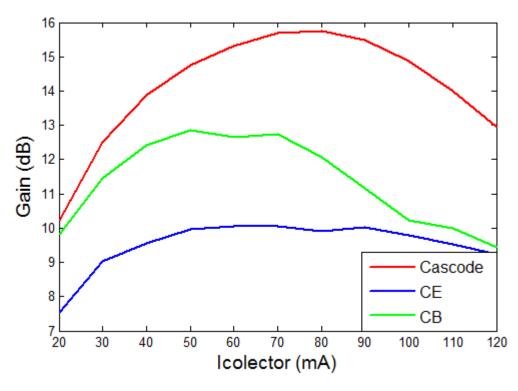

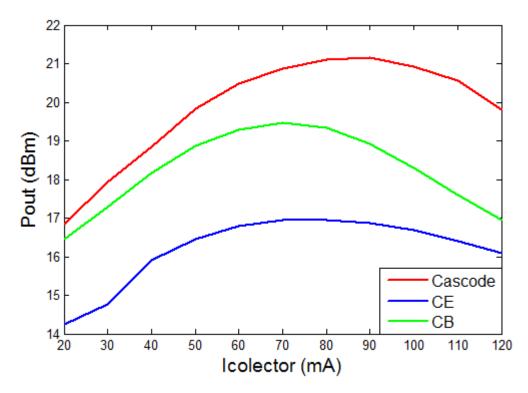

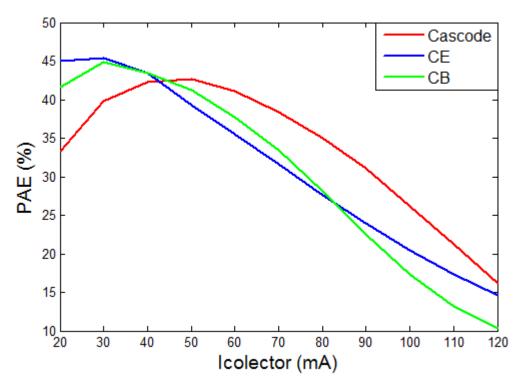

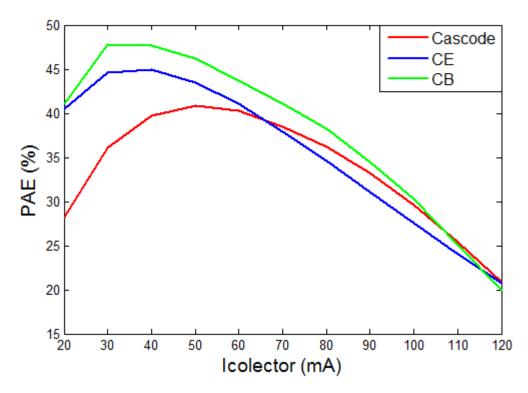

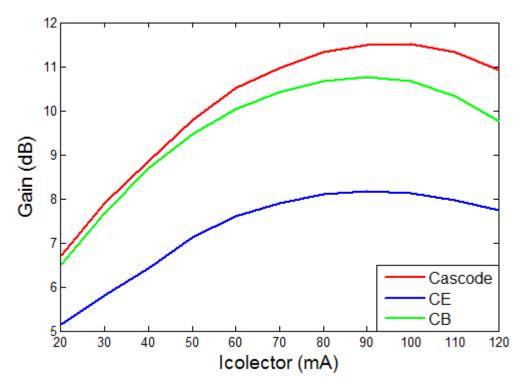

| Figure 57 – | Pout with 5 dBm of Pavs                                                                                                                | 85 |

| Figure 58 – | PAE with 5 dBm of Pavs.                                                                                                                | 86 |

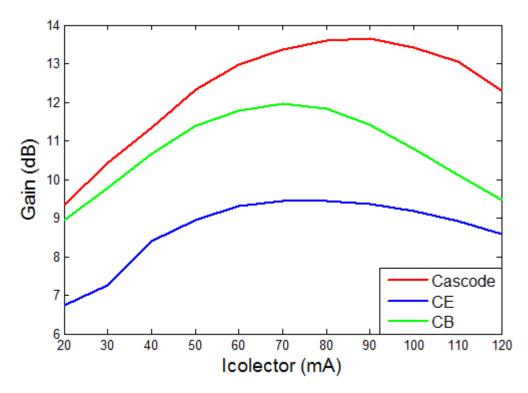

| Figure 59 – | Gain with 5 dBm of Pavs                                                                                                                | 86 |

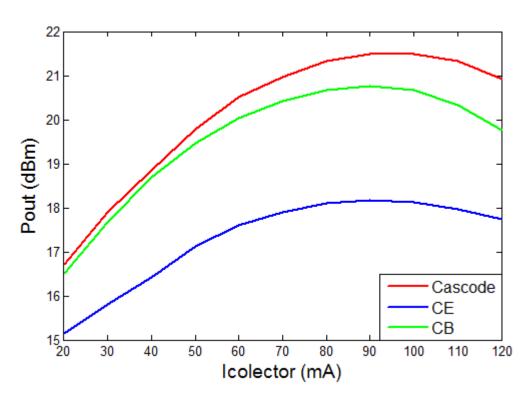

| Figure 60 – | Pout with 7.5 dBm of Pavs                                                                                                              | 87 |

| Figure 61 – | PAE with 7.5 dBm of Pavs.                                                                                                              | 87 |

| Figure 62 – | Gain with 7.5 dBm of Pavs.                                                                                                             | 88 |

| Figure 63 – | Pout with 10 dBm of Pavs.                                                                                                              | 88 |

| Figure 64 – | PAE with 10 dBm of Pavs                                                                                                                | 89 |

| Figure 65 – | Gain with 10 dBm of Pavs.                                                                                                              | 89 |

|             |                                                                                                                                        |    |

# List of Tables

| Table 1 | _ | Characteristics of the different classes (ROGERS; PLETT, 2010)   |

|---------|---|------------------------------------------------------------------|

| Table 2 | _ | State of the art in 60 GHz Power Amplifiers                      |

| Table 3 | _ | Target specifications                                            |

| Table 4 | _ | Optimized parameters                                             |

| Table 5 | _ | Comparison with the state of the art                             |

| Table 6 | _ | Measurements with the PA input left open                         |

| Table 7 | _ | Measurements with a 50 $\Omega$ connected to the input of the PA |

## List of abbreviations and acronyms

4G Fourth generation of mobile systems

5G Fifth generation of mobile systems

ACLR Adjacent Channel Leakage Ratio

ADS Advanced Design System

AM-AM Amplitude-Amplitude Conversion

AM-PM Amplitude-Phase Conversion

AR/VR Augmented Reality/Virtual Reality

BEOL Back-End-of-Line

BJT Bipolar Junction Transistors

BiCMOS Bipolar-CMOS

CB Common-Base

CE Common-Emitter

CAD Computer Aided Design

DAT Distributed Active Transformers

DRC Design Rules Check

DUT Device Under Test

ECMA European Computer Manufacturers Association

EVM Error Vector Magnitude

FOM Figure of Merit

GaAs Gallium Arsenide

GaN Gallium Nitride

GF Global Foundries

GSG Ground-Signal-Ground

HBT Heterojunction Bipolar Transistors

HEMT High Electron Mobility Transistors

IFPB Federal Institute of Paraíba

InP Indium Phosphide

ITU International Telecommunication Union

LNA Low Noise Amplifier

LO Local Oscillator

LSSP Large Signal S-Parameters

MIM Metal Insulator Metal

mmW millimeter Wave

NF Noise Figure

OFDM Orthogonal Frequency Division Multiplexing

PA Power Amplifier

PAE Power Added Efficiency

PHY Physical Layer

PVT Process, Voltage and Temperature

PZ Poles and Zeros

RF Radio Frequency

R&D Research and Development

SC Single Carrier

SiGe Silicon-Germanium

SiO2 Silicon Dioxide

T-lines Transmission lines

UFPB Federal University of Paraíba

VNI Visual Network Index

VNA Vector Network Analyzer

WRC World Radiocommunication Conference

WiGig Wireless Gigabit Alliance

WLAN Wireless Local Area Network

WPAN Wireless Personal Area Network

WVAN Wireless Video Area Network

# Table of Contents

| List of Figures                                 |

|-------------------------------------------------|

| List of Tables                                  |

| Table of Contents                               |

| Introduction                                    |

| LITERATURE REVIEW                               |

| A brief overview of power amplifiers            |

| Key performance parameters                      |

| Output power and saturated output power         |

| Efficiency                                      |

| Power gain                                      |

| Linearity                                       |

| Power amplifier operating classes               |

| Power combining techniques                      |

| State of the art in 60 GHz PAs                  |

| The 60 GHz band                                 |

| Standards                                       |

| Wireless HD                                     |

| ECMA-387                                        |

| IEEE 802.15.3.c (TG3c)                          |

| WiGig                                           |

| Microwave Theory                                |

| Transmission lines: model and propagation       |

| Scattering parameters (S-parameters)            |

| The Smith chart                                 |

| Stability analysis criteria                     |

| Impedance matching                              |

| Large-signal impedance matching (Load-Pull)     |

| Synthesis and impedances transformation         |

| Synthesis and impedances transformation         |

| A BRIEF INTRODUCTION TO SOME ELEMENTS AVAILABLE |

| IN BICMOS8HP TECHNOLOGY 39                      |

| The HBT transistor (npn)                        |

| Resistors                                       |

| Capacitors                                      |

| Transmission lines                              |

| DESIGN PROCEDURE                                |

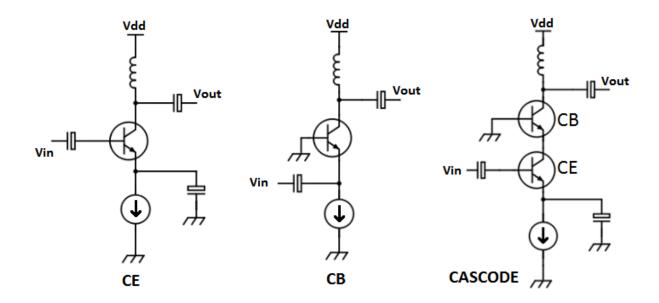

| Choice of amplifier topology                    |

| Specifications                                  |

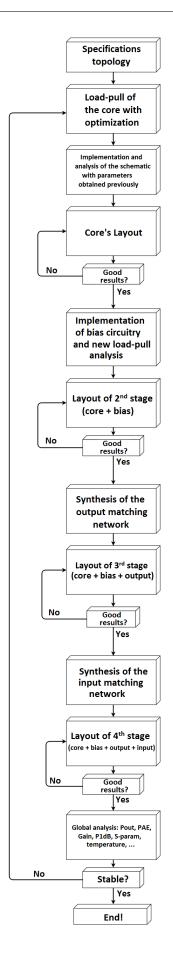

| Layout-oriented design                          |

| PA's core design                                |

|                                                 |

|       | APPENDIX                                   | 84 |

|-------|--------------------------------------------|----|

|       | REFERENCES                                 | 81 |

| 5     | CONCLUSIONS AND PROSPECTS                  | 79 |

| 4.6   | Experimental results                       | 73 |

| 4.5   | Tape-out                                   | 71 |

| 4.4   | Comparison with the state of the art       |    |

| 4.3.4 | Linearity                                  |    |

| 4.3.3 | Temperature                                |    |

| 4.3.2 | Stability analysis                         |    |

| 4.3.1 | Load-line analysis                         |    |

| 4.3   | Complementary parameters                   |    |

| 4.2.1 | S-parameters                               |    |

| 4.2   | Power amplifier key performance parameters |    |

| 4.1   | Power amplifier circuit and layout         |    |

| 4     | RESULTS                                    |    |

| 3.3.4 | Design of the input matching network       | 61 |

| 3.3.3 | Design of the output matching network      | 59 |

| 3.3.2 | Bias circuitry design                      | 57 |

### Introduction

In the last few years wireless communication industry had enormous growth due to the increasing demand of wireless devices. Nowadays, millions of people around the world are daily online exchanging data to each other through their smartphones, tablets and laptops. This huge demand for services are saturating the spectrum below 6 GHz, where mobile and data communication (3G, 4G) are usually done. This spectrum will no longer be sufficient to meet the ever-growing demand of consumers, who want all their devices to be online been able to record, transfer and monitor a large amount of data with increasing data rates.

The demand for content will continue to grow at extreme rates, which can be seen thanks to the annual Visual Network Index (VNI) released by Cisco (CISCO, 2017). The most recent (September 2017) report shows a demand of 278 Exabyte per month by 2021, representing an increasing of almost 100 times since 2010. In addition to the large amount of data, the number of devices and data rates will continue to grow exponentially (ANDREWS et al., 2014).

While the memory capacity and clock speed of computers have increased by a few orders of magnitude in recent decades, the frequency of wireless carriers ranged from just 0.8 to 5.8 GHz (RAPPAPORT et al., 2011). This limited spectrum allows data rate of only a few hundred Mb/s in the fourth generation (4G), mainly due to spectral congestion that heavily limits its bandwidth.

The necessity of a high rate and volume of data makes inevitable the migration of the carriers to beyond the Radio Frequency (RF) band, due to this one be relatively small compared to the vast free spectrum between 6 and 300 GHz (RAPPAPORT et al., 2015), fomenting the bases of what will become the fifth generation of mobile communication (5G). In this way, millimeter wave circuits (mmW) became a hot topic of this last decade, representing the most challenging and exciting opportunities for electronic engineers in the field of circuits design, antennas and communications systems (RAPPAPORT et al., 2011). Inside the millimeter wave band, there is a frequency range around 60 GHz that attracts more interest. The unlicensed band between 57 and 64/66 GHz becomes one of the most attractive option for the next generation mobile system (5G), for allowing an extremely high data rate (within the Gb/s range), and availability of a large free frequency band without any neighboring standards. The oxygen absorption at this band allows high attenuation of the signals that cross the environment, making these ideal for densely pack electronic media for short-range communication (RAPPAPORT et al., 2011).

Introduction 15

At such high frequencies the design of transceivers becomes challenging, since any parasitic element can significantly impact the behavior of the circuit. On the other hand, working at such high frequencies brings one advantage. In 60 GHz, the wavelength of approximately 2.5 millimeter in silicon dioxide  $(SiO_2)$ , allows a high density of integration of analog and microwave components, such as transmission lines and antennas, allowing the implementation of fully integrated topologies that were not possible at lower frequencies.

One of the main blocks in a transmitter is the power amplifier (PA), being the one in charge to amplifying the signal to such levels that can be radiated by the antenna. Thus, this block is the main responsible for the power consumption in a transmitter system. Its main performance characteristics are the power delivered to the load, power added efficiency (PAE), power gain and linearity.

In the last decade, the design of PAs in the millimeter wave range was performed in technologies based on semiconductors of group III-V<sup>1</sup>. These technologies were preferred for allowing a high frequency of operation when compared to the technologies based on silicon of that time. On the other hand, such manufacturing processes are relatively expensive, and do not allow easy integration with the digital part of the circuit. The continued process scaling in SiGe technology allowed the heterojunction bipolar transistor (HBT) to become sufficiently fast for operations in millimeter waves. These achieved a transition frequency of 505 GHz and a maximum oscillation frequency of up to 720 GHz (IHP, 2016), making it the main competitor of group III-V semiconductors in terms of high frequency performance. The drawback of this process is the reduction of breakdown voltages, making difficult to achieve large output power. Therefore the power amplifier is one of the most challenging blocks to be designed at this band.

The goal of this work was the investigation, analysis and design of power amplifiers in the band of millimetric waves, having the 60 GHz frequency as central. The great challenge of designing circuits in this frequency range is the impact caused by all the parasitic elements that arise as a result of the design of the layout. These parasitics arise from the several metal layers used to interconnect the components (passive and active), and which do not present a model in the schematic. At such high frequencies any parasitic elements, however small (e.g. fF capacitances or  $m\Omega$  resistances), can significantly impact the behavior of the amplifier by introducing losses and mismatches. For this reason the classical design approach, in which the circuit is completely designed in the schematic level to then be designed the entire layout, may not yield satisfactory results, that is, there can be a huge discrepancy between the results of the schematic and the layout. Due to this difficulty in reaching a good relation between schematic and layout results in very high frequencies, a layout-oriented design approach was proposed. This was adopted to decide upon different combination/arrangements of passive components and interconnections,

<sup>&</sup>lt;sup>1</sup> The group III-V are the semiconductors made up of elements from group III and V of the periodic table, such as GaAs, GaN, InP.

Introduction 16

aiming at reducing the global losses of the PA, thus increasing its efficiency. This approach was divided in steps, where each one is optimized by successive layout iteractions (iterative method) in order to establish the best relation between schematic and layout results, thus providing the expected performance.

This master's thesis took place in the RFWild laboratory located at the Federal University of Paraíba (UFPB) and Federal Institute of Paraíba (IFPB) in Brazil. The research group was established in 2013. This group develops researches in the area of microelectronics (design and modeling), instrumentation and Research and Development (R&D). The laboratory has undergraduates and masters students working on these projects. Further information about the laboratory and the projects developed by this group can be find at (RFWILD, 2018).

This work was carried out using all the infrastructure and the Computer Aided Design (CAD) tools of the RFWild's laboratory, and through the use of the Global Foundries (GF) SiGe BiCMOS8HP technology process of 0.13  $\mu$ m.

The rest of the document is organized as follows: Chapter 1 brings a literature review of the main fundamentals for a good understanding of the design procedure of this work. In Chapter 2 we describe the components of the technology used and their characteristics. In Chapter 3 we describe the design procedure methodology while Chapter 4 presents and discusses the results obtained. Finally, Chapter 5 draws the conclusions and discusses the prospects of this work.

## 1 Literature Review

### 1.1 A brief overview of power amplifiers

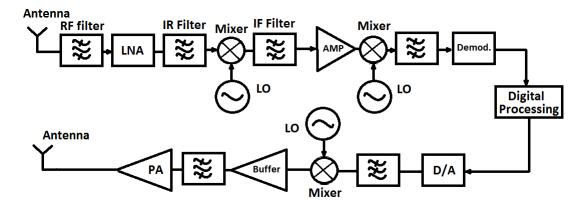

The transceiver is the element responsible for RF signal modulation/demodulation, enabling wireless communication through high frequency signals. This is made up of two stages, one responsible for the transmission (transmitter) and the other responsible for the reception (receiver) of the signal. The performance of these blocks depends directly on the individual performance of each circuit that constitutes it, and of the set as a whole. In communication systems these transceivers can be implemented in different architectures. A typical architecture of an RF transceiver is shown in Figure 1.

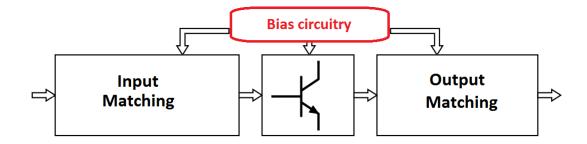

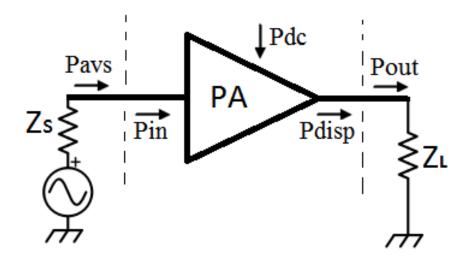

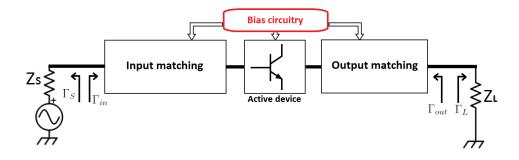

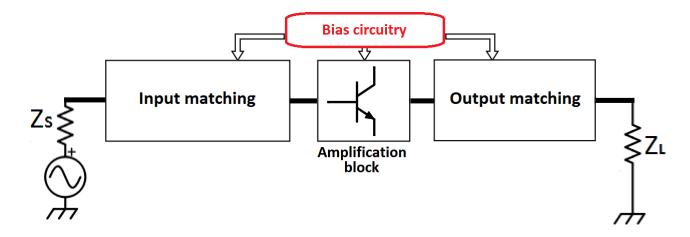

After the information is converted to the baseband, the signal is processed digitally. The trend is that the digital processing is getting closer and closer to the antenna, thus reducing costs and increasing system flexibility (LEE, 2004). Afterward digital processing, the signal is suited in order to be able to be transmitted in the environment. In the receiver stage the design of the following RF circuits stand out: Low Noise Amplifier (LNA), local oscillators (LO) and mixer. In the transmitter the LNA is replaced by a power amplifier (PA). Its design is of great interest for the transmitter chain, since it may represent the majority part of the consumption of an entire transceiver. A simplified power amplifier features three main stages as shown in Figure 2. It is composed of an input matching network, an amplifier stage and an output matching network, besides the bias circuitry. Power amplifiers should provide a high output power with the best possible efficiency, in order to increase the autonomy of battery-powered systems. Besides these ones, the design of a PA requires take in account other parameters that characterize the good performance of the circuit. In this way the RF design engineer must be able to establish the best trade-off between output power, efficiency, gain, linearity, among others,

Figure 1 – Typical architecture of a transceiver.

Figure 2 – Simplified diagram of a power amplifier.

for a given situation. These are used as performance parameters of the circuit and allow comparison with the state of the art. The next subsection will introduce some of the key performance characteristics of power amplifiers.

#### 1.1.1 Key performance parameters

#### 1.1.1.1 Output power and saturated output power

One of the main goals in designing a PA is to deliver a certain power to a load. Output power is one of the main performance characteristics of the amplifier, being its maximum value determined largely by the load impedance and the power supply (ROGERS; PLETT, 2010). The theoretical maximum power (at fundamental frequency) in a purely resistive load would be defined by:

$$P_{out} = \frac{V_{out}^2}{2R_L} \tag{1.1}$$

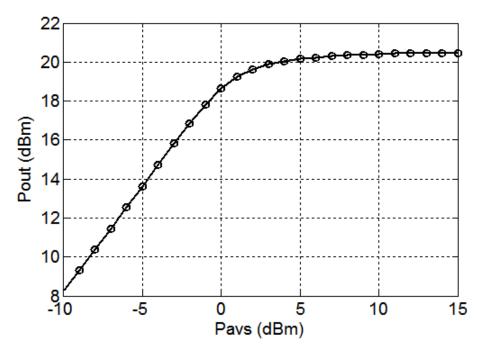

where  $V_{out}$  is the peak output voltage in the frequency of interest and  $R_L$  is the load (generally  $50\Omega$ ). The diagram in Figure 3 shows the power balance in a PA. The output power ( $P_{out}$ ) is defined as the one delivered to the load to which the amplifier is connected.  $P_{in}$  represents the power effectively entering in the amplifier, while  $P_{disp}$  is the power available at the output of this.  $P_{avs}$  represents the power available from the source, while  $P_{dc}$  is the DC power dissipated at the amplifier. The characteristic source and load impedances ( $Z_S \in Z_L$ ) are generally equal to 50  $\Omega$ . In Figure 4 the relation between the output power ( $P_{out}$ ) and the power available by the source ( $P_{avs}$ ) for an implemented generic power amplifier is shown. In this graph, the evolution of the output power is observed as a function of the increasing available input power. The highest possible value that  $P_{out}$  can achieve is called saturated output power ( $P_{sat}$ ). In this region increments in  $P_{avs}$  will no longer affects  $P_{out}$  and so, for a fixed bias, this will lead to a reduction of gain and efficiency (PAE).

Figure 3 – PA power balance.

Figure 4 – Output power and saturated output power of an implemented generic PA.

#### 1.1.1.2 Efficiency

Energy consumption is a very important parameter in the design of battery-powered wireless communication systems. The figure of merit that takes this into account is the efficiency. This is why it is one of the main performance parameters of a PA, since most of the energy dissipated in a transceiver occurs in this block. In this way, the power amplifiers must be able to transfer (and amplify) the available power from the source to the load efficiently. Without this, part of the power will be dissipated in the form of heat, causing a temperature increase in the transistor that will result in poor performance or even the burning of the device (worst case). Maximum efficiency is limited by the amplifier class and impacted by the parasitic elements of the circuit. There are two definitions of efficiency: drain efficiency  $(\eta)$  and PAE. The drain efficiency presented in Equation 1.2 describes the relationship between the output power and DC power. Usually, PAE presented in Equation 1.3 is more significant and utilized for taking into account the input power. Through the latter it is noted that for a high gain, i.e.  $P_{out}$  much larger than  $P_{in}$ , the PAE will be equivalent to drain efficiency.

$$\eta = \frac{P_{out}}{P_{dc}} \tag{1.2}$$

$$PAE = \frac{P_{out} - P_{in}}{P_{do}} \tag{1.3}$$

#### 1.1.1.3 Power gain

There are different power gain terminologies in PAs, due to the impedance mismatches in their input and output. The transducer power gain (Equation 1.4) establishes the relationship between the output power  $(P_{out})$  and the power available by the source  $(P_{avs})$ .

$$G_t = \frac{P_{out}}{P_{avs}} \tag{1.4}$$

The operating power gain (Equation 1.5) establishes the relationship between the output power  $(P_{out})$  and the power at the input of the amplifier  $(P_{in})$ .

$$G_p = \frac{P_{out}}{P_{in}} \tag{1.5}$$

Finally, the available power gain (Equation 1.6) establishes the relationship between the available power at the output of the amplifier  $(P_{disp})$  and the available power by the source  $(P_{avs})$ :

$$G_{disp} = \frac{P_{disp}}{P_{avs}} \tag{1.6}$$

Transducer gain is the most used because it takes into account all the effects of the mismatches.

#### 1.1.1.4 Linearity

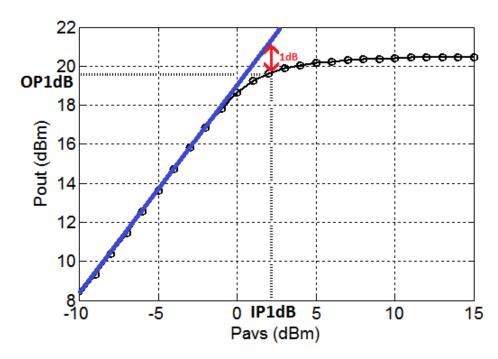

Another important performance parameter of a power amplifier is linearity. This one describes the ability of a PA to amplify the signal with a limited level of distortion. An amplifier responds linearly for small values of power of the input signal. As the signal level grows a variation in the gain arises due to intrinsic non-linearities to the active device. The gain compression occurs when the relation between input power and output power is no longer linear. When the output power is 1 dB less than the expected ideal response, the 1 dB compression point  $(P_{1dB})$  is obtained. This parameter can be referred to input  $(IP_{1dB})$  or output  $(OP_{1dB})$  power. This non-linearity is sometimes also referred as AM-AM (Amplitude Modulation) conversion gain. Graphically this point is obtained by extrapolating the fundamental curve at low input levels and observing where the difference between the extrapolation and the fundamental one is 1 dB (Figure 5).

By plotting the phase of the output signal as a function of the input signal another non-linearity can be observed: the amplitude-phase conversion (AM-PM). This non-linearity causes signal distortion affecting the EVM (Error Vector Magnitude) and the ACLR (Adjacent Channel Leakage Ratio) parameters used to qualify complex modulations. The first one quantifies the error between the output symbol and the reference symbol in a given constellation. A high ACLR will indicate interference in neighboring channels due to the appearance of power side lobes (spectral regrowth).

This work will focus on the measures of 1 dB compression point, because it is the most easy to obtain and used by most works.

#### 1.1.2 Power amplifier operating classes

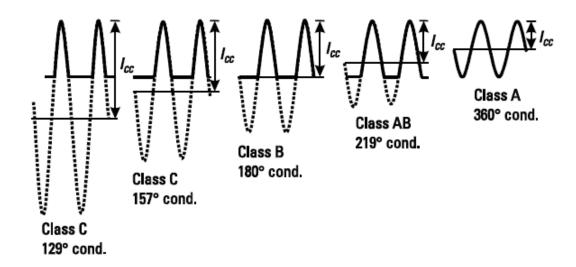

Power amplifiers are divided into different classes that vary according to the relation between the input and output signal, conduction angle and efficiency. There are four main classes of amplifiers (Class A, B, AB and C) which the active device acts as a controlled current source, also known as sinusoidal class. On the other hand, PAs that use the active device as a switch fit to classes D, E, F and S (among others), also known as switching classes. For these last, the switching frequency must be higher than the operating frequency.

Figure 5-1 dB compression point. Black (fundamental), blue (extrapolation).

Therefore, the implementation of these classes at very high frequencies may bring some inconvenience, as the transistor may not switch fast enough (between saturation and cutoff regions). All classes of amplifiers are extensively discussed in (RAZAVI, 2011; LEE, 2004; ROGERS; PLETT, 2010), so here we will address only a brief summary of the conventional classes that use the transistor as a current source.

The class A amplifier is the most linear among all, presenting a 360° conduction angle. The bias of this class is usually established so that the transistor operates (quasi)linearly (LEE, 2004). This condition is satisfied by avoiding cut-off and saturation, in a bipolar transistor. The maximum drain efficiency possible in this class of amplifiers is 50%. As the current conduction angle decreases, linearity also decreases. On the other hand, amplifiers that operate at a reduced angle take the transistor to the cut-off region during part of the cycle, thus increasing efficiency. The class B amplifier is biased so that the transistor is at the conduction threshold. It has a conduction angle of 180° with a maximum theoretical drain efficiency of approximately 78.5%. The class AB amplifier presents a trade-off between linearity and efficiency, since it is biased in order to have a conduction angle between 180 and 360°. The closer to 360° the more linear and less efficient the amplifier will be. The class C amplifier is biased so that the transistor conducts for less than half of a cycle, hence the collector current will consist of a periodic pulse train (if the input signal is also periodic). This class presents a conduction angle between 0 and 180 ° and a maximum drain efficiency of 100%. Table 1 summarizes the classes of amplifiers with their respective conduction angles and drain efficiency. Figure 6 shows the waveform of the collector current in relation to the conduction angle for different classes of amplifiers.

| Class | Conduction angle (°) | $\eta_{max}(\%)$ |

|-------|----------------------|------------------|

| A     | 360                  | 50               |

| AB    | 180 - 360            | 50 - 78.5        |

| В     | 180                  | 78.5             |

| С     | 0 - 180              | 78.5 - 100       |

Table 1 – Characteristics of the different classes (ROGERS; PLETT, 2010).

It can be seen that the collector current is partially rectified in classes that operate with a conduction angle of less than 360 °. In this way the output must present harmonics that arise because of the effects of non-linearity due to the reduced angle of conduction. These harmonics should be filtered in order to respect the requirements of emission regulators.

Figure 6 – Current waveforms for various conduction angles (ROGERS; PLETT, 2010).

#### 1.1.3 Power combining techniques

Many times reaching the output power specifications becomes an arduous task in the design of power amplifiers. In the millimeter wave range this work is even more hard, since the gain of a transistor falls with increasing frequency. For this reason, in many of the applications of RF and millimeter waves, it is necessary to use power combining techniques. Two of the most used techniques in millimeter wave PAs are: 1) using transformers and 2) using passive power combining elements, also known as Wilkinson power combiner. Both techniques combine the signals (in phase) of two or more amplifier stages. The transformer combines the voltages in phase so as to achieve a larger excursion of the signal at the output of the PA (Figure 7a). This technique is a good option when the design kit of the technology has integrated transformers. In most technologies, however, integrated transformers are not available. Wilkinson power combiner (or splitter) is another very

interesting technique in high frequency applications, since the length of the transmission lines of its equivalent circuit depends on the wavelength of the signal (Figure 7b). Thus, at high frequencies, this combiner can be integrated into the transceiver chip. This technique allows power combining while providing isolation between ports and impedance matching. Some of the state-of-the-art works of PAs make use of these techniques as we will see in the following subsection.

Figure 7 – Power combining techniques: a) using transformer b) equivalent circuit of Wilkinson combiner/splitter.

#### 1.1.4 State of the art in 60 GHz PAs

In this section a review of the state of the art in power amplifier design at 60 GHz band is presented. We considered papers developed in the last decade in SiGe-based processes that vary between 0,25  $\mu$ m e 0,12  $\mu$ m. Table 2 summarizes the key performance parameters of these ones. To compare the performance of power amplifiers, in general, a figure of merit (FOM) is adopted, including different performance parameters. One of the ways to define FOM is based on the guidelines introduced by the International Technology Roadmap for Semiconductors (ITRS), which considers the saturated output power ( $P_{sat}$ ) in dBm, the power gain in dB, the PAE (%) and the central frequency in GHz, defined by (ITRS, 2017):

$$FOM = P_{sat}(dBm) + G(dB) + 10 * \mathcal{L}og(PAE(\%)) + 20 * \mathcal{L}og(fc(Hz))$$

$$\tag{1.7}$$

This FOM includes the main performance parameters of power amplifiers. However it does not take into account some others, as the linearity. Sometimes the parameters of Equation 1.7 are used with respect to the 1 dB compression point, but these ones are barely available in published works. For this reason, in order to compare several works, we used the FOM described in Equation 1.7.

| Ref                        | [1]                       | [2]                                                            | [3]                            | [4]                            | [5]                     | [6]                     | [7]                    | [8]                                                     | [9]                                                   |

|----------------------------|---------------------------|----------------------------------------------------------------|--------------------------------|--------------------------------|-------------------------|-------------------------|------------------------|---------------------------------------------------------|-------------------------------------------------------|

| Tec. (μm)                  | SiGe                      | SiGe                                                           | SiGe                           | SiGe                           | SiGe                    | SiGe                    | SiGe                   | SiGe                                                    | SiGe                                                  |

|                            | 0.13                      | 0.13                                                           | 0.25                           | 0.25                           | 0.25                    | 0.13                    | 0.25                   | 0.12                                                    | 0.13                                                  |

| Freq (GHz)                 | 60                        | 60                                                             | 61                             | 60                             | 60                      | 60                      | 61.5                   | 60                                                      | 40/65                                                 |

| Topology /<br>Architecture | Push-pull differ. 1 stage | Push-pull differ. 2 stages with power combining by transformer | Cascode<br>single. 2<br>stages | Cascode<br>single. 2<br>stages | Cascode single. 1 stage | Cascode single. 1 stage | Cascode difer. 1 stage | CE single. 5 stages w/ power combining (2way) wilkinson | Cascode w/ driver (2way) asymmetrical power combining |

| $P_{sat}(dBm)$             | 20                        | 23                                                             | 15.5                           | 18                             | 14.6                    | 16.8                    | 17.4                   | 21.3                                                    | 23.6 @55 GHz                                          |

| $Gain_{sat}(dB)$           | 4.5                       | 13                                                             | 14*                            | 11                             | 10.7                    | 11.4                    | 7                      | 22*                                                     | 18.8 @55 GHz                                          |

| $Gain_{max}(dB)$           | 18                        | 20                                                             | 18.8                           | 15                             | 13.2*                   | 14.5*                   | 14.2                   | 27.5                                                    | 24*                                                   |

| OP1dB<br>(dBm)             | 13.1                      | -                                                              | 14.5                           | -                              | -                       | 11.7                    | 12.2                   | 19.2                                                    | 19.9 @55 GHz                                          |

| PAE (%)                    | 12.7                      | 6.3                                                            | 19.7                           | 14                             | 22                      | 28.4                    | 16.3                   | 14.4                                                    | 27.7 @55 GHz                                          |

| FoM                        | 84.60                     | 86.55                                                          | 82.95                          | 80.02                          | 76.78                   | 81.39                   | 79.49                  | 95.94                                                   | 96.83                                                 |

| Supply (V)                 | 4                         | 4                                                              | 3.3                            | 3.3                            | 3                       | 4                       | 3.3                    | 2                                                       | 4                                                     |

| Pdc (mW)                   | 248                       | 1200                                                           | 132                            | 198                            | 123                     | 64                      | 257.4                  | 420                                                     | -                                                     |

| Area (mm x mm)             | 1.3 x 0.75                | 1.9 x 1.8                                                      | 0.75 x 1.06                    | 0.53 x 0.53                    | 0.61 x 0.56             | 0.4 x 0.5               | 0.85 x 0.73            | 1.8 x 1.3                                               | 1.23 x 0.83                                           |

\* estimated from plots

```

[1](PFEIFFER; GOREN, 2007a);

[2](PFEIFFER; GOREN, 2007b);

[3](DO et al., 2008);

[4](HAMIDIAN et al., 2010);

[5](HELLFELD et al., 2011);

[6](SUN; FISCHER; SCHEYTT, 2012);

[7](GRUJIC et al., 2012);

[8](YISHAY; ELAD, 2016);

[9](CHAPPID; SENGUPTA, 2017);

```

Table 2 - State of the art in 60 GHz Power Amplifiers

In the work [1], a single-stage differential cascode circuit was designed to provide a high gain and output power with good efficiency at 60 GHz. A push-pull topology was used for the amplifier core, which is a well known topology implemented at lower frequencies. This topology is used to decrease the impedance transformation ratio required for differential antennas, thereby improving the efficiency of the output matching network. To increase the breakdown voltage of the output device, the cascode were designed very close to each other in order to provide a good AC ground at the base of the output device (common-base). An automatic level detector circuit was also implemented in order to minimize the impacts caused by the variation in process, voltage and temperature (PVT).

In [2] a two-stage amplifier with power combining by distributed active transformers (DAT) was designed. The circuit has achieved a high output power of 23 dBm, which is equivalent to +/- 6.3 V of swing (peak to peak) on a 100  $\Omega$  load. The amplifier's core uses a push-pull differential topology very similar to the work [1]. Six Wilkinson power splitters were used to share the signal coming from the driver with the two-stage differential amplifier.

In the work [3], a two-stage single-ended power amplifier was designed to operate at 61 GHz using a 0,25  $\mu$ m process. The amplifier features a cascode topology operating in AB class providing good gain, isolation and efficiency. Microstrips are used for matching and filtering.

The amplifier in [4] presents a two-stage single-ended cascode topology. The PA core was obtained by optimizing the dimensions of the transistor and by current combination techniques best described in (NATARAJAN et al., 2006). The amplifier can operate in class A and class AB, but the best results of output saturated power and PAE are obtained by operating near the class B region. The matching networks are composed of high quality factor transmission lines and capacitors MIM (Metal Insulator Metal), thus minimizing losses due to matching.

The work developed in [5] presents a methodology to design millimeter wave power amplifiers. This one takes into account the model for small-signals of the active devices, without the need of an accurate model for large-signal. The new methodology was validated by designing a PA in a 0.25  $\mu$ m process with a cascode, single-ended and single-stage topology. Matching networks were implemented through the use of transmission lines and capacitors.

In [6] a single-ended cascode PA was designed in a 0,13  $\mu$ m process. A high PAE is obtained by putting the output transistor (common-base) in a weak avalanche region (with an output collector voltage swing close to  $BV_{cbo}$ ) through its correct sizing. The bias voltages are fixed through the use of HBTs connected as diodes. Linearity is achieved through the optimization of the input network and the degeneration inductor. This PA is the one with the highest PAE and the smallest chip area of all the amplifiers listed.

An one-stage differential cascode power amplifier is presented in [7] using a 0,25  $\mu$ m process. In this work a careful electromagnetic modeling of the interconnections with the transistors is made. Transmission lines and capacitors are used for matching purposes. The main goal was not to obtain the highest output power and PAE, but rather to show that through a good partitioned and carefully modeled layout, an excellent correlation between simulation and measurement can be obtained.

In work [8] a common-emitter five-stage PA was designed. Two shunt cores are combined in phase through a splitter (at the input) and a modified Wilkinson combiner (at the output). This modified topology is best discussed in (HORST et al., 2007). The power supply of the amplifier is implemented through digitally adjustable biasing circuitry. This PA presents the highest gain among all the amplifiers cited in this section, in addition to presenting the second largest FOM.

The most recent paper found [9] was published by August 2017. A new methodology for impedance synthesis is discussed. Amplifiers feature a cascode topology in parallel preceded by drivers. Each branch are summed through an asymmetric combiner, which allows the programmable synthesis of complex impedances. This allows the cores to see the optimal output impedance, thus relieving trade-offs between output power, efficiency and frequency reconfigurability. The PA features a 25 GHz operating band between 40 and 65 GHz, with best results at 55 GHz. This work was the one that presented the highest saturated output power and FOM among those summarized in Table 2.

In this work, we followed the line of work [6], which allows to obtain good results of Pout and PAE, through taking the transistor to a weak avalanche region. This was designed without the use of power combining techniques, greatly reducing the used chip

area (which is also a constraint). On the other hand, the design-kit of the technology has power combiners, however these would only be used if we could not meet our output power specifications with a single amplifier, as the power consumption and the area would increase. The layout-oriented approach proposed in this thesis also recalls what was done (layout partitioning) in work [7].

#### 1.2 The 60 GHz band

The growing demand for wireless communication devices and the need of higher speed rates, makes relevant and necessary the use of the spectrum in the millimeter wave range. According to the channel capacity theorem proposed by Shannon Hartley (Equation 1.8), one of the ways to achieve a higher data rate is through the use of a larger band.

$$C = Band * \mathcal{L}og_2(1 + SNR) \tag{1.8}$$

where C is the channel capacity (in bits/s), Band is the bandwidth (in Hz), and SNR represents the signal-to-noise ratio (linear power ratio).

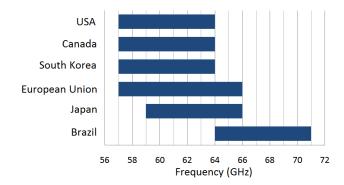

The sub-6 GHz spectrum is already saturated by existing several communications standards. Millimeter wave range then becomes the most attractive option to obtain gigahertz bandwith, allowing a high data rate. Within the spectrum of millimeter waves, the band around 60 GHz is one that attracts most the industry's attention in the world for the next generation (5G) mobile systems. This is due the fact this is a band not yet licensed in most part of the world. In the United States of America this band is ranged between 57 and 64 GHz, as well as in Canada and South Korea. In the European Union this band extends from 57 to 66 GHz, whereas in Japan it is between 59 and 66 GHz. In Brazil, however, the band between 57 and 64 GHz has already been licensed for satellite applications, while the band between 64 and 71 GHz remains unlicensed (TELECO, 2017; ANATEL, 2017). Figure 8 presents a summary of the unlicensed spectrum around the world.

Figure 8 – Unlicensed frequency bands near 60 GHz around the world.

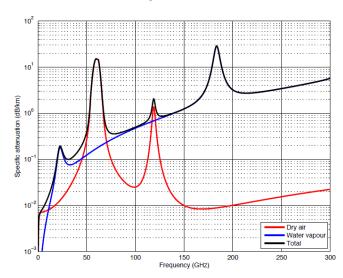

The allocation of frequency bands to the next generation of mobile (5G) systems, however, will only really be defined by the ITU (International Telecommunication Union) during the World Radiocommunication Conference (WRC), which will take place in 2019. There is a strong tendency for the band around 60 GHz to be one of the chosen, and the whole world industry uses it, including Brazil. In addition to being unlicensed, the 60 GHz band presents some peculiarities that have aroused great interest for short-range wireless networks. The oxygen absorption at this band generates a high attenuation of the signals that cross the environment, making it ideal for dealing with a dense and secure data traffic. Figure 9 shows this attenuation as a function of frequency. In 59.755 GHz one of the attenuation peaks occurs, with a value equal to 15.255 dB/km (YILMAZ; FADEL; AKAN, 2014). This attenuation is an advantage when it is desired to transmit data in a safe way, since the waves will not propagate for long distances. Interferences with other standards operating in the same frequency range will also be minimized because of this. In this way the main applications of this band will be focused on the Wireless Local Area Network (WLAN) and Wireless Personal Area Network (WPAN). In addition, the small wavelength in this frequency range allows the miniaturization of the antennas, allowing them to be integrated in the same chip of the transceiver.

The 5G generation will also make use of the concept of small cells that was already introduced in 4G. This cell is basically a miniature of a base station that breaks up a cell site into much smaller pieces (pico cells, micro cells and femtocells), with applications for indoor and outdoor systems. Small cells are typically used in very densely populated urban areas for improving coverage and signal strength. This concept is not fully matured, but has undergone a great evolution in the last years, through the development of new techniques that minimize its disadvantages.

Figure 9 – Specific attenuation due to atmospheric gases as a function of frequency (YIL-MAZ; FADEL; AKAN, 2014).

#### 1.2.1 Standards

Due to the great opportunities that this frequency range can offer, there is a joint effort of the international industry to standardize and commercialize it (RAPPAPORT et al., 2011). Some standards are already well matured and are constantly updated by the technical groups. Some of these are: ECMA-387 , WirelessHD, 802.15.3.c (TG3c) and WiGig.

#### 1.2.1.1 Wireless HD

The Wireless HD standard is a consortium created among giants of the electronics industry, some of them: Intel, LG, Samsung, Sony, Toshiba and others. This consortium is dedicated to providing a unified standard, based on the 60 GHz spectrum, for high-speed wireless communication of electronic products. Its specifications were made available in 2008. The main applications of this standard are turned to wireless transmission of lossless high-definition audio and video, creating the so-called Wireless Video Area Network (WVAN). Its current data rate is between 10 and 28 Gb/s (WIRELESSHD, 2017).

#### 1.2.1.2 ECMA-387

The European Computer Manufacturers Association (ECMA) has also set a standard since 2010 at this band. The ECMA-387 is intended to support a massive transfer of data, such as data downloads and high-definition multimedia streaming (ECMA, 2017).

#### 1.2.1.3 IEEE 802.15.3.c (TG3c)

The IEEE 802.15.3 TaskGroup 3c (TG3c) standard was formed in 2005 to develop a Physical Layer (PHY) alternative in the millimeter wave band for the WPAN 802.15.3-2003 standard. This standard supports high speed rate for applications such as: high speed internet access, streaming, among others. (IEEE, 2017).

#### 1.2.1.4 WiGig

The Wireless Gigabit Alliance (WiGig) standard was announced in 2009 promoting the already existing IEEE 802.11ad protocol, with applications aimed at extending computer peripherals and high definition interfaces, such as projectors and monitors. In 2013, WiGig was acquired by the Wi-Fi Alliance. In 2016 the Wi-Fi group introduced the certificate so-called "Wi-Fi CERTIFIED WiGig<sup>TM</sup>", in order to accelerate the commercialization of the WiGig devices (WIFI, 2017). WiGig will enable service providers to use millimeter wave spectrum for point-to-point connectivity as an alternative to fiber. Facebook has

announced recently multiple new partnerships to bring the concept of Terragraph (in essence are WiGig radios forming a city mesh) to market, delivering fiber-like speeds and high-capacity connectivity to dense urban areas. The idea is to use the huge amount of spectrum available in 60 GHz to connect city people to a faster, better, and cheaper Internet (WIFI, 2018). Operating in this less crowded frequency band, this standard enables extremely high performance, multi-gigabit connectivity and low latency for a range of applications, including wireless docking, augmented reality/virtual reality (AR/VR), multimedia streaming, gaming, and networking. (WIFI, 2017)

All of these standards operate in the unlicensed band around 60 GHz (57 to 66 GHz). This 9 GHz free spectrum is generally divided into four channels with 2.16 GHz each. The most commonly used modulation techniques are Single Carrier (SC) and Orthogonal Frequency Division Multiplexing (OFDM).

### 1.3 Microwave Theory

At high frequencies, the standard circuit theory cannot be used directly to solve circuits. This is due to the fact that this is an approximation of the broader electromagnetic theory, also known as Maxwell's equations. The theory of transmission lines bridges the gap between field analysis and classical circuit theory, becoming an extremely important tool for the analysis of microwave networks. (POZAR, 2005).

#### 1.3.1 Transmission lines: model and propagation

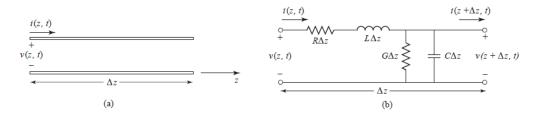

The classical circuit analysis considers that the wavelength of the signal is much larger than the physical dimensions of the devices, characterizing them as lumped circuits. When this condition is not satisfied the circuits are considered to be distributed, where the voltages and currents can vary significantly in magnitude and phase over the physical extent of the device. In Figure 10 the schematic of a two-wire transmission line is presented. The infinitesimal line of length  $\Delta z$  can be modeled by a circuit with lumped elements, shown in Figure 10b.

Figure 10 – Equivalent circuit for an incremental length of transmission line (POZAR, 2005).

The parameters R, L, G and C are per unit length quantities. The series resistance (R) represents the resistance due to the finite conductivity of both conductors and is expressed in  $\Omega/m$ . The inductance (L) represents the self-inductance of both conductors in H/m. The parameter C represents the shunt capacitance due to the proximity of the two conductors (in F/m), while G represents the conductance due to the dielectric losses in the material between the conductors (in S/m). A finite transmission line can be seen as a cascade of several sections of the circuit of Figure 10b (POZAR, 2005). However, there is a difficulty in working with transmission lines on a silicon substrate due to the relatively high doping (high G) of this, which introduces significant transmission losses and limits the quality factor of these lines.

#### 1.3.2 Scattering parameters (S-parameters)

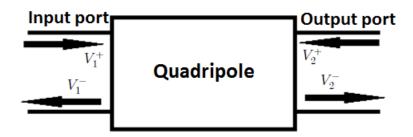

The scattering parameters (or S-parameters) are used to characterize the behavior of linear systems at high frequencies, where obtaining other parameters through measures becomes more complex (RAZAVI, 2011; LEE, 2004). A diagram of the representation of the S parameters for a two-port network is shown in Figure 11.

Figure 11 – Representation of the S parameters in a quadripole.

The main idea of this representation is to measure the incident voltage wave  $V_1^+$  entering the system, as well as the corresponding reflected voltage wave  $V_1^-$  coming out of the system (through the input port). The incident and reflected normalized waves  $V_1^+$  and  $V_1^-$  are related to the terminal voltages and currents of the input port. For the network shown in Figure 11, contributions from the two ports can be combined to form the Equation 1.9 in the matrix form.

$$\begin{bmatrix} V_1^- \\ V_2^- \end{bmatrix} = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix} \begin{bmatrix} V_1^+ \\ V_2^+ \end{bmatrix}$$

$$(1.9)$$

where S11, S12, S21 and S22 are the scattering parameters measured between the input

and output port. Expanding the scattering matrix, the following equations can be written:

$$S_{11} = \frac{V_1^-}{V_1^+}, if \to V_2^+ = 0 \tag{1.10}$$

$$S_{12} = \frac{V_1^-}{V_2^+}, if \to V_1^+ = 0 \tag{1.11}$$

$$S_{21} = \frac{V_2^-}{V_1^+}, if \to V_2^+ = 0 \tag{1.12}$$

$$S_{22} = \frac{V_2^-}{V_2^+}, if \to V_1^+ = 0 \tag{1.13}$$

where S11 is the input reflection coefficient (input impedance), S12 is the reverse transmission coefficient, S21 is the forward transmission coefficient and S22 is the output reflection coefficient (output impedance) of a quadripole. These parameters are widely used in low noise amplifier designs, impedance matching and stability criteria analysis.

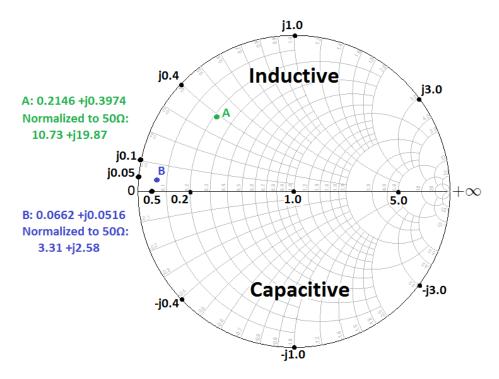

#### 1.3.3 The Smith chart

A very useful way of graphically visualizing impedances is through the Smith chart. This allows you to trace impedances with the real part between zero and infinity and with any possible imaginary values. Using the concepts of reflection coefficients, it is possible to measure how well two impedances are matched. The voltage reflection coefficient ( $\Gamma$ ) is defined by the amplitude of the reflected voltage wave normalized with respect to the amplitude of the incident voltage wave:

$$\Gamma = \frac{V_0^-}{V_0^+} = \frac{Z_L - Z_0}{Z_L + Z_0} \tag{1.14}$$

where  $Z_0$  is the characteristic impedance and  $Z_L$  is the load impedance.

Rewriting Equation 1.14, it can be defined the load impedance in the following way:

$$Z_L = Z_0 \frac{1+\Gamma}{1-\Gamma} \tag{1.15}$$

The real impedances are represented between  $0\Omega(\Gamma = -1)$  to  $+\infty\Omega(\Gamma = +1)$ , so when  $\Gamma = 0$ ,  $Z_L = Z_0$ . This means that the center of the Smith chart indicates the point at which the load is identical to the characteristic impedance (i.e., matching condition). Normalizing with respect to  $Z_0$ , one can obtain the impedance directly from the Smith chart of Figure 12. The circular lines represent the constant resistance contour, whereas

the arc lines correspond to the constant reactance. In addition the upper part of the chart represents positive reactance (inductive), while the lower one negative reactance (capacitive). In the chart of Figure 12, we represent the points A and B, which are impedances that will be used further in this work for matching purpose.

Figure 12 – Smith chart. Points A and B are two examples of impedances in the chart.

### 1.4 Stability analysis criteria

An important feature of amplifiers is stability analysis. Through this, it can be ensured that oscillations will not occur due to the presence of feedback paths from the output to the input, that might arise (oscillations) for certain combinations of input and output impedance. For this analysis under small-signal operation consider the circuit of Figure 13.

Figure 13 – Circuit for stability analysis.

Considering this circuit, oscillations are possible when the impedance of the input or output port presents negative real part, implying in:  $|\Gamma_{in}| > 1$  ou  $|\Gamma_{out}| > 1$ . It is worth remembering from the subsection previous that a reflection coefficient greater than unity indicates a region outside the Smith chart. Because  $\Gamma_{in}$  and  $\Gamma_{out}$  depend on the input and output matching networks, the stability of the amplifier will also depend. In (POZAR, 2005) two types of stability are defined:

- Unconditional Stability: The network will be unconditionally stable if  $|\Gamma_{in}| < 1$  e  $|\Gamma_{out}| < 1$  for any passive load and source impedances (i.e.,  $|\Gamma_S| < 1$  and  $|\Gamma_L| < 1$ )

- Conditional Stability: The network will be conditionally stable if  $|\Gamma_{in}| < 1$  and  $|\Gamma_{out}| < 1$  only for a certain range of passive load and source impedances. This case is also referred to as potentially unstable.

The stability criteria of the amplifiers are usually frequency dependent, since the input and output matching networks generally are too. In this way it is possible that the amplifier is stable in the operating frequency, but becomes unstable in other ones. Therefore the criteria must be evaluated over a wide spectrum range in order to ensure stability. There are several ways to test the stability conditions of a circuit. One is to determine regions on the Smith chart for  $\Gamma_s$  and  $\Gamma_L$  where the amplifier is conditionally stable. This approach requires a more elaborate mathematical treatment that can be seen in detail in (POZAR, 2005). On the other hand, there are simpler tests to be evaluated that determine the unconditional stability of the circuit using the S parameters, known as the Rollet's stability factor (K and  $\Delta$ ), and defined as follows:

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2|S_{12}S_{21}|}$$

(1.16)

$$|\Delta| = |S_{11}S_{22} - S_{12}S_{21}| \tag{1.17}$$

When K > 1 and  $|\Delta| < 1$  are simultaneously satisfied, they form a set of necessary and sufficient conditions for unconditional stability (POZAR, 2005). If these conditions are not met stability circles should be used to determine if there are  $\Gamma_s$  and  $\Gamma_L$  values for which the circuit is conditionally stable. Despite the K and  $\Delta$  parameters form a rigorous mathematical treatment to indicate unconditional stability, they do not serve to compare the stability of different devices, that is, it does not indicate how good the stability of one circuit relative to another is. This is due to the need to meet two different requirements  $(K \text{ and } \Delta)$ . An alternative method proposed in (EDWARDS; SINKSY, 1992), known as

geometric stability factor, uses only one requirement to indicate stability, the parameter  $\mu$  defined below.

$$\mu = \frac{1 - |S_{11}|^2}{|S_{22} - \Delta S_{11}^*| + |S_{12} - S_{21}|}$$

(1.18)

For  $\mu > 1$  the amplifier will be unconditionally stable. The geometric stability factor calculates the distance from the center of the Smith chart to the nearest point of instability. In this way higher values of  $\mu$  indicate a better stability. The parameters K,  $\Delta$  and  $\mu$  are sufficient to prove and qualify the stability of a device. Sometimes in Computer Aided Design (CAD) tools the K parameter is made available directly in the setups of S-parameter simulations, whereas the  $\Delta$  is not. In these cases there is another parameter also widely used to replace the  $\Delta$ , known as factor B1 and defined by:

$$B1 = 1 + |S_{11}|^2 - |S_{22}|^2 - |\Delta|^2$$

(1.19)

If K > 1 and B1 > 0 the circuit will be unconditionally stable.

These criterias considers that the circuit works with small-signals (only powered), also known as stationary analysis. Under large-signal operation, however, the stability analysis is a much more harder task. One approach is to use the Poles and Zeros (PZ) analysis, but first, it is necessary to put the amplifier in a known non-linear state (by applying an input signal that does it). Then small-signal PZ analysis is performed around this non-linear operating point. This is a hard task because this non-linear stability analysis needs to be conducted at several drive conditions (frequency-power level set). In addition, this PZ analysis works well only for small networks (EDWARDS, 2012). One example of PZ identification tool is STAN (AMCAD, 2018).

Another approach is to use network-system identification routine by applying a dataset obtained through circuit analysis in the real frequency domain. These routines tend to be focused on the pure mathematical manipulations rather than the analysis of electronic circuits (EDWARDS, 2012).

### 1.5 Impedance matching

The impedance matching seeks to minimize reflection between a source and a load. In other words, it targets maximize power transfer. There are two approaches to impedance matching analysis. When designing circuits that work with small-signal levels, such as the LNA, the small-signal approach is utilized. In this approach one can determine the three different types of power gains (Equations 1.4, 1.5 and 1.6) in terms of the S parameters and the reflection coefficients ( $\Gamma_s$  e  $\Gamma_L$ ). These gain definitions differ mainly by how the source

and the load are matched to the circuit. The most useful one is the gain of the transducer  $(G_t)$ , because it takes into account both source and load mismatches. In the condition that the input and output are the conjugate complex of the source and load impedances respectively, the power gain will be maximized and thus  $G_t = G_p = G_{disp}(POZAR, 2005)$ . In the design of power amplifiers the small-signals analysis can not be considered, since the device is usually driven to a non-linear region of operation. In PAs the requirements to maximize the output power of the amplifier usually differ from those used to maximize power gain in small-signals. Under these conditions the optimal source/load impedances may no longer correspond to the conjugate complex of the input/output impedances. The optimum load impedance value for a maximum output power is found through load-pull measurements and/or simulations. This approach will be discussed in the following subsection, whereas the analysis in small-signals can be well evaluated in (POZAR, 2005; RAZAVI, 2011).

#### 1.5.1 Large-signal impedance matching (Load-Pull)

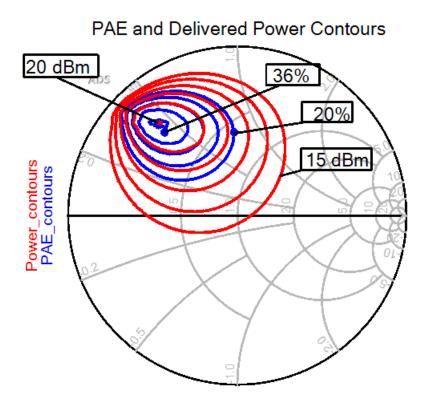

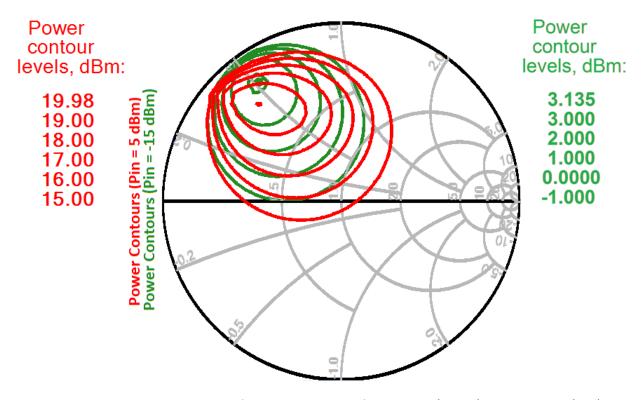

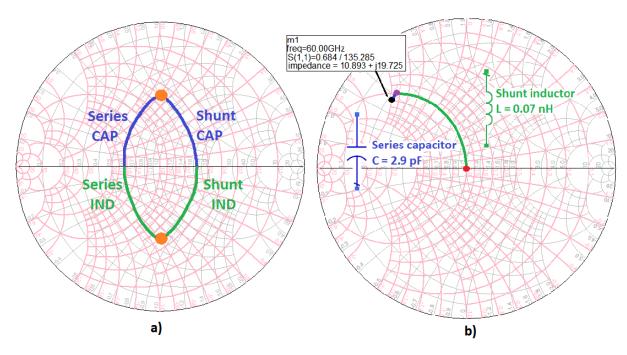

To evaluate the effect of the load impedance on the power delivered to it, load-pull approach is used. This allows to systematically vary the real and imaginary parts of the load impedance, so as to trace constant power contours in the abacus of the Smith chart (LEE, 2004). This set of contours are known as a load-pull diagram. This approach is used in non-linear analysis (e.g. for PAs), since in the linear analysis there are much simpler and faster methods (both in simulation and measurements), which already produce satisfactory results. The derivation of the analytical approach of this method was first proposed in (CRIPPS, 1983) for a PA in GaAs. The method by simulation consists of the addition of a tuner connected between the transistor output and the load. The tuner is configured to synthesize a wide range of impedances to be viewed at the output of the transistor, while the source remains as the conjugate complex of the input impedance. The latter is determined to be the voltage-current relationship of the input observed at the frequency of interest and at the point of maximum output power. In this analysis can be obtained the behavior of some of the key performance parameters of a PA for a wide range of synthesized impedances. In addition to the power contours, others like the PAE are also important to be analyzed. Figure 14 shows an example of a load-pull diagram for output power and PAE of a bipolar transistor of the technology used. As can be observed this analysis resembles contour lines, where the highest values are concentrated more to the center of the contours. Figure 15 shows the load-pull diagram under different input signals levels. As can be seen, the optimal output impedance in large-signal (red) differs from that small-signal (green) ones. So, the requirements to maximize the output power of the amplifier differ from those used to maximize power gain in small-signals.

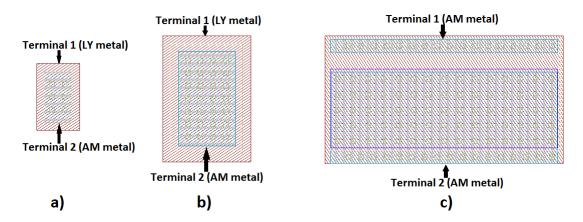

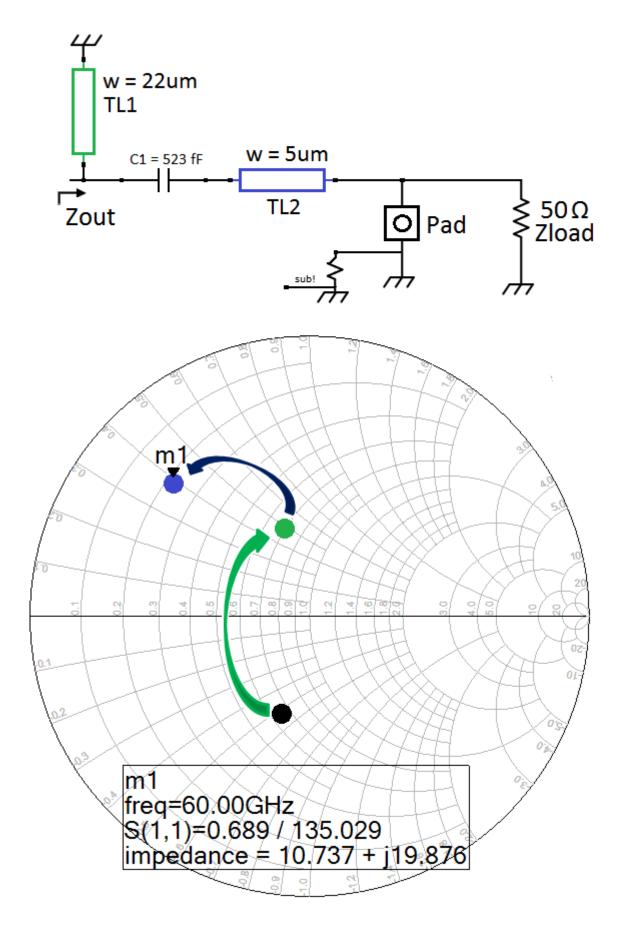

Figure 14 – Load-pull diagram for a bipolar cascode topology. Output power in red and PAE in blue.