Federal University of Paraíba

Department of Electrical Engineering

Master in Electrical Engineering

# Digitally Driven Control for Inductive Buck Converters in Portable Battery-Powered Applications

Rodrigo Pedroso Mendes

João Pessoa-PB, 29 de julho de 2024

## Rodrigo Pedroso Mendes

## Digitally Driven Control for Inductive Buck Converters in Portable Battery-Powered Applications

Dissertação de Mestrado apresentada ao Programa de Pós-Graduação em Engenharia Elétrica - PPGEE, da Universidade Federal da Paraíba - UFPB, como requisito parcial para a obtenção do título de Mestre em Engenharia Elétrica.

Orientador: Antônio Augusto Lisboa de Souza

Coorientador: Cícero da Rocha Souto

João Pessoa-PB 2024

#### Catalogação na publicação Seção de Catalogação e Classificação

M538d Mendes, Rodrigo Pedroso.

Digitally driven control for inductive buck converters in portable battery-powered applications / Rodrigo Pedroso Mendes. - João Pessoa, 2024.

165 f.: il.

Orientação: Antônio Augusto Lisboa de Souza. Coorientação: Cícero da Rocha Souto. Dissertação (Mestrado) - UFPB/CEAR.

1. Engenharia elétrica. 2. Conversor CC-CC. 3. Controle digital. 4. Indutivo. 5. Abaixador de tensão. 6. Conversor DPWM. 7. Conversor ADC com janela. I. Souza, Antônio Augusto Lisboa de. II. Souto, Cícero da Rocha. III. Título.

UFPB/BC CDU 621.3(043)

Elaborado por Larissa Silva Oliveira de Mesquita - CRB-15/746

## UNIVERSIDADE FEDERAL DA PARAÍBA – UFPB CENTRO DE ENERGIAS ALTERNATIVAS E RENOVÁVEIS - CEAR PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA - PPGEE

A Comissão Examinadora, abaixo assinada, aprova a Dissertação

## Digitally Driven Control for Inductive Buck Converters in **Portable Battery-Powered Applications**

Elaborada por

## Rodrigo Pedroso Mendes

como requisito parcial para obtenção do grau de Mestre em Engenharia Elétrica.

Comissão Examinadora:

Antônio Augusto Lisboa de Souza

Cícero da Rocha Souto

Darlan Alexandria Fernandes

Documento assinado digitalmente FERNANDO RANGEL DE SOUSA

Data: 02/08/2024 08:36:05-0300 CPF: \*\*\*.649.114-\*\* Verifique as assinaturas em https://v.ufsc.br

Fernando Rangel de Sousa

## Contents

|         | Introduction                                                                                          | 18 |

|---------|-------------------------------------------------------------------------------------------------------|----|

| 1       | BASIC CONCEPTS AND STATE OF THE ART                                                                   | 21 |

| 1.1     | Basic concepts                                                                                        | 21 |

| 1.1.1   | Conduction modes                                                                                      | 21 |

| 1.1.2   | Buck control schemes                                                                                  | 22 |

| 1.1.3   | Average model with voltage mode control in CCM                                                        | 23 |

| 1.1.3.1 | Approximate capacitor voltage ripple and inductor current ripple                                      | 25 |

| 1.1.3.2 | Continuous time small signal model                                                                    | 25 |

| 1.1.3.3 | Discrete time small signal model                                                                      | 27 |

| 1.1.4   | Control loop performance measurements                                                                 | 28 |

| 1.1.5   | Basic ADC performance measurements                                                                    | 28 |

| 1.2     | Summary of previous research on integrated digitally controlled                                       |    |

|         | DC-DC converters                                                                                      | 29 |

| 1.2.1   | A 0.6 V Input CCM/DCM Operating Digital Buck Converter in 40 nm CMOS                                  | 29 |

| 1.2.2   | A 65 nm, 1 A Buck Converter With Multi-Function SAR-ADC-Based                                         |    |

|         | CCM/PSK Digital Control Loop                                                                          | 31 |

| 1.2.3   | A 4 μA Quiescent-Current Dual-Mode Digitally Controlled Buck Converter                                |    |

|         | IC for Cellular Phone Applications                                                                    | 33 |

| 1.2.4   | $20~\mu\text{A}$ to $100~\text{mA}$ DC-DC Converter With $2.8\text{-}4.2~\text{V}$ Battery Supply for |    |

|         | Portable Applications in 45 nm CMOS                                                                   | 35 |

| 1.2.5   | A 180 nA Quiescent Current Digital Control Dual-Mode Buck Converter                                   |    |

|         | With a Pulse-Skipping Load Detector for Long-Range Applications                                       | 36 |

| 1.2.6   | A Digital Controller IC for High-Frequency DC-DC Switching Converters                                 | 38 |

| 1.2.7   | A 300 mA 14 mV-ripple digitally controlled buck converter using frequency                             |    |

|         | domain $\Delta\Sigma$ ADC and hybrid PWM generator                                                    | 40 |

| 1.2.8   | A Digitally Controlled DC-DC Buck Converter with Automatic Digital PFM                                |    |

|         | to PWM Transition Scheme                                                                              | 41 |

| 1.2.9   | All-Digital Current-Sensorless Multi-Mode DC-DC Converter for Battery                                 |    |

|         | Powered Applications                                                                                  | 42 |

| 1.2.10  | Digital Low Power Mode Control Technique for High Frequency                                           |    |

|         | Synchronous DC-DC Buck Converters                                                                     | 42 |

| 1.2.11  | Fully-Integrated Digital Average Current-Mode Control 12 V-to-1.x V Voltage                           |    |

|         | Regulator Module IC                                                                                   | 44 |

| 1.2.12   | Time-Based PWM Controller for Fully Integrated High Speed Switching DC-DC Converters – An Alternative to Conventional Analog and Digital |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|

|          | Controllers                                                                                                                              |

| 1.2.13   | A 90–240 MHz hysteretic controlled DC-DC buck converter with digital PLL                                                                 |

|          | frequency locking                                                                                                                        |

| 1.2.14   | Analysis of the reviewed literature                                                                                                      |

| 1.2.14.1 | Analog-to-Digital Converter (ADC)                                                                                                        |

| 1.2.14.2 | Digital Pulse Width Modulation (DPWM)                                                                                                    |

| 1.2.14.3 | Digital logic                                                                                                                            |

| 1.2.14.4 | Summary of the main parameters                                                                                                           |

| 2        | HIGH LEVEL DESIGN                                                                                                                        |

| 2.1      | Model of the power switches and drivers                                                                                                  |

| 2.2      | Inductor selection                                                                                                                       |

| 2.3      | Small signal analysis, compensation, and transient response 55                                                                           |

| 2.3.1    | PID tuning                                                                                                                               |

| 2.3.2    | Voltage reference step response                                                                                                          |

| 2.3.3    | Load step response                                                                                                                       |

| 2.3.4    | Bandwidth, output capacitor, and the maximum duty cycle change for one-bit                                                               |

|          | variation of the ADC                                                                                                                     |

| 2.3.5    | Capacitor selection                                                                                                                      |

| 2.3.6    | Input voltage step response                                                                                                              |

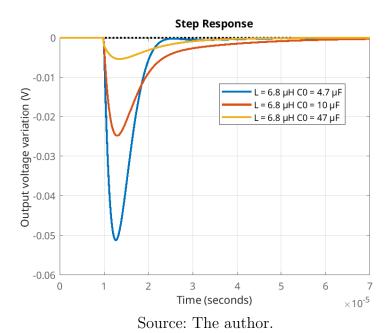

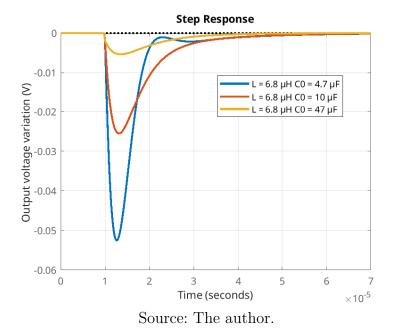

| 2.3.7    | Dependency on inductor and capacitor tolerances                                                                                          |

| 2.4      | Output voltage ripple                                                                                                                    |

| 2.5      | Quantization                                                                                                                             |

| 2.6      | Requirements for the ADC                                                                                                                 |

| 2.7      | Requirements for the DPWM                                                                                                                |

| 3        | IMPLEMENTATION 73                                                                                                                        |

| 3.1      | Analog to digital converter (ADC)                                                                                                        |

| 3.1.1    | Analysis of the relationship between the differential input and the accumulated                                                          |

|          | ADC output                                                                                                                               |

| 3.1.2    | Influence of the comparator offset                                                                                                       |

| 3.1.3    | Sizing of the devices, bias, supply and clock                                                                                            |

| 3.1.3.1  | Supply                                                                                                                                   |

| 3.1.3.2  | Sizing of transistors in the differential pair and clock frequency selection 83                                                          |

| 3.1.3.3  | Sizing of the NMOS mirrors                                                                                                               |

| 3.1.3.4  | Bias and sizing of the switches and capacitors                                                                                           |

| 3.2      | DPWM 83                                                                                                                                  |

| 3.3      | Digitally Controlled Logic                                                                                                               |

| 4          | RESULTS                                                                |

|------------|------------------------------------------------------------------------|

| 4.1        | ADC                                                                    |

| 4.1.1      | Typical process, supply, and temperature                               |

| 4.1.2      | Dependency on temperature                                              |

| 4.1.3      | Dependency on supply                                                   |

| 4.1.4      | Dependency on process                                                  |

| 4.1.5      | Dependency on process, supply, and temperature                         |

| 4.1.6      | Sensitivity to mismatch                                                |

| 4.1.7      | Estimated Area                                                         |

| 4.2        | <b>DPWM</b>                                                            |

| 4.2.1      | Typical process, supply, buck input voltage, and temperature 99        |

| 4.2.2      | Dependency on temperature                                              |

| 4.2.3      | Dependency on the buck input voltage                                   |

| 4.2.4      | Dependency on process                                                  |

| 4.2.5      | Dependency on process, buck input voltage, supply, and temperature 103 |

| 4.2.6      | Sensitivity to mismatch                                                |

| 4.2.7      | Estimated Area                                                         |

| 4.3        | System level simulations                                               |

| 4.3.1      | Load Transient                                                         |

| 4.3.2      | Supply Transient                                                       |

| 4.3.3      | Step in the voltage reference                                          |

| 4.3.4      | Dithering                                                              |

| 5          | DISCUSSIONS                                                            |

| 5.1        | ADC                                                                    |

| 5.2        | DPWM                                                                   |

| 5.3        | System                                                                 |

|            | Conclusions and Future work                                            |

| 5.3.1      | Future work                                                            |

|            | BIBLIOGRAPHY 122                                                       |

|            | ANNEX A – POWER SWITCH MODEL                                           |

| B.1<br>B.2 | ANNEX B – ADC COMPARATOR AND CONTROL                                   |

|            | ANNEX C – COMPARATOR UTILIZED IN THE DPWM 131                          |

| ANNEX D – MATLAB MODEL FOR ANALYSIS OF THE ADC . 132                    |

|-------------------------------------------------------------------------|

| ANNEX E – SYNTHESIZABLE VERILOG MODEL OF THE DIGITALLY CONTROLLED LOGIC |

| ANNEX F – ADC TEST BENCH STIMULUS                                       |

| ANNEX G – DPWM TEST BENCH STIMULUS 159                                  |

| ANNEX H – SYSTEM LEVEL TEST BENCH STIMULUS 163                          |

## List of Figures

| Figure 1 – Simplified block diagram of a step-down switched-inductor DC-DC   |    |

|------------------------------------------------------------------------------|----|

| converter                                                                    | 21 |

| Figure 2 – Inductor charge stage                                             | 22 |

| Figure 3 – Inductor discharge stage                                          | 22 |

| Figure 4 – Equivalent circuit for null inductor current in DCM               | 22 |

| Figure 5 – PWM and PFM modes                                                 | 22 |

| Figure 6 – Inductor current in continuous conduction mode                    | 23 |

| Figure 7 – Inductor charge stage including parasitic resistances             | 23 |

| Figure 8 – Inductor discharge stage including parasitic resistances          | 24 |

| Figure 9 – Block diagram of the converter [8]                                | 30 |

| Figure 10 – Block diagram of the PWM controller [8]                          | 30 |

| Figure 11 – Timing diagram [8]                                               | 31 |

| Figure 12 – Simplified block diagram of the DC-DC converter proposed in [9]  | 32 |

| Figure 13 – Block diagram of the digital controller [9]                      | 32 |

| Figure 14 – Architecture proposed by Jinwen Xiao et al. [3]                  | 34 |

| Figure 15 – Ring ADC proposed by Jinwen Xiao et al. [3]                      | 34 |

| Figure 16 – DPWM proposed by Jinwen Xiao et al. [3]                          | 34 |

| Figure 17 – Architecture proposed by Saurav et al. [10]                      | 35 |

| Figure 18 – Digital to Pulse Width Modulation proposed by Saurav et al. [10] | 36 |

| Figure 19 – Architecture proposed by TSAI, TH. et al. [11]                   | 37 |

| Figure 20 – Architecture proposed by CHEN, N. et al. [12]                    | 38 |

| Figure 21 – ADC proposed by CHEN, N. et al. [12]                             | 38 |

| Figure 22 – Control proposed by CHEN, N. et al. [12]                         | 39 |

| Figure 23 – DPWM proposed by CHEN, N. et al. [12]                            | 39 |

| Figure 24 – Architecture proposed by AHMAD, H. H. and BAKKALOGLU, B. [13].   | 40 |

| Figure 25 – Architecture proposed by BEOHAR, N. et al. [14].                 | 41 |

| Figure 26 – ADC proposed by BEOHAR, N. et al. [14]                           | 42 |

| Figure 27 – Architecture proposed by YAO, GS. et al. [15]                    | 43 |

| Figure 28 – Architecture proposed by BOTTAMEDI, D. et al. [16]               | 43 |

| Figure 29 – Architecture proposed by VEKSLENDER, T. et al. [17]              | 44 |

| Figure 30 – ADC proposed by VEKSLENDER, T. et al. [17]                       | 45 |

| Figure 31 – DPWM proposed by VEKSLENDER, T. et al. [17]                      | 45 |

| Figure 32 – Architecture proposed by KHAN, Q. A. et al. [18]                 | 47 |

| Figure 33 – Architecture proposed by LI, P. et al. [19]                      | 48 |

| Figure 34 – Block diagram of a digitally controlled DC-DC                    | 51 |

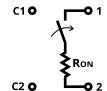

| Figure 35 – Power switches high level model                                  | 52 |

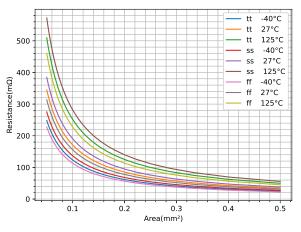

| Figure 36 – | nfet50x resistance                                                                            | 52 |

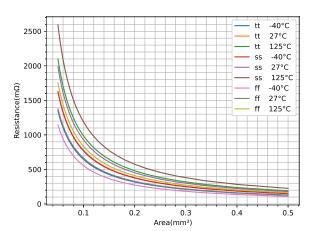

|-------------|-----------------------------------------------------------------------------------------------|----|

| Figure 37 – | pfet50x resistance                                                                            | 52 |

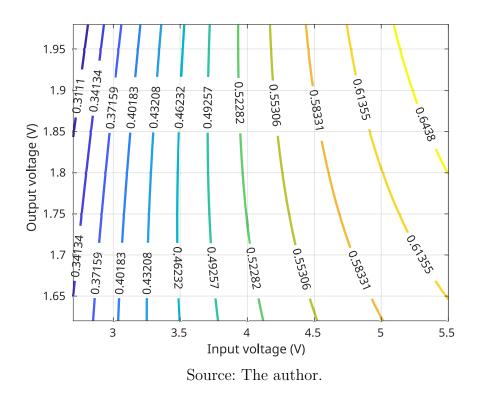

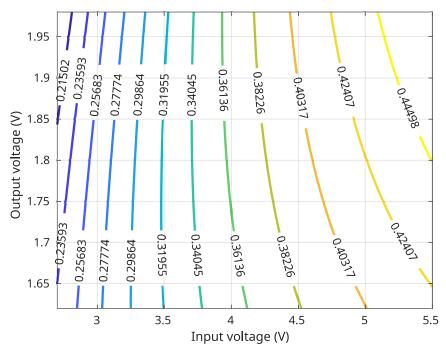

| Figure 38 – | Contour plot of ratio $r$ for L = 4.7 $\mu H$ and different combinations of                   |    |

|             | input and output voltages                                                                     | 54 |

| Figure 39 – | Contour plot of ratio $r$ for L = 6.8 $\mu H$ and different combinations of                   |    |

|             | input and output voltages                                                                     | 54 |

| Figure 40 – | Contour plot of ratio $r$ for L = 8.2 $\mu H$ and different combinations of                   |    |

|             | input and output voltages                                                                     | 55 |

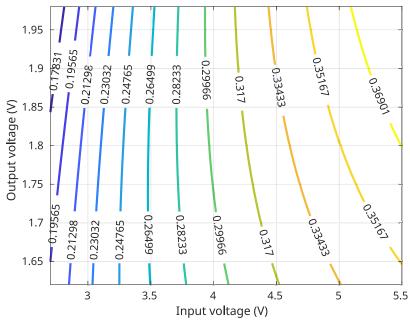

| Figure 41 – | Bode plot of $H(s)$                                                                           | 56 |

| Figure 42 – | Comparison between different methods of obtaining $H(z)$                                      | 57 |

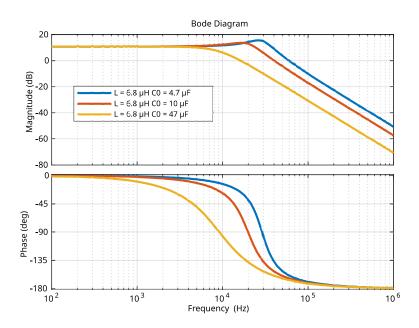

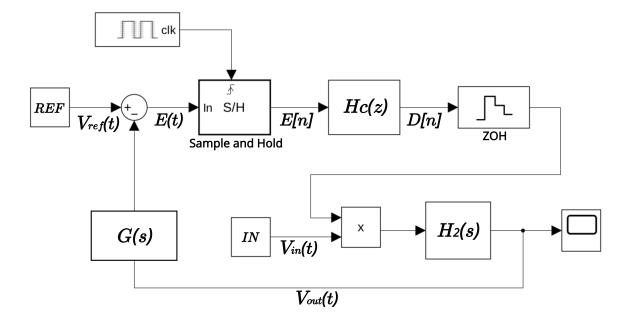

| Figure 43 – | Average model small signal block diagram using Simulink <sup>®</sup>                          | 58 |

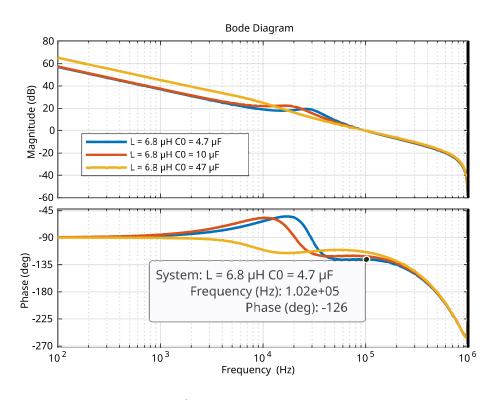

| Figure 44 – | Bode plot of $Hc(z) \cdot H(z)$ for the PID tuned using the MATLAB®                           |    |

|             | pidtune function                                                                              | 59 |

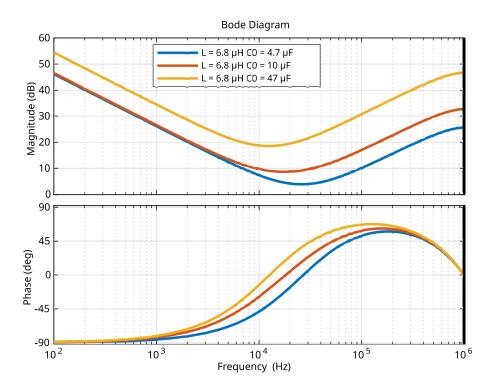

| Figure 45 – | Bode plot of $Hc(z)$ for the PID tuned using the MATLAB® pidtune                              |    |

|             | function                                                                                      | 60 |

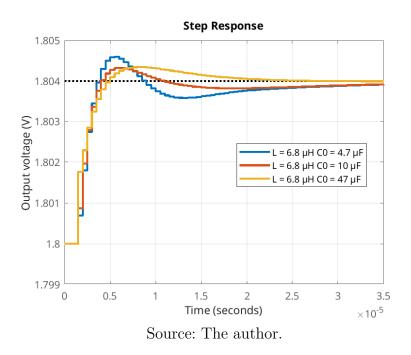

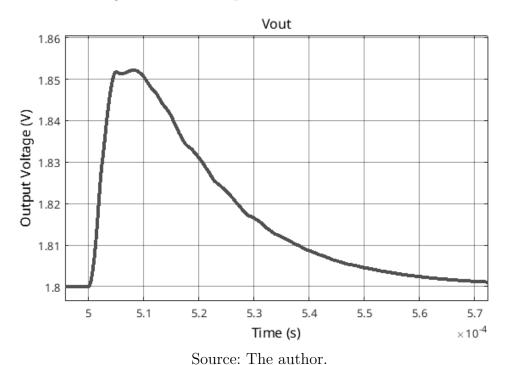

| Figure 46 – | Closed loop step response of $Hc(z) \cdot H(z)$ for the PID tuned using the                   |    |

|             | MATLAB® pidtune function                                                                      | 61 |

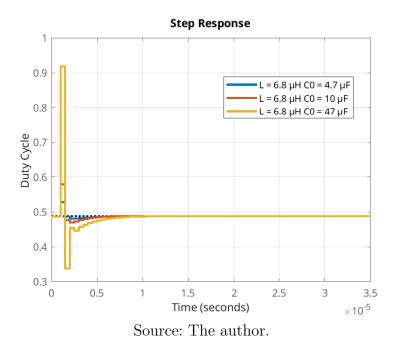

| Figure 47 – | Duty cycle of the closed loop step response of $Hc(z) \cdot H(z)$ for the PID                 |    |

|             | tuned using the MATLAB® pidtune function                                                      | 61 |

| Figure 48 – | Equivalent circuit including output current                                                   | 62 |

| Figure 49 – | Load transient for the PID tuned using the MATLAB® pidtune function                           |    |

|             |                                                                                               | 63 |

| Figure 50 – | Load transient for the PID tuned using the MATLAB® pidtune function                           |    |

|             | for $R = 1M \Omega$                                                                           | 63 |

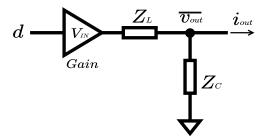

| Figure 51 – | Large signal block diagram using Simulink® that includes input voltage                        |    |

|             | dependency                                                                                    | 66 |

| Figure 52 – | Output voltage under a step of 3.7 to 5.5 V in the input voltage for the                      |    |

|             |                                                                                               | 67 |

|             |                                                                                               | 67 |

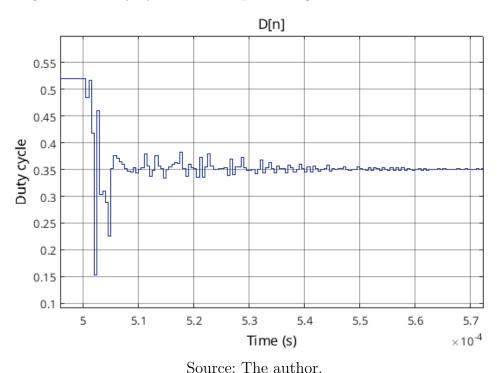

| Figure 54 – | Bode plot of $Hc(z) \cdot H(z)$ for the PID tuned using the MATLAB®                           |    |

|             | pidtune function for $L=6.8~\mu\mathrm{H}$ and $C_O=13.2~\mu\mathrm{F}$ including tolerances. | 68 |

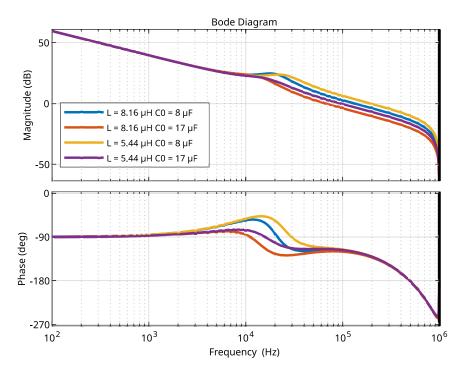

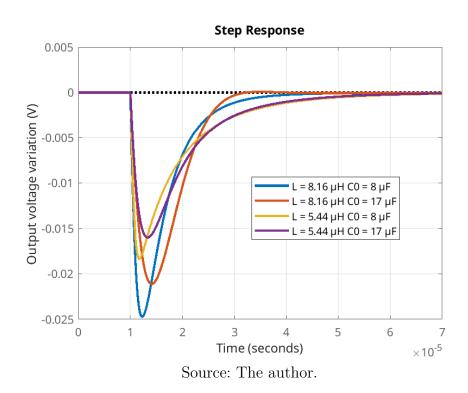

| Figure 55 – | Load transient for the PID tuned using the MATLAB® pidtune function                           |    |

|             |                                                                                               | 68 |

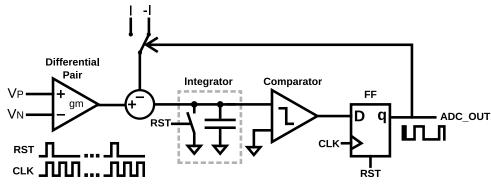

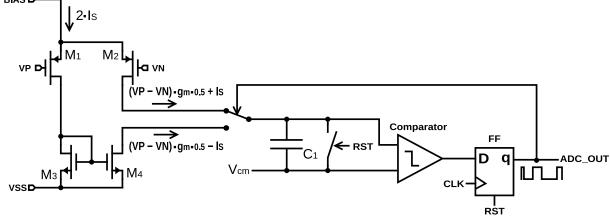

|             |                                                                                               | 74 |

| _           | • •                                                                                           | 74 |

|             | · ·                                                                                           | 75 |

|             |                                                                                               | 76 |

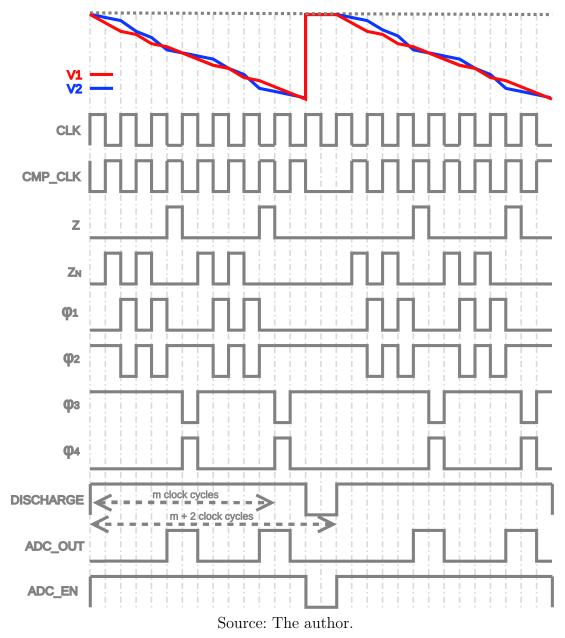

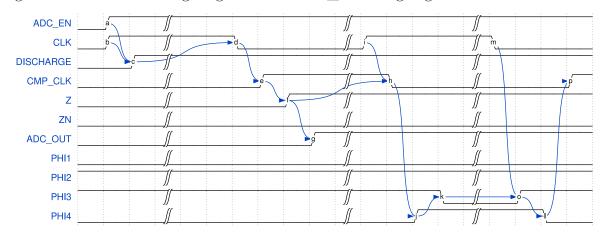

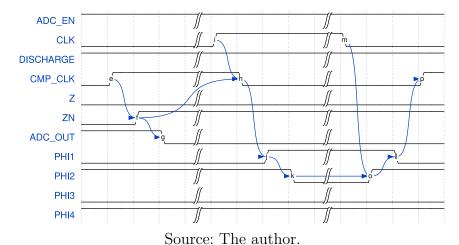

| Figure 60 – | Detailed timing diagram after ADC_EN rising edge and also when $V_1$                          |    |

|             | $> V_2$                                                                                       | 77 |

| Figure 61 – | Detailed timing diagram when $V_1 < V_2 \dots \dots 77$                                 |

|-------------|-----------------------------------------------------------------------------------------|

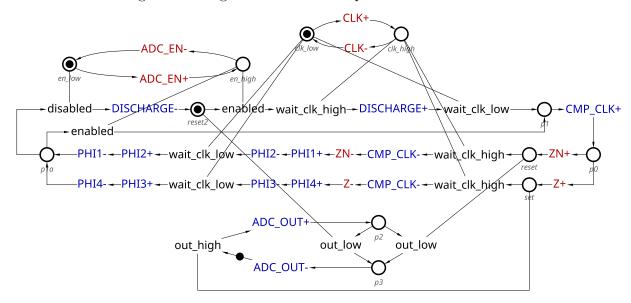

| Figure 62 – | Signal Transition Graph of the ADC control                                              |

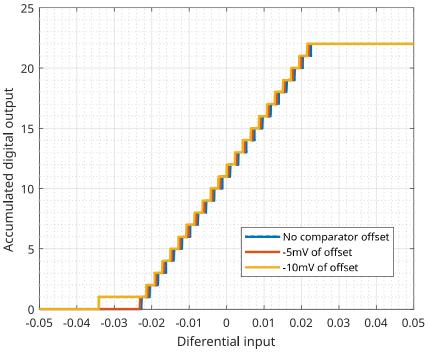

| Figure 63 – | ADC transfer curve including effects of offset in the clocked comparator. $80$          |

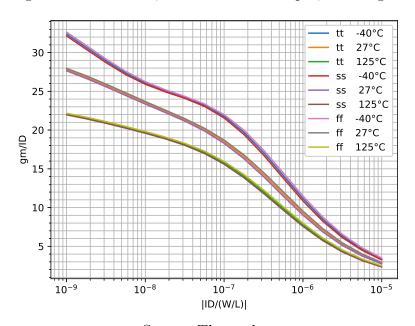

| Figure 64 – | PMOS transistor transconductance divided by the drain current as a                      |

|             | function of the drain current divided by the width to length ratio. Drain               |

|             | to source voltage was set to 0.9 V, width was set to 1 $\mu m,$ and length              |

|             | also to 1 μm                                                                            |

| Figure 65 – | Block diagram of the proposed DPWM                                                      |

| Figure 66 – | Proposed schematic of the unit capacitor                                                |

| Figure 67 – | Proposed block diagram of the capacitor matrix 86                                       |

| Figure 68 – | Proposed DPWM circuit                                                                   |

| Figure 69 – | DPWM timing diagram                                                                     |

| Figure 70 – | Detailed block diagram of the digitally driven control                                  |

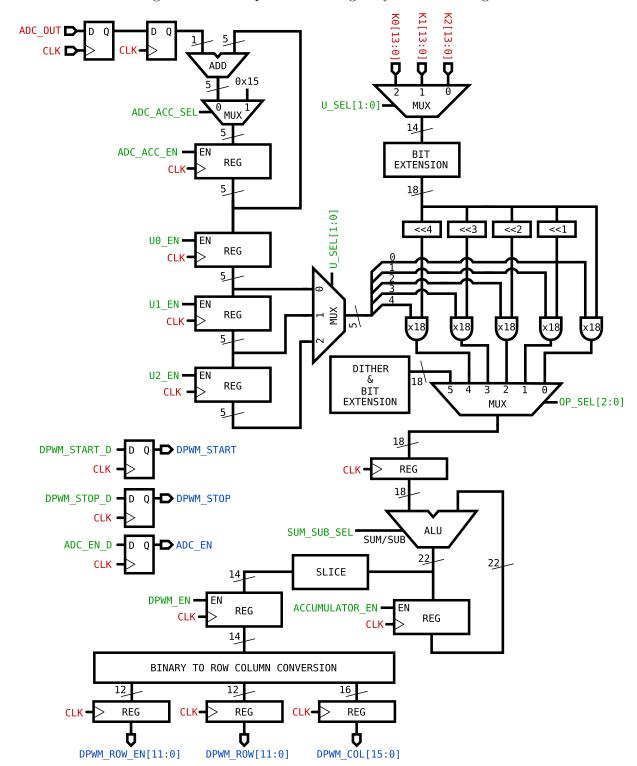

| Figure 71 – | Datapath of the digitally controlled logic                                              |

| Figure 72 – | Timing diagram of the digitally controlled logic state machine 90                       |

| Figure 73 – | Diagram of the ADC test bench                                                           |

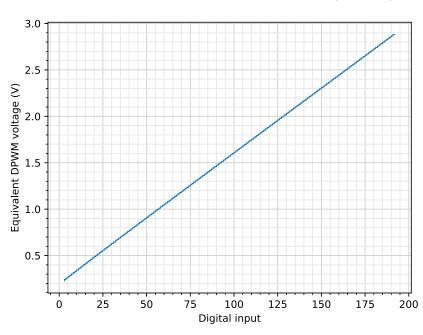

| Figure 74 – | Typical ADC transfer curve                                                              |

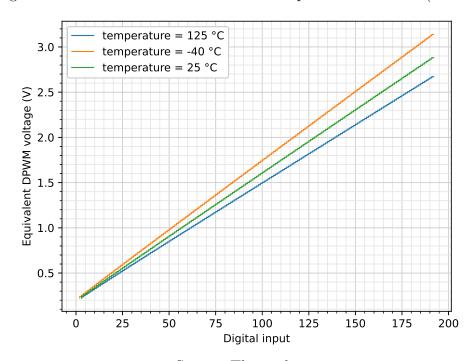

| Figure 75 – | ADC transfer curve with temperature variation                                           |

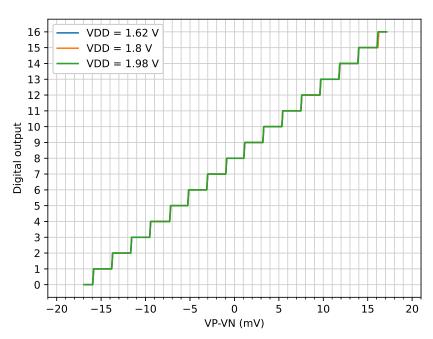

| Figure 76 – | ADC transfer curve with supply variation                                                |

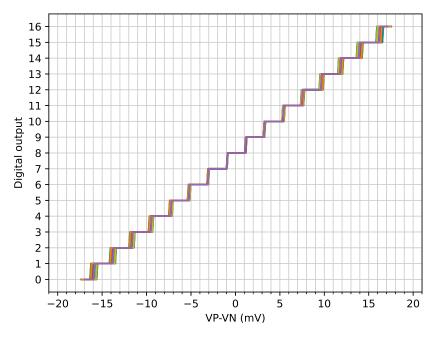

| Figure 77 – | ADC transfer curve with process variation                                               |

| Figure 78 – | ADC transfer curve with process, supply, and temperature variation 96                   |

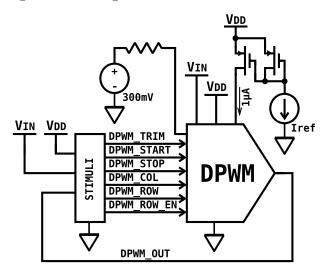

| Figure 79 – | Diagram of the DPWM test bench                                                          |

| Figure 80 – | Typical DPWM transfer curve $(D \cdot V_{IN})$                                          |

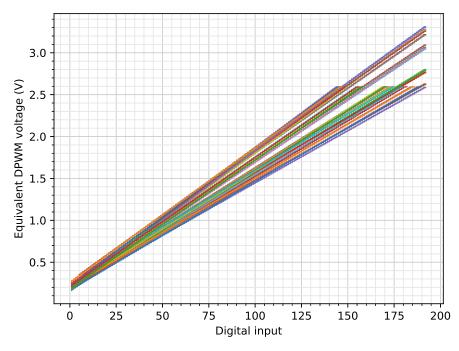

| Figure 81 – | DPWM transfer curve with temperature variation $(D \cdot V_{IN})$ 100                   |

| Figure 82 – | DPWM transfer curve with buck input voltage variation $(D \cdot V_{IN})$ 101            |

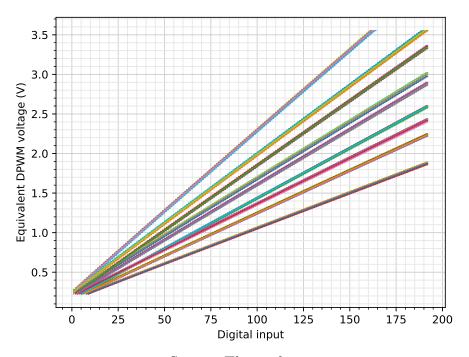

| Figure 83 – | DPWM transfer curve including process variation before trimming                         |

|             | $(D \cdot V_{IN})$                                                                      |

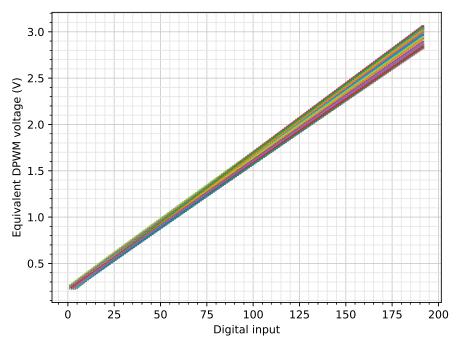

| Figure 84 – | DPWM transfer curve including process variation after trimming $(D \cdot V_{IN})$ . 103 |

| Figure 85 – | DPWM transfer curve with process (after trimming), supply, buck input                   |

|             | voltage, and temperature variation $(D \cdot V_{IN})$                                   |

| Figure 86 – | Diagram of the system level test bench                                                  |

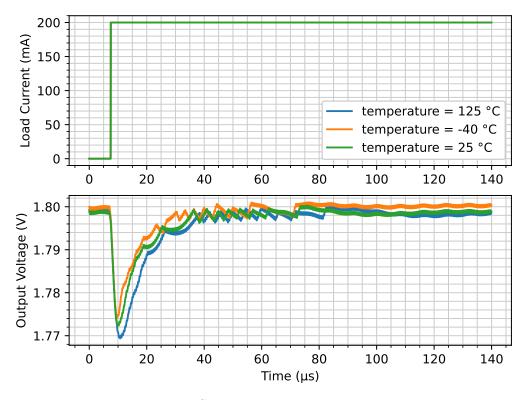

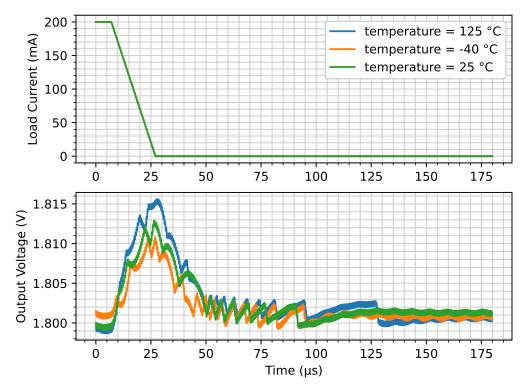

| Figure 87 – | Output voltage undershoot when the load current varies from 0 A to                      |

|             | 200 mA in 100 ns                                                                        |

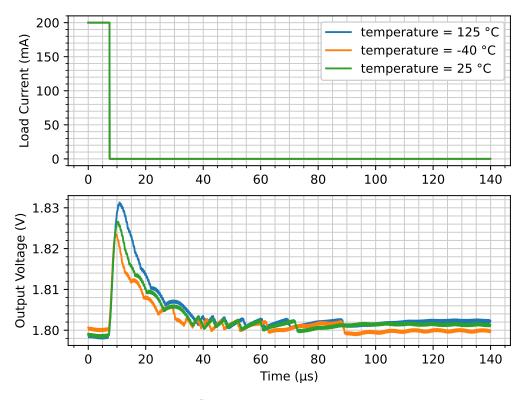

| Figure 88 – | Output voltage overshoot when the load current varies from 200 mA to                    |

|             | 0 A in 100 ns                                                                           |

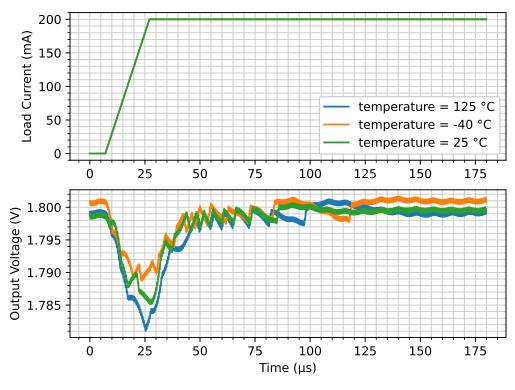

| Figure 89 – | Output voltage undershoot when the load current varies from 0 A to                      |

|             | 200 mA in 20 μs                                                                         |

| Figure 90 – | Output voltage overshoot when the load current varies from 200 mA to                    |

|             | 0 A in 20 μs                                                                            |

|             |                                                                                         |

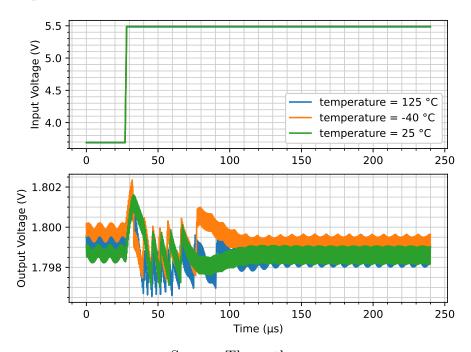

| Figure 91 – | Output voltage transient when the input voltage varies from 3.7 V to              |     |

|-------------|-----------------------------------------------------------------------------------|-----|

|             | 5.5 V in 1 µs                                                                     | 109 |

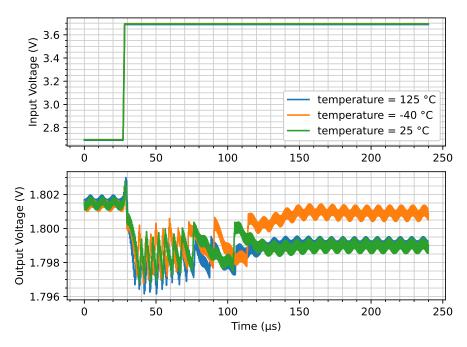

| Figure 92 – | Output voltage transient when the input voltage varies from 2.5 V to              |     |

|             | 3.7 V in 1 µs                                                                     | 109 |

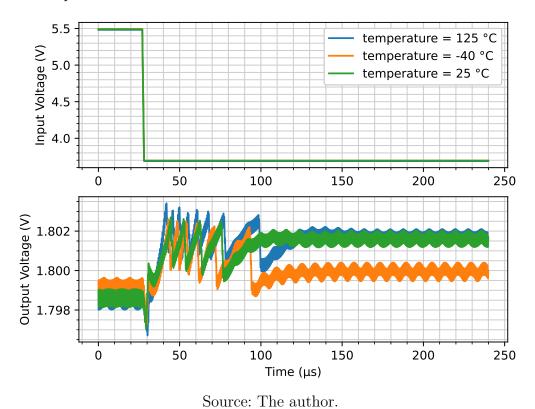

| Figure 93 – | Output voltage transient when the input voltage varies from $5.5~\mathrm{V}$ to   |     |

|             | $3.7~V$ in 1 $\mu s.$                                                             | 110 |

| Figure 94 – | Output voltage transient when the input voltage varies from $3.7~\mathrm{V}$ to   |     |

|             | 2.7 V in 1 μs                                                                     | 110 |

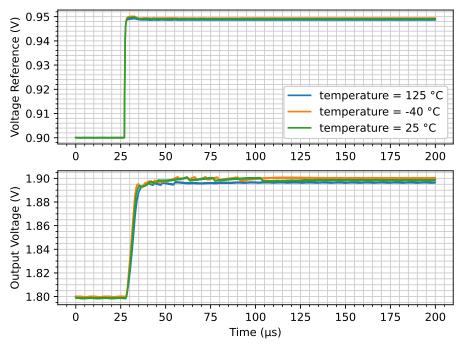

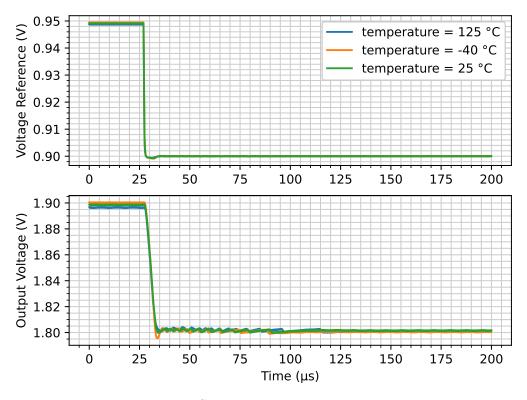

| Figure 95 – | Output voltage overshoot when the voltage reference varies from 0.9 V $$          |     |

|             | to 0.95 V in 1 $\mu s.$                                                           | 111 |

| Figure 96 – | Output voltage overshoot when the voltage reference varies from 0.85 V $$         |     |

|             | to 0.9 V in 1 μs                                                                  | 111 |

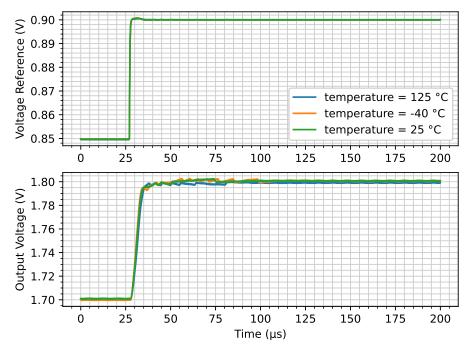

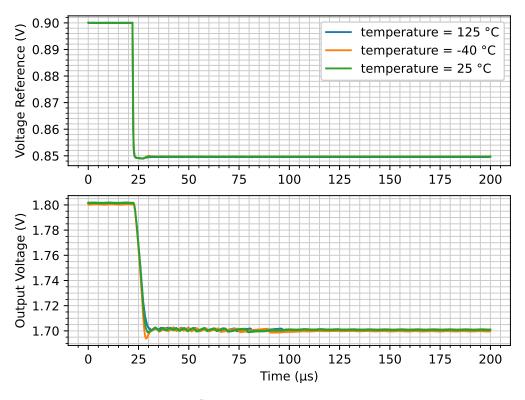

| Figure 97 – | Output voltage Undershoot when the voltage reference varies from                  |     |

|             | 0.95 V to 0.9 V in 1 $\mu$ s                                                      | 112 |

| Figure 98 – | Output voltage Undershoot when the voltage reference varies from $0.9~\mathrm{V}$ |     |

|             | to 0.85 V in 1 µs                                                                 | 112 |

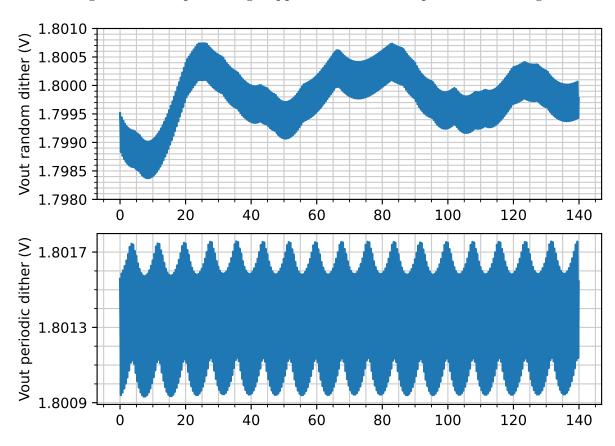

| Figure 99 – | Output voltage ripple for random and periodic dithering                           | 113 |

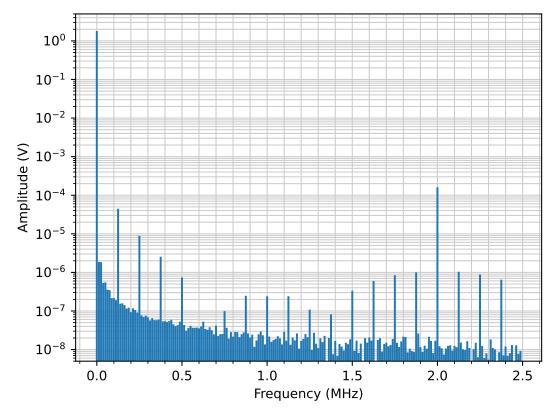

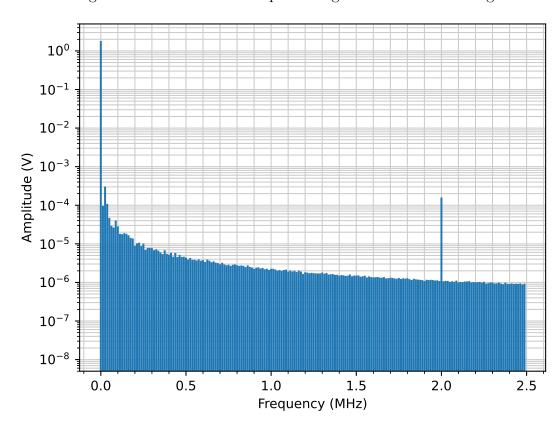

| Figure 100- | -FFT of the output voltage for periodic dithering                                 | 114 |

|             | -FFT of the output voltage for random dithering                                   |     |

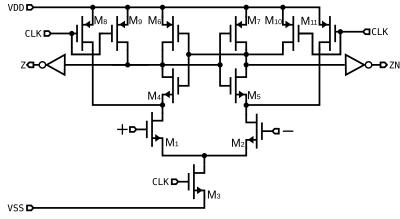

| Figure 102- | -Proposed clocked comparator for the ADC                                          | 130 |

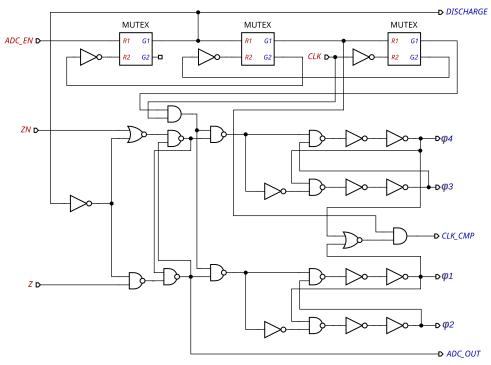

|             | Gate level implementation of the ADC control                                      |     |

| Figure 104- | -Proposed comparator for the DPWM                                                 | 131 |

|             |                                                                                   |     |

## List of Tables

| Table 1 – Summary of the main parameters in [8]                                              |

|----------------------------------------------------------------------------------------------|

| Table 2 - Summary of the main parameters in [9]                                              |

| Table 3 - Summary of the main parameters in [3]                                              |

| Table 4 - Summary of the main parameters in [10]                                             |

| Table 5 - Summary of the main parameters in [11]                                             |

| Table 6 - Summary of the main parameters in [12]                                             |

| Table 7 - Summary of the main parameters in [13]                                             |

| Table 8 - Summary of the main parameters in [14]                                             |

| Table 9 - Summary of the main parameters in [15]                                             |

| Table 10 – Some parameters in [16]                                                           |

| Table 11 – Summary of the main parameters in [17]                                            |

| Table 12 – Summary of the main parameters in [19]                                            |

| Table 13 – Comparison between the main parameters                                            |

| Table 14 $-$ Summary of the commercial inductor parameters from Murata 53                    |

| Table 15 – Summary of the PID tuning using the first method                                  |

| Table 16 – Summary of the PID tuning using the MATLAB® pidtune function 59                   |

| Table 17 – Output voltage undershoot for 200 mA current step                                 |

| Table $18$ – Maximum duty cycle variation for a step of $1\ \mathrm{mV}$ in the input of the |

| controller                                                                                   |

| Table 19 – Summary of some commercial capacitor parameters from Murata 65                    |

| Table 20 – Typical ADC Parameters                                                            |

| Table 21 – ADC Parameters with temperature variation                                         |

| Table 22 – ADC Parameters with supply variation                                              |

| Table 23 – ADC Parameters with process variation                                             |

| Table 24 – ADC Parameters with process, supply, and temperature variation 96                 |

| Table 25 – Standard deviation of the ADC parameters taking into account the                  |

| mismatch                                                                                     |

| Table 26 – Typical DPWM Parameters                                                           |

| Table 27 – DPWM Parameters with temperature variation                                        |

| Table 28 – DPWM Parameters with buck input voltage variation                                 |

| Table 29 – DPWM Parameters with process variation before trimming 102                        |

| Table 30 – DPWM Parameters with process variation after trimming                             |

| Table 31 – DPWM Parameters with process (after trimming), supply, and temperature            |

| variation                                                                                    |

| Table 32 – Standard deviation of the DPWM Parameters taking into account the                 |

| mismatch                                                                                     |

| Table 33 – | Comparison | between | the m | nain | parai | meters | of | this | work | and | the | reviewed |       |

|------------|------------|---------|-------|------|-------|--------|----|------|------|-----|-----|----------|-------|

|            | literature |         |       |      |       |        |    |      |      |     |     |          | . 115 |

## **Abstract**

In this work, a digitally driven control system for an integrated fixed-frequency inductive buck converter is presented. A comprehensive review of small signal modeling and compensation is included, with a digital control based on a standard Proportional Integral Derivative (PID) controller. To enable this control, focus was given on optimizing the Analog to Digital Converter (ADC) and the Digital Pulse Width Modulator (DPWM) for the intended application.

The novel ADC architecture achieves a typical step size of 2.136 mV, a quiescent current of 15.5  $\mu$ A and an estimated area of 0.0088 mm<sup>2</sup>. The proposed DPWM incorporates a feed-forward of the input voltage to boost line regulation and includes a thermometer encoded capacitor array to improve Differential Nonlinearity (DNL). The typical quiescent current of the DPWM is 35.1  $\mu$ A with an estimated area of 0.0439 mm<sup>2</sup>.

Special care was taken to ensure the robustness of the ADC and DPWM against mismatch, process, temperature, and supply voltage variations. The proposed control architecture can be applied to implement DC-DC converters for portable applications, powered either by a Lithium-Ion battery (2.7 V to 4.2 V) or, during the charging of the battery, via a USB port (4.7 V to 5.5 V). The load current may vary from 0 to 200 mA, the switching frequency is 2 MHz, and the output voltage aligns with the range of the native transistors available in the CMOS 180 nm technology adopted (1.62 V to 1.98 V).

**Keywords**: DC-DC Converter, digital control, inductive, step-down, digital pulse width modulation, window analog to digital converter, buck.

## Resumo

Neste trabalho, é apresentado um sistema de controle acionado digitalmente para um conversor indutivo abaixador integrado de frequência fixa. Uma revisão abrangente da modelagem de pequenos sinais e da compensação é incluída, utilizando um controlador Proporcional Integral Derivativo (PID) digital padrão. Para viabilizar esse controle, focou-se na otimização do Conversor Analógico para Digital (ADC) e do Modulador de Largura de Pulso Digital (DPWM) para a aplicação pretendida.

A nova arquitetura do ADC alcança um tamanho de passo típico de 2,136 mV, uma corrente quiescente de 15,5  $\mu$ A e uma área estimada de 0,0088 mm². O DPWM proposto incorpora um mecanismo de avanço da tensão de entrada para melhorar a regulação de linha e inclui uma matriz de capacitores com código termométrico para melhorar a Não Linearidade Diferencial (DNL). A corrente de quiescente típica do DPWM é de 35,1  $\mu$ A, com uma área estimada de 0,0439 mm².

Foi dedicada atenção especial para garantir a robustez do ADC e do DPWM contra variações de descasamento, processo, temperatura e tensão de alimentação. A arquitetura de controle proposta pode ser aplicada na implementação de conversores CC-CC para aplicações portáteis alimentadas por uma bateria de íon de lítio (2,7 V a 4,2 V) ou, durante o carregamento da bateria, via uma porta USB (4,7 V a 5,5 V). A corrente de carga pode variar de 0 a 200 mA, a frequência de comutação é de 2 MHz, e a tensão de saída está alinhada com os transistores nativos disponíveis na tecnologia CMOS de 180 nm que foi adotada (1,62 V a 1,98 V).

**Keywords**: Conversor CC-CC, controle digital, indutivo, abaixador de tensão, conversor digital para modulação em largura de pulso, conversor analógico digial com janela.

## List of abbreviations and acronyms

AC Alternating Current

ACM Average Current Mode

ADC Analog-to-Digital Converter

ALU Arithmetic Logic Unit

AMS Analog Mixed Signal

CCM Continuous Conduction Mode

CMOS Complementary Metal-Oxide-Semiconductor

DAC Digital-to-Analog Converter

DC Direct Current

DCM Discontinuous Conduction Mode

DPWM Digital Pulse Width Modulation

DNL Differential Nonlinearity

DRC Design Rule Check

DVFS Dynamic Voltage and Frequency Scaling

ESR Equivalent Series Resistance

GM Gain Margin

HDL Hardware Description Language

IC Integrated Circuit

INL Integral Nonlinearity

IQ Quiescent Current

LDO Low Dropout Regulator

LHS Latin Hypercube Sampling

LPM Low Power Mode

MOS Metal-Oxide-Semiconductor

MSPS Mega Samples Per Second

MUX Multiplexer

NMOS N-type Metal-Oxide-Semiconductor

PSAOT Pulse-Skipping Adaptive On-Time

PSAM Pulse-Skipping Asynchronous Mode

PDK Process Design Kit

PFM Pulse Frequency Modulation

PI Proportional-Integral

PID Proportional-Integral-Derivative

PLL Phase-Locked Loop

PM Phase Margin

PMIC Power Management Integrated Circuit

PMOS P-type Metal-Oxide-Semiconductor

PWM Pulse Width Modulation

RC Resistor-Capacitor

RMS Root Mean Square

SAR Successive Approximation Register

SoC System on Chip

SPL Skip Prevention Logic

SPS Samples Per Second

SR Set-Reset

STG Signal Transition Graph

USB Universal Serial Bus

VCO Voltage-Controlled Oscillator

ZOH Zero-Order Hold

## Introduction

Battery-powered portable devices have become essential in our daily tasks, serving as tools for managing finances, appointments, communication, and other tasks. Inside these devices, there is a crucial component known as the Power Management Integrated Circuit (PMIC). The PMIC not only manages the charging of the battery but also converts the voltage levels to meet the different requirements of the system.

To accomplish the tasks, PMICs typically incorporate one or more DC-DC converters (a device capable of converting a voltage level into another). A step-down DC-DC converter is employed to reduce the input voltage, providing a lower output voltage. Conversely, a step-up DC-DC converter elevates the input voltage as needed.

The most basic DC-DC converter achievable with semiconductor components is a voltage regulator and it works by converting the extra power from the difference between the input and output voltage into heat. Regulators can only work as a step-down DC-DC by construction and the maximum theoretical efficiency is limited by the ratio between the output and input voltages  $(V_{out}/V_{in})$ .

For the construction of step-up DC-DC converters or highly efficient counterparts, switched architectures are required. These architectures cyclically store and reuse the energy available in capacitors (switched-capacitor converters) or inductors (switched-inductor converters).

The switching frequency can be constant or variable depending on the choice of the controller topology. Variable frequency topologies are optimized for low power consumption or designed to spread the spectrum of the switching noise. On the other hand, fixed frequency topologies provide good load regulation, low ripple, and maintain the switching noise at a specific frequency with a higher current consumption.

The focus of this work was a digital control for fixed frequency converters. Therefore, instead of defining methods to determine which application requires a fixed frequency DC-DC or a variable frequency one, our concern was the implementation of the control loop in the digital domain, providing that a fixed frequency converter is better suitable for the intended application.

As a matter of fact, most applications need a DC-DC converter that operates both in fixed and variable switching frequency modes. A communication device, for example, need a low ripple supply when transmitting, but it tolerates a higher ripple supply during idle in order to save power. Therefore, at least one mode of operation that involves fixed frequency control loop will be present in most battery powered applications.

Introduction 19

## Motivation

Competition in the portable device market is tight: users demand higher processing power and longer battery life. Dynamic Voltage and Frequency Scaling (DVFS), which consists in adjusting the microprocessor input voltage and frequency according to the work load, is one of the solutions created to address these issues. This technique requires devices capable of efficiently converting the 2.7 V - 4.2 V voltage from a Lithium-ion battery in a dynamically configurable lower voltage. The control loop of converters for these applications are traditionally implemented in the analog domain due to the difficulty of building low power ADC and DPWM, but the implementation of the control loop in the digital domain can provide more flexibility and re-usability. Our main motivation was thus to look for (and adapt) ADC and DPWM low-power topologies suitable to the indented application, as a mean for enabling a control loop in the digital domain.

## **Tools**

Since the cost of manufacturing an integrated circuit is high, foundries provide Process Design Kits (PDKs) with simulation models that have a fairly good accuracy, which for this work is a PDK of the Global Foundries 180 nm process. The work was carried out by means of computer modeling of the proposed circuits with the Virtuoso software from Cadence<sup>®</sup>, which is a well known and established software provider for the microelectronics field. From Virtuoso, Schematic-XL, Maestro, and Layout-XL were mainly used. Spectre with Xcelium integration was also installed in order to perform Verilog-AMS simulations. For high level modeling, the MATLAB<sup>®</sup> was used.

In addition, artificial intelligence tools, specifically ChatGPT 3.7, were used to verify the clarity of the text and suggest rephrasing to improve readability. It is important to note that no content presented in this work was generated by artificial intelligence.

## Goals

The goal of this work was to design a digitally driven control for a fixed frequency buck converter in the context of PMIC for portable battery-powered applications. The control loop consists of an ADC, a digital state machine with a standard Proportional Integral Derivative (PID) logic, and a DPWM converter. The desirable performance is described below:

- Input voltage between 2.7 V and 5.5 V. Typical 3.7 V.

- Output voltage between 1.62 V and 1.98 V. Typical 1.8 V.

Introduction 20

- Load current between 0 to 200 mA.

- Switching frequency of 2 MHz.

- The sum of the ADC accuracy, line transients variations, and load transients variations must be within 2% of the voltage reference once the voltage reference is settled. The system can violate the  $\pm 2\%$  specification when the voltage reference is being updated.

- Minimize power consumption.

- Reduce complexity and circuit area whenever possible.

## Text structure

The remaining document is structured as follows:

- Chapter 1: Review of the theory and the state of the art.

- Chapter 2: High level design and establishment of high level guidelines for the design of the ADC, DPWM, and digital PID.

- Chapter 3: Development of the implementation details of the ADC, DPWM, and digital PID.

- Chapter 4: Result of the ADC, DPWM, and top level simulations.

- Chapter 5: Discussion of the results.

## 1 Basic concepts and State of the art

This chapter summarizes basic concepts of buck converters and some previous research on the subject of integrated digitally controlled buck converters.

## 1.1 Basic concepts

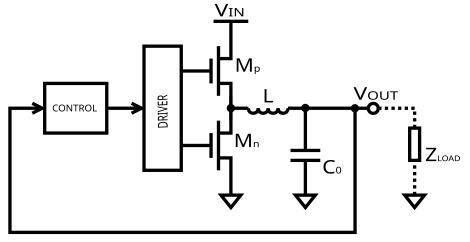

The main components of a buck converter are inductor, capacitor, power switches, driver, and control as shown in Figure 1. This particular architecture is prevalent in most battery portable devices in order to efficiently convert the battery voltage into a constant DC supply for the application. The circuit can operate in different conduction modes and control schemes. A summary of these aspects is given in the following subsections.

Figure 1 – Simplified block diagram of a step-down switched-inductor DC-DC converter.

Source: The author.

#### 1.1.1 Conduction modes

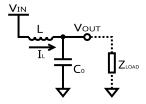

In Continuous Conduction Mode (CCM), the circuit operates in two stages: inductor charge stage and inductor discharge stage. During the inductor charge stage ( $M_P$  is on and  $M_N$  is off as depicted in Figure 2), the surplus energy is stored in the inductor instead of being converted into heat. During the inductor discharge stage (the transistor  $M_P$  is off and  $M_N$  is on as depicted on Figure 3), the energy stored in the inductor is transferred to the load. The converter switches between the two stages cyclically with a period that is called switching period. The inverse of the switching period is the switching frequency of the converter.

Figure 2 – Inductor charge stage.

Source: The author.

Figure 3 – Inductor discharge stage.

Source: The author.

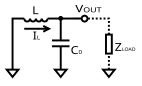

In Discontinuous Conduction Mode (DCM), the operation is similar, but the converter enters a third stage (Figure 4) with both transistor  $M_P$  and  $M_N$  off when the inductor current reaches 0 A.

Figure 4 – Equivalent circuit for null inductor current in DCM.

Source: The author.

#### 1.1.2 Buck control schemes

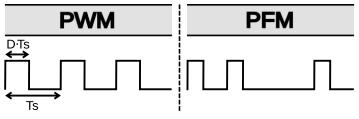

Commonly, a buck can be controlled using Pulse Width Modulation (PWM) or Pulse Frequency Modulation (PFM).

PWM modulation involves the representation of an analog signal with two levels (0 or 1) oscillating at a fixed switching period  $(T_S)$ . The amplitude information of the analog signal is encoded in the duty cycle (D), which represents the ratio between the time the signal remains at one and the switching period. PFM modulation is similar, but the pulse width is usually fixed with a variable switching frequency. Both modulation methods are illustrated in Figure 5.

When employing the PWM modulation method, the control can operate in voltage mode or current mode. In voltage mode, the control relies on the output voltage information to determine the duty cycle. In current mode, the control measures both the output voltage and the inductor current to determine the duty cycle.

Figure 5 – PWM and PFM modes.

Source: The author.

## 1.1.3 Average model with voltage mode control in CCM

In order to control the output voltage with a constant switching frequency, the converter must change the duty cycle, therefore mathematical relations between the duty cycle and the output voltage are important for the correct design of the control loop.

This section provides mathematical models of the DC-DC converter correlating the duty cycle with the output voltage in CCM. Besides, approximate equations for the capacitor voltage ripple and the inductor current ripple are also shown. Most of the models shown in this chapter are based on or inspired by the material available in the book Pulse-Width Modulated DC-DC Power Converters [1].

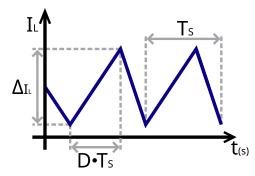

The inductor current in CCM is shown in Figure 6, where  $I_L$  represents the inductor current,  $T_S$  is the switching period, and D is the duty cycle (a real number between 0 and 1).

Figure 6 – Inductor current in continuous conduction mode.

Source: The author.

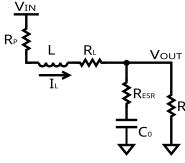

The equivalent circuit of the converter during the inductor charge stage is shown in Figure 7, where  $R_P$  is the resistance of the transistor  $M_P$ , L is the inductance,  $C_0$  is the capacitance,  $R_L$  is the equivalent series resistance of the inductor,  $R_{ESR}$  is the equivalent series resistance of the capacitor,  $V_{IN}$  is the input voltage, and  $V_{OUT}$  is the output voltage.

Figure 7 – Inductor charge stage including parasitic resistances.

Source: The author.

Derivatives of the inductor current and the capacitor voltage for the inductor charge stage are shown below ( $V_{C_0}$  represents the voltage across  $C_0$ ):

$$\frac{dI_L}{dt}_{CHG} = -\frac{I_L}{L} \cdot \left(\frac{R_{ESR} \cdot R}{R_{ESR} + R} + R_P + R_L\right) - \frac{V_{CO}}{L} \cdot \frac{R}{R_{ESR} + R} + \frac{V_{IN}}{L}$$

(1.1)

$$\frac{dV_{C_O}}{dt}_{CHG} = \frac{I_L}{C_O} \cdot \frac{R}{R_{ESR} + R} - \frac{V_{C_O}}{C_O} \cdot \frac{1}{R_{ESR} + R}$$

(1.2)

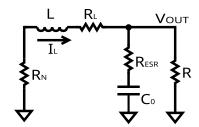

The model of the converter during the inductor discharge stage is shown in Figure 8. All the parameters are identical to the inductor charge stage except for  $R_N$ , which represents the resistance of transistor  $M_N$ .

Figure 8 – Inductor discharge stage including parasitic resistances.

Source: The author.

Derivatives of the inductor current and the capacitor voltage are now equal to:

$$\frac{dI_L}{dt}_{DIS} = -\frac{I_L}{L} \cdot \left(\frac{R_{ESR} \cdot R}{R_{ESR} + R} + R_N + R_L\right) - \frac{V_{CO}}{L} \cdot \frac{R}{R_{ESR} + R} \tag{1.3}$$

$$\frac{dV_{C_O}}{dt}_{DIS} = \frac{I_L}{C_O} \cdot \frac{R}{R_{ESR} + R} - \frac{V_{C_O}}{C_O} \cdot \frac{1}{R_{ESR} + R}$$

(1.4)

The average of the derivative of the inductor current and capacitor voltage within one switching cycle will be equal to:

$$\frac{\overline{dI_L}}{dt} = \frac{1}{T_S} \cdot \left( \int_0^{D \cdot T_S} \frac{dI_L}{dt}_{CHG} dt + \int_{D \cdot T_S}^{T_S} \frac{dI_L}{dt}_{DIS} dt \right)$$

(1.5)

$$\frac{\overline{dV_{C_O}}}{dt} = \frac{1}{T_S} \cdot \left( \int_0^{D \cdot T_S} \frac{dV_{C_O}}{dt} dt + \int_{D \cdot T_S}^{T_S} \frac{dV_{C_O}}{dt} dt \right)$$

(1.6)

$$\frac{\overline{dI_L}}{dt} = -\frac{\overline{I_L}}{L} \cdot \left[ \frac{R_{ESR} \cdot R}{R_{ESR} + R} + R_P \cdot D + R_N \cdot (1 - D) + R_L \right] - \frac{\overline{V_{C_O}}}{L} \cdot \frac{R}{R_{ESR} + R} + D \cdot \frac{V_{IN}}{L}$$

(1.7)

$$\frac{\overline{dV_{C_O}}}{dt} = \frac{\overline{I_L}}{C_O} \cdot \frac{R}{R_{ESR} + R} - \frac{\overline{V_{C_O}}}{C_O} \cdot \frac{1}{R_{ESR} + R}$$

(1.8)

In steady state, the average inductor current and the average capacitor voltage will not change, therefore:

$$\frac{\overline{dV_{C_O}}}{dt} = 0 \implies \overline{V_{C_O}} = R \cdot \overline{I_L}$$

(1.9)

$$\frac{\overline{dI_L}}{dt} = 0 \implies \overline{V_{C_O}} = \frac{D \cdot V_{IN}}{1 + \frac{R_P \cdot D + R_N \cdot (1 - D) + R_L}{R}}$$

(1.10)

Since the average capacitor current must also be 0 in stead state, the average output voltage will be:

$$\overline{V_{OUT}} = \overline{V_{C_O}} \tag{1.11}$$

#### 1.1.3.1 Approximate capacitor voltage ripple and inductor current ripple

Assuming that the parasitic resistances  $R_P$ ,  $R_N$ , and  $R_L$ , are negligible, the inductor current ripple  $(\Delta_{I_L})$  can be calculated as follows:

$$\Delta_{I_L} = \frac{D \cdot T_S \cdot \left(V_{IN} - \overline{V_{OUT}}\right)}{I_L} \tag{1.12}$$

Assuming that  $R_{ESR}$  is also negligible, the output voltage ripple  $(\Delta_{V_{OUT}})$  can be calculated as follows:

$$\Delta_{V_{OUT}} = \frac{\frac{\Delta_{I_L}}{2} \cdot \frac{T_S}{2}}{2 \cdot C_0} = \frac{\Delta_{I_L} \cdot T_S}{8 \cdot C_0}$$

$$\tag{1.13}$$

When  $R_{\rm ESR}$  is large and it dominates the ripple contribution, the output voltage ripple is:

$$\Delta_{V_{OUT}} = \Delta_{I_L} \cdot R_{ESR} \tag{1.14}$$

An upper bound for the output voltage ripple can be established as:

$$max\left(\Delta_{V_{OUT}}\right) < \frac{\Delta_{I_L} \cdot T_S}{8 \cdot C_0} + \Delta_{I_L} \cdot R_{ESR} \tag{1.15}$$

#### 1.1.3.2 Continuous time small signal model

The small signal equations can be obtained by analyzing the sensitivity of Equations 1.7 and 1.8 to small variations in the duty cycle and the input voltage.

In what follows, small signal variations were changed to lowercase and dependencies on large signals were kept in uppercase.

$$\frac{\overline{di_L}}{dt} = -\frac{\overline{i_L}}{L} \cdot \left[ \frac{R_{ESR} \cdot R}{R_{ESR} + R} + R_P \cdot D + R_N \cdot (1 - D) + R_L \right]

- \frac{\overline{v_{C_O}}}{L} \cdot \frac{R}{R_{ESR} + R}

- \frac{\overline{I_L}}{L} \cdot d \cdot (R_P - R_N) + d \cdot \frac{V_{IN}}{L}

+ \frac{v_{in}}{L} \cdot D$$

(1.16)

$$\frac{\overline{dv_{C_O}}}{dt} = \frac{\overline{i_L}}{C_O} \cdot \frac{R}{R_{ESR} + R} - \frac{\overline{v_{C_O}}}{C_O} \cdot \frac{1}{R_{ESR} + R}$$

(1.17)

Using the space state representation:

$$\frac{dx}{dt} = A \cdot x + B \cdot u \tag{1.18}$$

$$\overline{v_{out}} = C \cdot x + D \cdot u \tag{1.19}$$

In this case, x,  $i_L$ , A, B, C, D and u are equal to:

$$x = \begin{bmatrix} \overline{i_L} \\ \overline{v_{C_O}} \end{bmatrix} \tag{1.20}$$

$$u = \begin{bmatrix} d \\ v_{in} \end{bmatrix} \tag{1.21}$$

$$A = \begin{bmatrix} -\frac{\frac{R_{ESR} \cdot R}{R_{ESR} + R} + R_P \cdot D + R_N \cdot (1 - D) + R_L}{L} & -\frac{R}{L \cdot (R_{ESR} + R)} \\ \frac{R}{C_O \cdot (R_{ESR} + R)} & -\frac{1}{C_O \cdot (R_{ESR} + R)} \end{bmatrix}$$

(1.22)

$$B = \begin{bmatrix} \frac{V_{IN} \cdot (R + R_N + R_L)}{L \cdot [R + R_P \cdot D + R_N \cdot (1 - D) + R_L]} & \frac{D}{L} \\ 0 & 0 \end{bmatrix}$$

(1.23)

$$C = \begin{bmatrix} \frac{R_{ESR} \cdot R}{R_{ESR} + R} & \frac{R}{R_{ESR} + R} \end{bmatrix}$$

(1.24)

$$D = \begin{bmatrix} 0 & 0 \end{bmatrix} \tag{1.25}$$

The transfer functions  $H(s) = \frac{\overline{v_{out}(s)}}{d(s)}$  and  $F(s) = \frac{\overline{v_{out}(s)}}{v_{in}(s)}$  can be calculated as follows (*I* is the identity matrix):

$$[H(s) \ F(s)] = C(sI - A)^{-1}B + D$$

(1.26)

Therefore:

$$H(s) = G_H \cdot \frac{1 - \frac{s}{z_1}}{\left(1 - \frac{s}{p_1}\right) \cdot \left(1 - \frac{s}{p_2}\right)}$$

(1.27)

$$F(s) = G_F \cdot \frac{1 - \frac{s}{z_1}}{\left(1 - \frac{s}{p_1}\right) \cdot \left(1 - \frac{s}{p_2}\right)}$$

(1.28)

$G_H$ ,  $G_F$ ,  $z_1$ ,  $p_1$  and  $p_2$  are equal to:

$$G_H = \frac{V_{IN} \cdot R \cdot (R_L + R + R_N)}{(R + R_S)^2}$$

(1.29)

$$G_F = \frac{D \cdot R}{(R + R_S)} \tag{1.30}$$

$$z_1 = -\frac{1}{C_O \cdot R_{ESR}} \tag{1.31}$$

$$p_1 = -\frac{b + j \cdot \sqrt{4 \cdot a - b^2}}{2 \cdot a} \tag{1.32}$$

$$p_2 = -\frac{b - j \cdot \sqrt{4 \cdot a - b^2}}{2 \cdot a} \tag{1.33}$$

, in which:

$$a = \frac{C_O \cdot (R_{ESR} + R) \cdot L}{(R + R_S)} \tag{1.34}$$

$$b = \frac{C_O \cdot (R_{ESR} + R) \cdot \left(\frac{R_{ESR} \cdot R}{R_{ESR} + R} + R_S\right) + L}{(R + R_S)}$$

$$(1.35)$$

$$R_S = R_P \cdot D + R_N \cdot (1 - D) + R_L \tag{1.36}$$

#### 1.1.3.3 Discrete time small signal model

The derivation of the discrete-time small-signal model is complex. Various works addressing this topic have been documented, with a precise model for the entire frequency range presented in [2]. This model assumes that the sampling occurs in fixed intervals and includes the delay between the sampling event and the trailing edge of the PWM signal.

When the ADC operates by averaging within an interval, as proposed in [3], obtaining a model becomes even more challenging. However, if the control loop's bandwidth is significantly lower than the sampling frequency, the discretization of the average model offers a first approximation. This involves multiplying Equation 1.27 by the transfer function of the Zero-Order Hold (ZOH), followed by decomposition into partial fractions. Each term is then converted to discrete time as shown in [4]. The result of this process is presented below:

$$\frac{H(z)}{G_H} = 1 + \frac{p2}{p1 - p2} \cdot \left(1 - \frac{p1}{z1}\right) \cdot \frac{z - 1}{z - e^{p1 \cdot Ts}} + \frac{p1}{p2 - p1} \cdot \left(1 - \frac{p2}{z1}\right) \cdot \frac{z - 1}{z - e^{p2 \cdot Ts}} \tag{1.37}$$

The analytical analysis presented in this chapter will be used in Chapter 2.

#### 1.1.4 Control loop performance measurements

Since the buck works in closed loop, it is important to list the basic control loop performance parameters. Some of them are:

- Line over/undershoot: This parameter is measured by rapidly increasing or decreasing the input voltage, followed by recording the maximum deviation between the steady state and transient output voltage levels.

- Load over/undershoot: This parameter is measured by rapidly increasing or decreasing the load current, followed by recording the maximum deviation between the steady state and transient output voltage levels.

- Voltage reference step response: A step in the voltage reference is induced, and the output voltage is characterized in terms of rise time  $t_r$ , settling time  $t_s$ , and overshoot M[5].

- Phase Margin (PM): In a negative feedback loop, the amount by which the phase of open loop frequency response exceeds -180° when the gain is equal to 0 dB [5].

- Gain Margin (GM): In a negative feedback loop, the gain margin is the amount by which the open loop gain can to be increased so the phase is greater than -180° [5].

## 1.1.5 Basic ADC performance measurements

A digital buck will probably require an ADC in order to digitize the output voltage, therefore is is important to establish some basic performance parameters for the ADC. According to [6] the main basic parameters are:

- Resolution: The number of bits in the digital code

- Accuracy: The closeness of the digital code to the actual analog input value, often expressed as a percentage of the full-scale range. In the case of the differential window ADC proposed in this work, the control loop will try to keep the difference between the output voltage and the voltage reference as low as possible. Therefore, the accuracy measurement is more relevant for the code that represents 0 V.

- Step Size: The analog voltage difference between two consecutive digital codes.

- Linearity: The degree of linearity in the relationship between analog input and digital output is crucial for the performance of an ADC. Non-linearity is commonly assessed through two metrics: Differential Non-Linearity (DNL) and Integral Non-Linearity (INL). These metrics are defined by Equations 1.38 and 1.39, respectively [7]. In these equations,  $V_i$  represents the input voltage corresponding to the code i, N denotes the resolution of the ADC, and  $Q_{ADC}$  denotes the ideal step size.

$$DNL(i) = \frac{V_{i+1} - V_i}{Q_{ADC}} - 1, \text{ where } 0 < i < 2^N - 2$$

(1.38)

$$INL(i) = \frac{V_i - V_0}{Q_{ADC}} - i, \text{ where } 0 < i < 2^N - 1$$

(1.39)

- Sampling Rate: The rate at which the ADC samples the analog input signal, typically measured in Samples Per Second (SPS).

- DC current: The current trough the ADC supply during operation.

# 1.2 Summary of previous research on integrated digitally controlled DC-DC converters

There are several works available on the subject of integrated digitally controlled DC-DC converters. The following subsections aim to provide the review of a few articles which represent some relevant techniques available at the time of this writing.

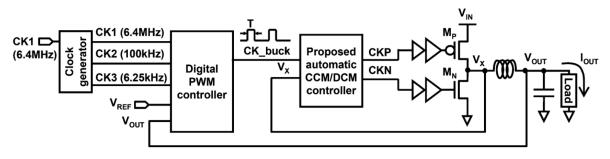

# 1.2.1 A 0.6 V Input CCM/DCM Operating Digital Buck Converter in 40 nm CMOS

ZHANG et al. [8] designed a 0.6 V Input DC-DC converter for photovoltaic applications. The converter has a digital control loop and automatic switching between continuous and discontinuous operating mode to ensure low power consumption. The top level block diagram and the control loop block diagram are shown in Figures 9 and 10, respectively.

Figure 9 – Block diagram of the converter [8].

Source: ZHANG et al. [8].

Figure 10 – Block diagram of the PWM controller [8].

Source: ZHANG et al. [8].

A clock signal of 6.4 MHz (CK1) controls a chain of 64 shift registers in which a reset pulse moves from the beginning to the end of the chain once every 10 µs. The division of CK1 by 64 generates another clock pulse (CK2) which generates a set pulse also once every 10 µs. A third division of CK2 by 16 (CK3) controls a bidirectional shift register. If the output voltage is lower than the reference, the bi-directional register will shift right. If the output voltage is higher than the average, the bidirectional shift register will shift left.

The set signal together with the reset signal selected by the bidirectional shift register are connected to a Set-Reset (SR) flip-flop, which generates a 100 kHz PWM signal with a duty cycle resolution of 1,5625% (64 steps). The duty cycle is updated with a frequency of 6.25 kHz. Check the timing diagram (Figure 11) for more information.

Figure 11 – Timing diagram [8].

Source: ZHANG et al. [8].

A summary of the main parameters is available in Table 1. Although the specification of a DC-DC converter designed for photovoltaic applications cannot be compared with the specification of a DC-DC converter designed for generic battery powered applications, the PWM control technique with only one comparator between the input voltage and the reference voltage worth some consideration.

| Parameter           | Minimum | Typical    | Maximum |

|---------------------|---------|------------|---------|

| Process             | -       | CMOS 40 nm | -       |

| Input voltage       | 0.6 V   | -          | 1.1 V   |

| Output voltage      | 0.3 V   | -          | 0.55 V  |

| Output current      | 50 μΑ   | -          | 10 mA   |

| Inductor            | -       | 220 μH     | -       |

| Capacitor           | -       | 167 nF     | -       |

| Efficiency          | -       | -          | 94%     |

| Switching frequency | -       | 100 kHz    | -       |

| System clock        | -       | 6.4 MHz    | -       |

| DPWM step           | -       | 1.5625%    | -       |

Table 1 – Summary of the main parameters in [8].

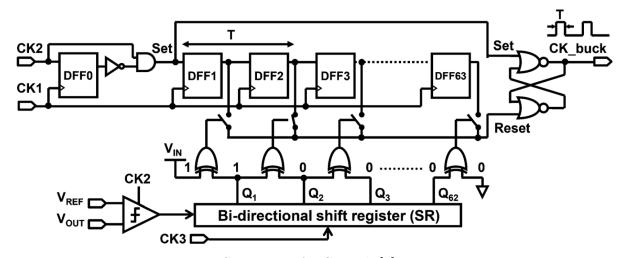

# 1.2.2 A 65 nm, 1 A Buck Converter With Multi-Function SAR-ADC-Based CCM/PSK Digital Control Loop

A 1 A DC-DC converter with embedded digital control implemented in 65 nm CMOS technology was developed by Sébastien Cliquennois et al. [9]. The proposed DC-DC converter has a multi-function Successive Approximation Register (SAR) ADC and a non-linear PID controller. It can also switch automatically between continuous conduction mode and pulse-skipping mode to achieve better efficiency over the load current range. The block diagram is shown in Figure 12.

$V_{BAT}$ IC CCM  $V_{OUT}$ PWM RLOAD TOOUT  $V_{BAT}$ PID SAR **DPWM ADC** Φ-Gen D<sub>BAT</sub> Filter Φ<sub>ADC</sub> MCK FSM V<sub>LX</sub> Sense  $\ll V_{LX}$ PSK

Figure 12 – Simplified block diagram of the DC-DC converter proposed in [9].

Source: Sébastien Cliquennois et al. [9].

A 7-bit SAR ADC is used in time-sharing to digitize both  $V_{OUT}$  with a sampling frequency of 6.4 MHz and  $V_{BAT}$  with a sampling frequency of 0.8 MHz. In continuous mode, the digitized  $V_{OUT}$  and  $V_{BAT}$  are fed to a digital controller, whose block diagram is shown in Figure 13.

The DPWM works based on a ripple counter operated at 307.2 MHz to provide a 48 level PWM. The transition between continuous conduction mode and the pulse skipping mode as well as the operation of the pulse skipping mode are not relevant in the context of this work, because of the focus on the control for fixed frequency operation.

Figure 13 – Block diagram of the digital controller [9].

Source: Sébastien Cliquennois et al. [9].

A summary of the main parameters can be found in Table 2.

| Parameter                        | Minimum | Typical              | Maximum |

|----------------------------------|---------|----------------------|---------|

| Process                          | -       | CMOS 65 nm           | -       |

| Input voltage                    | 2.3 V   | -                    | 4.8 V   |

| Output voltage                   | 0.6 V   | -                    | 1.35 V  |

| Output current                   | 0 A     | -                    | 1 A     |

| Inductor                         | -       | 470 nH               | -       |

| Load Capacitance                 | -       | 10 μF                | -       |

| Line Transient (600mV in 10 µs)  | -       | 10 mV                | -       |

| Load Transient (200mA in 500 ns) | -       | 20 mV                | -       |

| Efficiency                       | -       | -                    | 85%     |

| Switching frequency              | -       | 6.4 MHz              | -       |

| SAR clock frequency              | -       | 153.6 MHz            | -       |

| DPWM clock frequency             | -       | 307.2 MHz            | -       |

| Output ripple                    | -       | -                    | 10 mV   |

| ADC step                         | -       | 10 mV                | -       |

| DPWM step                        | -       | 2.083%               | -       |

| Active area                      |         | $0.038 \text{ mm}^2$ |         |

| without power transistors        | _       | 0.036 11111          | _       |

| Current consumption              |         | 115.5 μΑ             |         |

| without power transistors        | _       | 115.5 μΑ             | _       |

| Current consumption (ADC)        | -       | 18 μΑ                | -       |

| Current consumption (DPWM)       | -       | 82.5 μA              | -       |

| Current consumption (PID)        | -       | 15 μΑ                | -       |

Table 2 – Summary of the main parameters in [9].

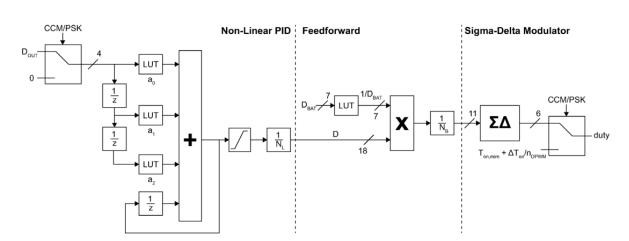

# 1.2.3 A 4 μA Quiescent-Current Dual-Mode Digitally Controlled Buck Converter IC for Cellular Phone Applications

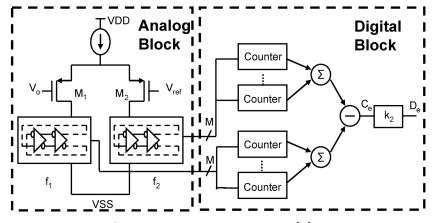

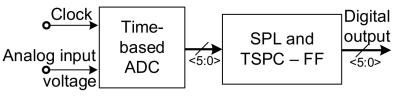

The DC-DC converter developed by Jinwen Xiao et al. [3] minimizes quiescent current by switching automatically between PFM and PWM. The block diagram can be visualized in Figure 14. In PWM mode, a ring ADC topology (Figure 15) digitizes the difference between the output voltage and the reference voltage which is then applied to a PID controller. The output of the PID controller is then connected to a DPWM converter (Figure 16).

The ADC has two ring oscillators operating in sub-threshold voltage biased by a differential pair. Every tap of the ring oscillator is connected to counters re-started at the beginning of the switching cycle, this structure averages and digitizes the difference between the output voltage and the reference voltage (Figure 15).

The implementation of the DPWM consists in a ring-oscillator-Multiplexer (MUX) topology (Figure 16) and latches. The set signal of the PWM will be generated when the square wave that propagates through the ring reaches the tap selected by the MUX.

The reset signal is generated when the square wave reaches a predefined tap of the ring oscillator.

Figure 14 – Architecture proposed by Jinwen Xiao et al. [3].

Source: Jinwen Xiao et al. [3].

Figure 15 – Ring ADC proposed by Jinwen Xiao et al. [3].

Source: Jinwen Xiao et al. [3].

Figure 16 – DPWM proposed by Jinwen Xiao et al. [3].

Source: Jinwen Xiao et al. [3].

Table 3 – Summary of the main parameters in [3].

A summary of the main parameters can be found in Table 3.

| Parameter                  | Minimum            | Typical              | Maximum   |

|----------------------------|--------------------|----------------------|-----------|

| Process                    | -                  | CMOS 0.25 μm         | -         |

| Input voltage              | 2.8 V              | -                    | 5.5 V     |

| Output voltage             | 1.0 V              | -                    | 1.8 V     |

| Output current             | 100 μΑ             | -                    | 400 mA    |

| Inductor                   | -                  | 10 μH                | -         |

| Load Capacitance           | -                  | 47 μF                | -         |

| Load Transient (50-150 mA) |                    | 25  mV               | -         |

| Switching frequency (PWM)  | $0.5~\mathrm{MHz}$ | -                    | 1.5 MHz   |

| Output ripple (PWM)        | -                  | 2  mV                | -         |

| Efficiency                 | -                  | -                    | above 90% |

| ADC step                   | -                  | 16 mV                | -         |

| DPWM step                  | -                  | 3.2%                 | -         |

| Active area                | -                  | $2 \text{ mm}^2$     | -         |

| Active area (ADC+DPWM+PID) | -                  | $0.23~\mathrm{mm}^2$ | -         |

| Current consumption (ADC)  | -                  | 37 μA                | -         |

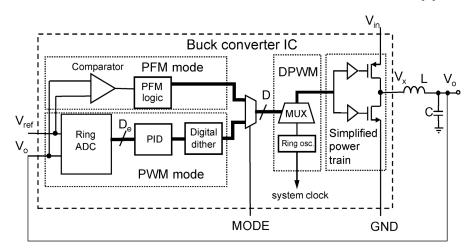

# 1.2.4 20 $\mu A$ to 100 mA DC-DC Converter With 2.8-4.2 V Battery Supply for Portable Applications in 45 nm CMOS

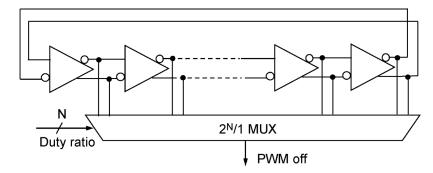

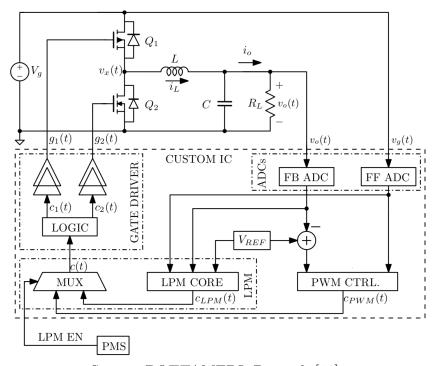

Saurav et al. [10] designed a DC-DC converter for portable applications capable of delivering currents from 20  $\mu A$  to 100 mA. The converter operates in two modes (PWM and PFM) and it can be supplied with a Li-ion battery (2.8 V - 4.2 V).

The general architecture is depicted in Figure 17. In PWM mode, the error between the reference voltage and the output voltage is converted to digital by a 4-bit flash ADC.

PWM Logic

1.2V

vref\_digital\_pwm

vref\_digital\_

Figure 17 – Architecture proposed by Saurav et al. [10].

Source: Saurav et al. [10].

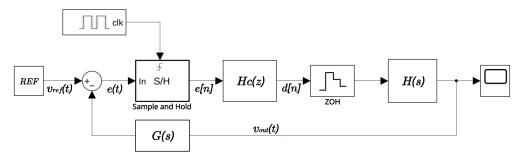

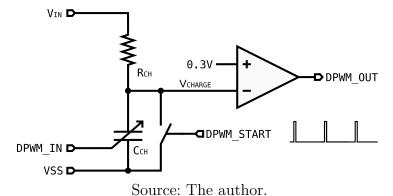

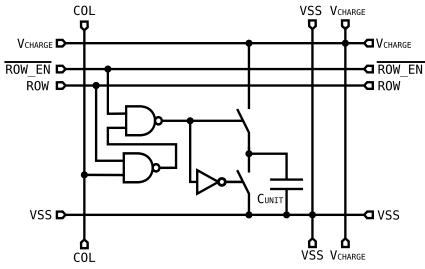

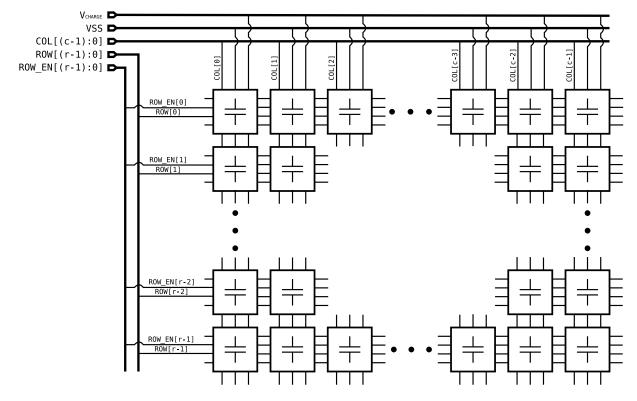

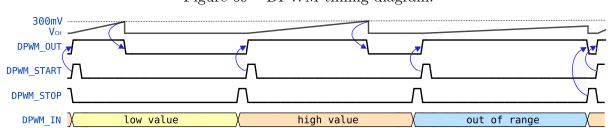

The digital representation of the error is then fed to the PID controller which in turn generates the input of the DPWM (Figure 18) which is based on a network of capacitors with values in powers of 2. By changing the total capacitance connected to  $V_{\rm CHARGE}$ , the PID controller can vary the duty cycle of the PWM signal.

Figure 18 – Digital to Pulse Width Modulation proposed by Saurav et al. [10].

A summary of the main parameters can be found in Table 4.

Table 4 – Summary of the main parameters in [10].

| Parameter                  | Minimum | Typical              | Maximum |

|----------------------------|---------|----------------------|---------|

| Process                    | -       | CMOS 45 nm           | -       |

| Input voltage              | 2.8 V   | -                    | 4.2 V   |

| Output voltage             | 0.4 V   | -                    | 1.2 V   |

| Output current             | 20 μΑ   | -                    | 100 mA  |

| Inductor                   | -       | 10 μΗ                | -       |

| Load Capacitance           | -       | 2 μF                 | -       |

| Load Transient             |         | 10 mV                |         |

| (10–50 mA in 25 μs)        | _       | 10 1111              | _       |

| Switching frequency (PWM)  | -       | 2 MHz                | -       |

| Efficiency                 | -       | -                    | 87.2%   |

| ADC step                   | -       | 50 mV                | -       |

| DPWM step                  | -       | 1%                   | -       |

| Active area (ADC+DPWM+PID) | -       | $0.07~\mathrm{mm^2}$ | -       |

| Current consumption (DPWM) | -       | approximately 6 μA   | -       |

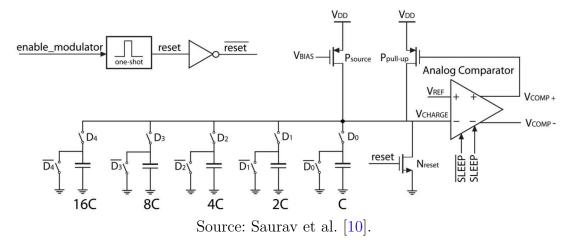

# 1.2.5 A 180 nA Quiescent Current Digital Control Dual-Mode Buck Converter With a Pulse-Skipping Load Detector for Long-Range Applications

TSAI, T.-H. et al. [11] suggest a DC-DC converter that operates in DCM with automatic switching between Pulse-Skipping Adaptive On-Time (PSAOT), and Pulse-Skipping Asynchronous Mode (PSAM). The block diagram is shown in Figure 19.

The PSAM mode has a low Quiescent Current (IQ) and is suitable for low currents. In this mode, the PSAM circuitry will turn on the PMOS switch (with a fixed on-time) if the output voltage is lower than the voltage reference. The clock frequency of the PSAM can be configured in order to further decrease IQ at a cost of a slower transient response.

On the other hand, the PSAOT mode has a higher IQ and is suitable for high currents. In this mode, the PSAOT circuitry also turns on the PMOS switch if the output voltage is lower than the voltage reference, but, differently from the PSAM mode, the PSAOT circuitry adjusts the PMOS on-time according to the load.

The comparison between the voltage reference and the output voltage is carried out by a clocked comparator and the load estimation is done by a digital circuit that counts the number of clock cycles between two high logic levels in the output of the comparator.

Figure 19 – Architecture proposed by TSAI, T.-H. et al. [11].

Source: TSAI, T.-H. et al. [11].

A summary of the main parameters can be found in Table 5.

| Parameter              | Minimum | Typical              | Maximum |

|------------------------|---------|----------------------|---------|

| Process                | -       | CMOS 350 nm          | -       |

| Input voltage          | 4.2 V   | -                    | 5.0 V   |

| Output voltage         | -       | 3.3 V                | -       |

| Output current         | 0 A     | -                    | 100 mA  |

| Inductor               | -       | 4.7 μΗ               | -       |

| Load Capacitance       | -       | 10 μF                | -       |

| Output Ripple at 10 mA | -       | 16 mV                | -       |

| Efficiency             | -       | -                    | 92.9%   |

| Switching Frequency    | -       | -                    | 500 kHz |

| Active area            | -       | $3.78~\mathrm{mm}^2$ | -       |

Table 5 – Summary of the main parameters in [11].

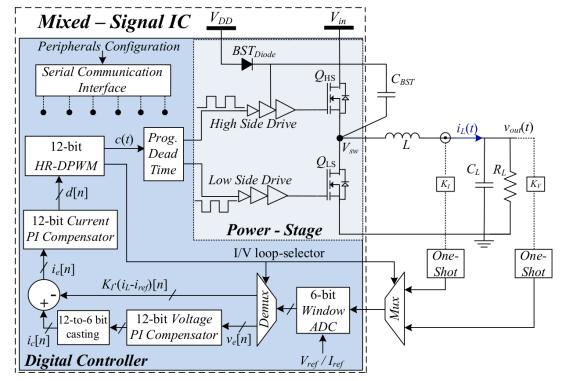

## 1.2.6 A Digital Controller IC for High-Frequency DC-DC Switching Converters

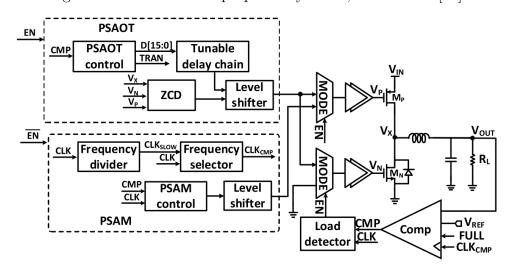

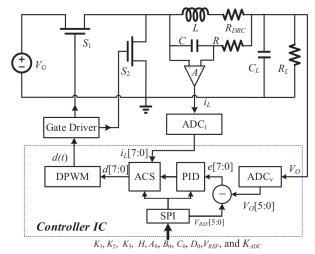

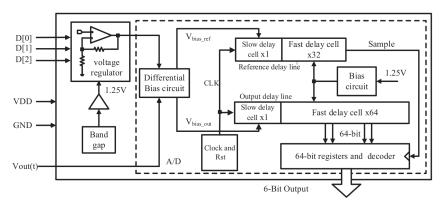

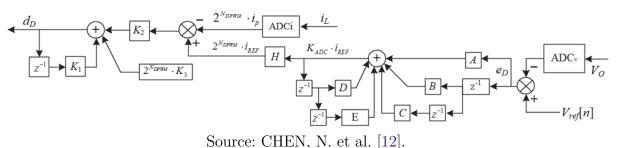

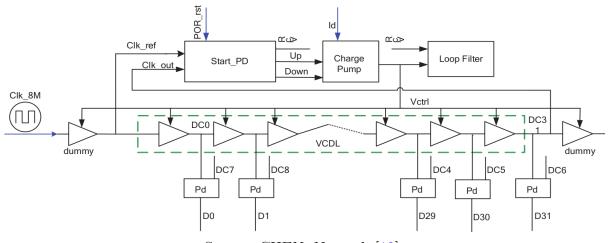

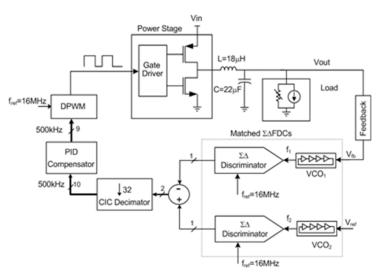

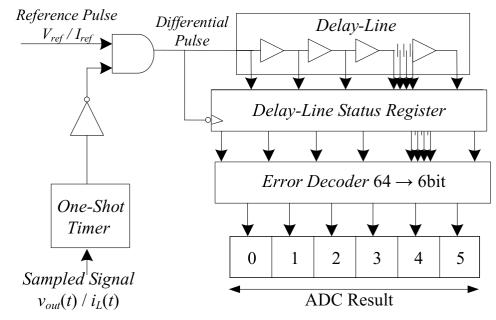

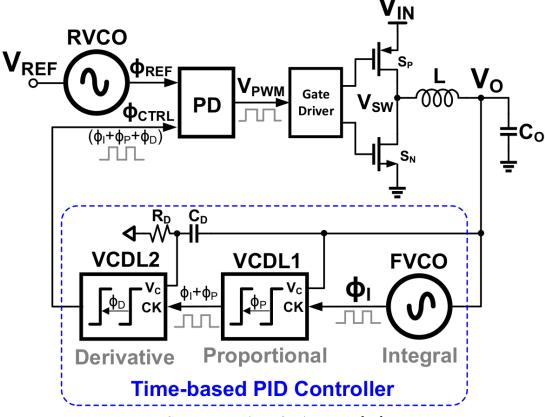

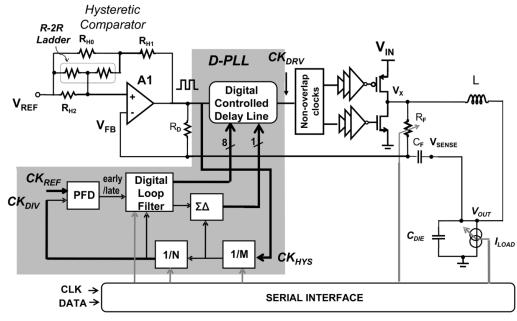

The architecture of the digital controller proposed by CHEN, N. et al. (Figure 20) consists of a delay line ADC (Figure 21), a current mode digital control (Figure 22), and a Phase-Locked Loop (PLL) based DPWM (Figure 23).

There are two ADCs. The first one is based on two delay lines with bias currents proportional to the difference between the output voltage and the voltage reference. One of the delay lines is connected to the input of a 64-bit register and the last inverter of the second delay line works like a clock for the same register. Consequently, this configuration generates a thermometer code with 64 levels that represents the difference between the voltage reference and the output voltage (Figure 21). The second ADC is external to the controller Integrated Circuit (IC) and its architecture is not mentioned, but it measures the inductor current in the end of the cycle so the digital logic can calculate the duty cycle for the next cycle.

Figure 20 – Architecture proposed by CHEN, N. et al. [12].

Source: CHEN, N. et al. [12].

Figure 21 – ADC proposed by CHEN, N. et al. [12].

Source: CHEN, N. et al. [12].

The digital control has one loop to control the inductor current and another loop to control the output voltage. This configuration has the advantage of eliminating the imaginary poles of the converter, but it requires an extra ADC to measure the inductor current.

Figure 22 – Control proposed by CHEN, N. et al. [12].

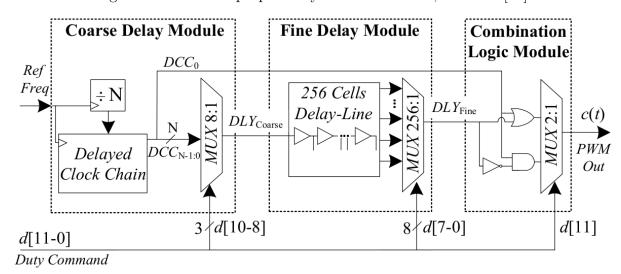

The DPWM is implemented through a combination of a 8 MHz clock, a 3-bit counter, and a voltage controlled delay line with 32 stages. If the frequency of the delay line is not equal to the 8 MHz clock, a phase discriminator and charge pump will vary the supply of the delay line until synchronization is achieved. Hence, a 1 MHz DPWM with 7-bit (3-bit from the counter and 5-bit from the delay line) is built from this combination.